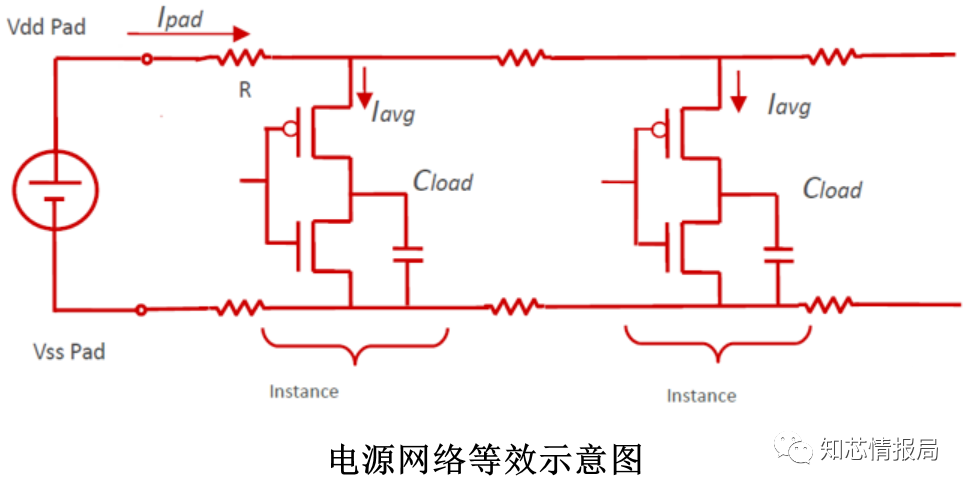

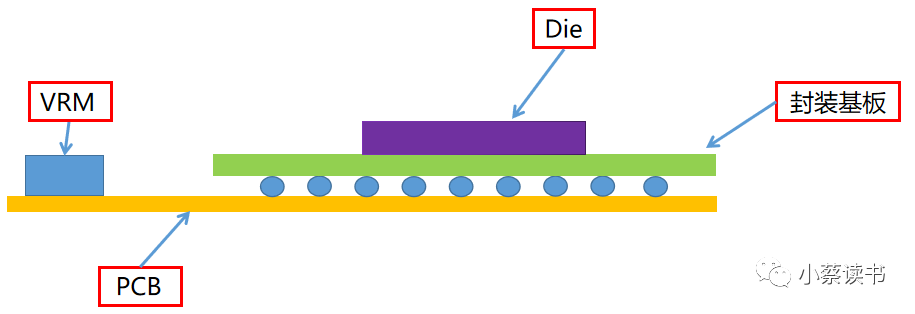

IR Drop仿真是一個系統層面的問題,需要考慮完整的Power Distribution System(PDS)鏈路上所有壓降,并以此來優化每顆器件所接收到的供電電壓。

在設計設計中所有的電源供電芯片在相應的設計下都有一個標稱的輸出電壓與電壓波動范圍(可能是由于芯片本身或所用分壓電阻誤差造成)。每顆SINK芯片也有標稱的正常工作的電壓與上下容限范圍。我們需要根據這些給定條件結合PowerDC仿真結果來判斷PDS設計是否符合要求。

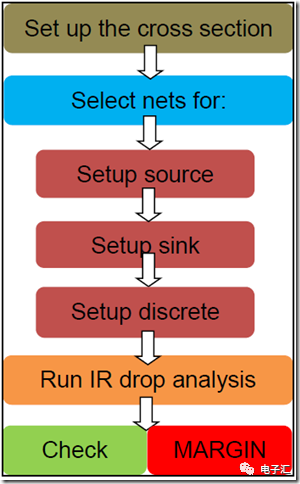

典型的PowerDC仿真流程:

案例1:實際電壓低于正常額定電壓

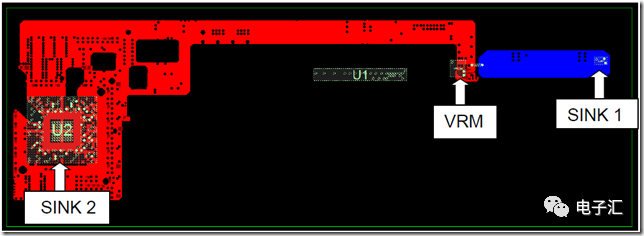

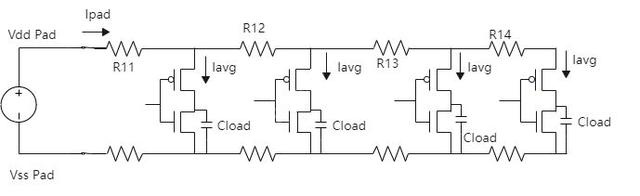

如下圖所示的一個PCB板,一個VRM同時給兩個SINK供電,SINK1通過一個被動元件(如磁珠或電阻等)與VRM連接,SINK2直接通過PCB敷銅與VRM連接。假設VRM輸出電壓為1.5V,輸出容限為0%,SINK1和SINK2額定供電電壓為1.5V, 容限為1%,供電電流分別為5A和0.2A。

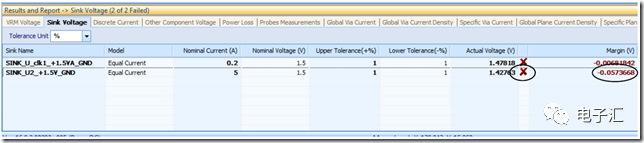

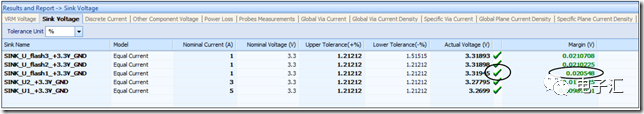

PowerDC的仿真結果如下圖所示,SINK1和SINK2結果都為FAIL。那么PowerDC軟件是如何計算Margin值的呢?

當實際電壓低于正常額定電壓時,Margin通過下面公式計算:

Margin = (Actual voltage + SinkLowerTolerance) – (Normal voltage + VRMoutputTolerance)

因此以U2為例計算得到U2的Margin為:

U2_margin = [1.42763 + (1.5 * 1%)] – [1.5 + (1.5*0%)]

= 1.44263 – 1.5 = –0.05737V

當Margin為負時則說明IR Drop仿真結果Fail, 在PowerDC報告中會出現一個紅色的叉叉。

案例2:實際電壓高于正常額定電壓

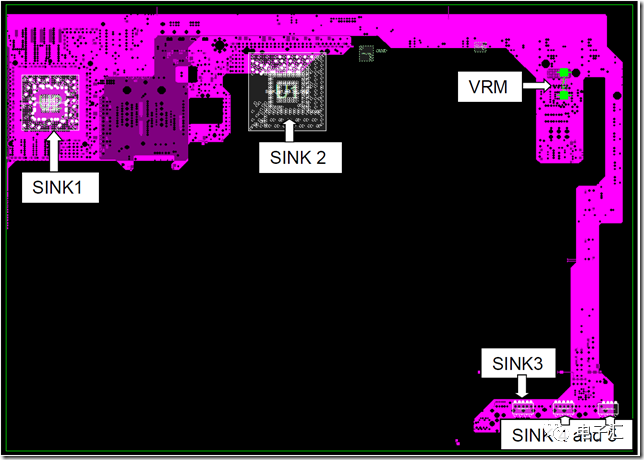

假設有一個PCB設計如下圖所示, 包含一個VRM和4個SINK芯片,VRM與SINK的設計參數見下圖仿真結果表格所設。

PowerDC最終的仿真結果顯示所有SINK的IR Drop仿真結果都PASS,那這些Margin值又是如何計算出來的呢?

當實際電壓高于正常額定電壓時,Margin通過下面公式計算:

Margin = (Normal voltage + SinkUpperTolerance) – (Actual voltage + VRMoutputTolerance)

因此以SINK_U_flash1為例計算得到SINK_U_flash1的Margin為:

SINK_U_flash1_margin = [3.3 + (3.3 * 1.2121%)] – [3.31945 + (3.3*0%)]

= 3.33999996 – 3.31945 = 0.020548V

當Margin為負時則說明IR Drop仿真結果Pass, 在PowerDC報告中會出現一個綠色的勾。

審核編輯:湯梓紅

-

PCB板

+關注

關注

27文章

1450瀏覽量

51955 -

仿真

+關注

關注

50文章

4124瀏覽量

133993 -

PCB設計

+關注

關注

394文章

4701瀏覽量

86349 -

DC

+關注

關注

9文章

3658瀏覽量

680037 -

電源供電

+關注

關注

0文章

157瀏覽量

22158

原文標題:Sigrity PowerDC是如何計算IR Drop Margin?

文章出處:【微信號:電子匯,微信公眾號:電子匯】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

談談芯片設計中的IR-drop

什么是DC IR Drop?DC IR Drop仿真有何意義?

什么是ADM (Add/Drop Multiplexer)

Cadence Sigrity PowerDC應用程序的用戶手冊資料免費下載

PowerDC直流仿真操作說明詳細概述

電源完整性之Cadence Sigrity Power DC_IR_Drop仿真

IR Drop對芯片性能及功能的影響

IR Drop與封裝分析

IR Drop對芯片性能及功能的影響

IR Drop與封裝(一)

技術資訊 | PowerDC直流壓降分析

2022 Sigrity Aurora SPB 17.4 版本更新 I IR Drop 直流電壓降仿真支持自動剪切功能

Sigrity PowerDC是如何計算IR Drop Margin?

Sigrity PowerDC是如何計算IR Drop Margin?

評論