單光子探測器是一種可檢測單個光子能量的高靈敏度器件。按工作原理不同,單光子探測器可分為光電倍增管(PMT)、超導單光子探測器(SSPD)和單光子雪崩光電二極管(SPAD)。

SPAD是一類利用半導體材料內部載流子的雪崩倍增效應實現高靈敏度探測的光電器件,工作在蓋革模式,其工作電壓高于擊穿電壓,內部增益可達到10?~10?,可進行單光子級信號探測。目前,技術相對成熟的是Si材料SPAD和InGaAs材料SPAD。InGaAs材料SPAD在0.9~1.7 μm光譜范圍內有高量子效率,是1.06、1.55 μm主動激光探測的理想探測器。

InGaAs單光子雪崩焦平面基于陣列化技術,將高效率InGaAs SPAD陣列芯片與CMOS計時/計數讀出電路芯片集成封裝,可對光子信號進行時間量化,具有高靈敏、高精度、小體積、全固態的特點,在激光三維成像、遠距離激光通信、稀疏光子探測等領域應用廣泛,是近年來單光子探測領域的研究。

據麥姆斯咨詢報道,近期,重慶光電技術研究所與量子通信核心光電器件重慶重點實驗室的聯合科研團隊在《紅外與激光工程》期刊上發表了以“InGaAs單光子雪崩焦平面研究進展(特邀)”為主題的文章。該文章第一作者和通訊作者為崔大健正高級工程師,主要從事InGaAs單光子雪崩焦平面技術研究及產品開發方面的研究工作。

文中首先介紹了InGaAs單光子雪崩焦平面的結構及基本原理,結合筆者單位工作回顧了國內外單光子雪崩焦平面技術的研究進展,并對未來技術發展進行了討論和展望。

InGaAs單光子雪崩焦平面結構及基本原理

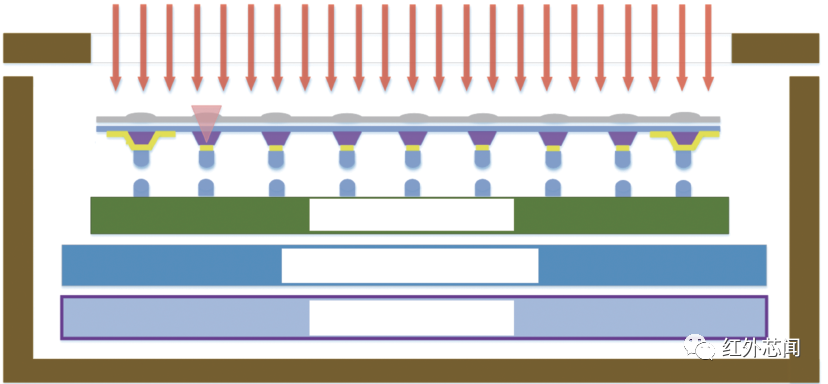

InGaAs單光子雪崩焦平面通常采用PGA封裝(PGA),結構示意圖如圖1所示。InGaAs SPAD陣列芯片和CMOS讀出電路經銦柱倒裝互連,并與微透鏡進行耦合。芯片貼裝在陶瓷基板上,TEC制冷器(TEC)對芯片進行制冷,降低芯片溫度。管殼與陣列芯片通過金絲進行電連接。入射光子經芯片匯聚到吸收層有源區,被吸收后轉化成電子-空穴對,載流子在內部電場作用下遷移到倍增層。

由于InGaAs SPAD陣列芯片工作在擊穿電壓之上的過偏壓蓋革模式下,倍增層高電場促使載流子在倍增層迅速碰撞離化引發雪崩,產生宏觀電流并傳輸到CMOS讀出電路。CMOS讀出電路提供像素級電接口,對單像素產生的雪崩電流進行檢測并淬滅,輸出經時間量化的信號。微透鏡通過高精度對準連接到背照式SPAD陣列芯片,確保高填充因子。InGaAs單光子雪崩焦平面的核心是SPAD陣列芯片和CMOS讀出電路芯片,直接決定了器件的性能。

圖1 InGaAs單光子雪崩焦平面結構示意圖

SPAD陣列芯片

InGaAs SPAD陣列芯片的縱向器件結構通常采用的是吸收層、能帶漸變層、電場控制層和雪崩倍增層分離的SAGCM外延結構,可以在InP襯底之上依次順序(頂部為P型接觸層的P-i-N結構)或者逆序排列(頂部為N型接觸層的N-i-P結構)。各功能層作用如下:

(1)吸收層根據入射光的工作波長,InGaAs材料的禁帶寬度為0.74 eV,長波截止吸收波長為1.7 μm。

(2)電場控制層用于調控縱向電場分布,通過提高倍增層電場促進雪崩碰撞離化,抑制吸收層電場降低隧穿概率。通常電荷濃度越高,倍增層與吸收層電場差異越大;

(3)過渡層主要是降低吸收層載流子向倍增層渡越的價帶勢壘,消除異質界面結空穴積累效應;

(4)倍增層使得載流子在其中發生雪崩碰撞離化從而實現高增益,采用的InP(Eg~1.35 eV)材料,倍增層厚度一般在0.8~1.4 μm。

InGaAs SPAD陣列芯片的橫向器件結構主要分為平面型和臺面型兩種。

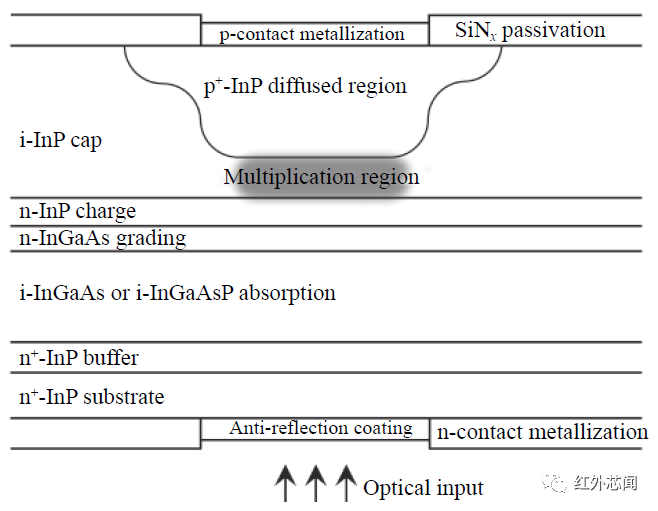

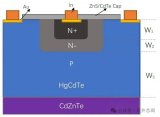

(1)平面型SPAD器件結構通常采用掩埋P-N結,通過光刻SiNx介質膜圖形來確定Zn摻雜的擴散區域以及有源區,并使用兩次擴散來調整P-N結輪廓,以使結在有源區的中心部分比在結外圍更深,這種設計確保了有源區中心部分的增益分布是均勻的,且高于邊緣外圍區域增益,確保邊緣擊穿抑制、低暗電流(<1 nA)和高可靠性。在陣列像元間刻蝕了深度達到緩沖層的隔離槽,一方面防止像素陣列間二次電致光子的光學串擾,另一方面阻斷吸收層載流子橫向的電學串擾。平面結構還包括了與像元有源區中心對準的正面In柱和背面增透膜,分別用于CMOS讀出電路倒裝互連和探測器芯片背照進光。倍增層需使用擴散及摻雜工藝,因此平面結構采用倍增層在上,吸收層在下的P-i-N結構,如圖2所示。

圖2 平面型SPAD芯片結構示意圖

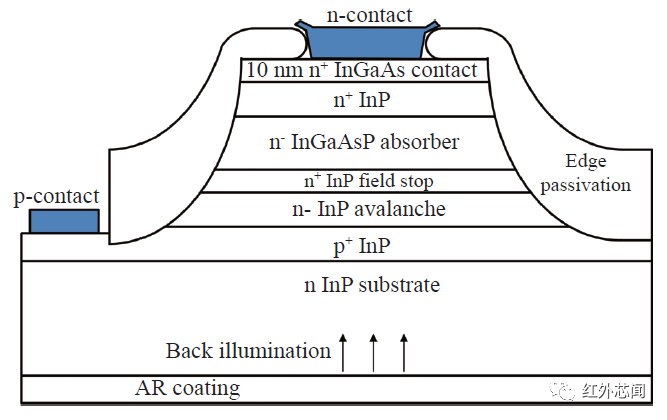

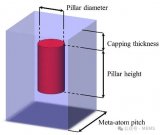

(2)臺面型SPAD器件結構的P-N結通過外延生長而成,吸收區在倍增區上方,如圖3所示。與通過擴散摻雜來限定有源區的平面結構不同的是,其有源區邊緣由臺面的蝕刻結構確定。臺面刻蝕工藝一般選用各向同性的非選擇性腐蝕溶液進行濕法刻蝕,能夠在側壁形成光滑連續坡面。一方面,該坡面便于有機和無機介質在側壁表面形成良好覆蓋,提高鈍化效果;另一方面,該斜坡結構能夠增大底部倍增層橫向寬度,利用中心有源區到邊緣的距離,降低高電場倍增層側壁邊緣的電場,減小暗電流。臺面結構設計通常采用n?型InP襯底,除臺面以外的材料都會被去濕法刻蝕除掉,形成相互隔離的像元。

圖3 臺面型SPAD芯片結構示意圖

CMOS讀出電路芯片

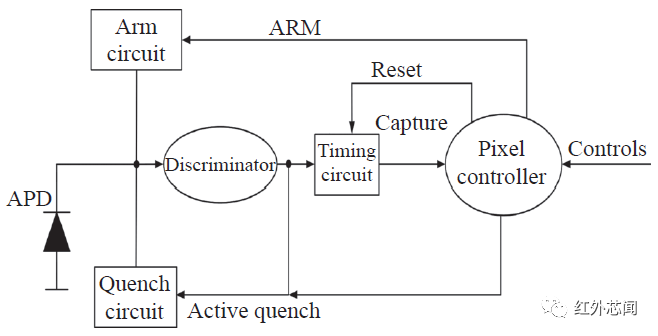

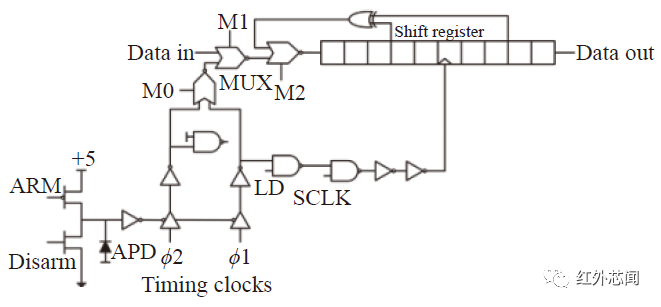

CMOS讀出電路的功能是用于檢測、時間量化以及淬滅SPAD芯片產生的雪崩信號,是實現器件功能的重要部分。InGaAs單光子雪崩焦平面的讀出電路最早由林肯實驗室開發,其基本框圖結構如圖4所示。CMOS讀出電路芯片的單像素電路包括前端電路、計時電路和用于控制像素工作狀態的像素控制電路。前端電路包括:為SPAD提供電壓偏置的偏置電路、用于快速檢測雪崩事件的鑒別器電路以及淬滅電路。計時電路用于光子飛行時間-數字轉換,其輸入與鑒別器的輸出相連。像素控制器相當于有限狀態機,用于控制SPAD偏置到過偏壓狀態、低功耗等待狀態、非使能狀態等。當前端電路檢測到雪崩事件后,淬滅電路快速淬滅SPAD并進入等待狀態,經過預設時間后像素控制電路控制SPAD進入過偏壓狀態,預設時間的長短將直接影響后脈沖的發生概率。

圖4 讀出電路基本框圖

InGaAs單光子雪崩焦平面的進展

InGaAs單光子雪崩焦平面的關鍵指標包括陣列規模、像元中心距、探測效率、暗計數率、時間抖動、累積串擾概率、時間分辨率等。下面圍繞這些指標,從SPAD陣列芯片、讀出電路兩方面的進展進行介紹。

SPAD陣列芯片研究進展

陣列規模與中心距

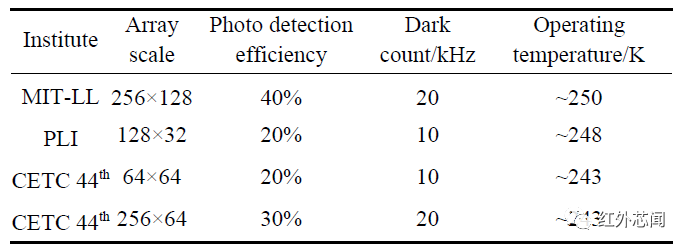

SPAD陣列芯片的陣列規模和中心間距決定了器件的空間分辨率。更大陣列規模、更小中心間距可以獲得更清晰的目標信息。早期MIT-LL的Heinrichs等人采用橋接互連方式,將單個CMOS讀出電路芯片與SPAD晶圓通過環氧樹脂面對面貼合。這種方式通過水平爬坡電極將CMOS讀出電路芯片與SPAD芯片進行電連接,占用面積較大。2011年,Itzler等人研制了128×32規格InGaAs單光子雪崩焦平面,該器件通過器件結構優化及銦柱互連的方式縮小了像元尺寸,像元間距減小到50 μm ,如圖5所示。Younger等人新設計器件的目標是將像元間距進一步減小到25 μm,陣列規模為256×256。國內方面,重慶光電技術研究所研制的64×64 InGaAs單光子雪崩焦平面如圖6所示,像元間距為50 μm,探測效率20%,暗計數率10 kHz,時間分辨率小于1 ns,目前已成功擴展到256×64,性能參數如表1所示。

表1 InGaAs單光子雪崩焦平面參數

大陣列小間距SPAD陣列芯片的發展主要受限于小間距的單元器件設計和陣列芯片工藝。主要手段包括:(1)采用高效率光敏芯片結構設計,并縮小像元尺寸;(2)采用像元間有效隔離結構抑制串擾;(3)采用高質量表面鈍化降低暗電流;(4)采用高質量外延及結擴散工藝,保證陣列芯片一致性;(5)提高小像元下微透鏡的耦合效率。

串擾抑制

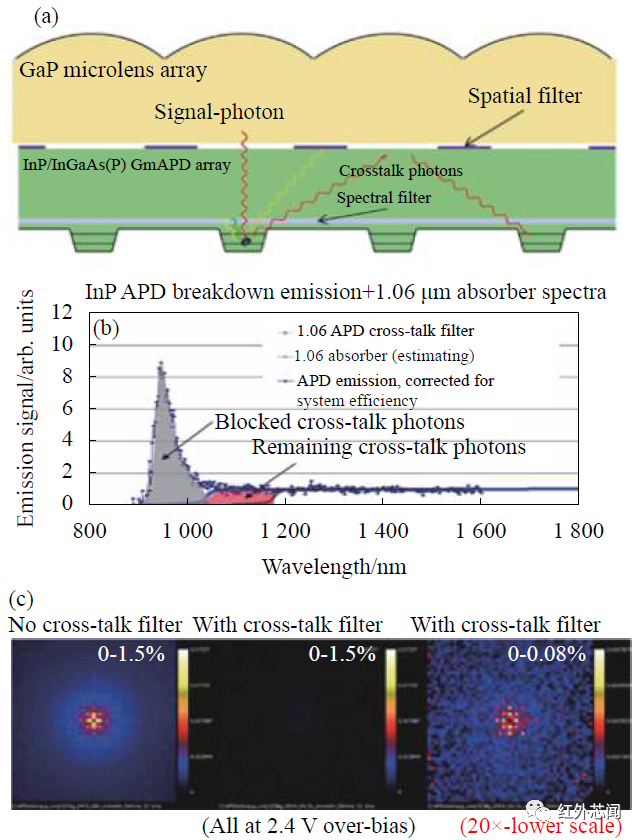

對于大陣列器件,串擾是影響成像質量的重要因素。由于SPAD的高增益特性,鄰近像元產生的極少量光子或漂移電流都可能導致雪崩觸發。串擾主要來源于電串擾和光串擾。像元間的深槽可以有效隔離電串擾。而光串擾主要來源于入射雜散光、鄰近像元的倍增區中熱載流子熒光輻射的次級光子,這些非信號光通過背面反射和橫向渡越傳播到相鄰像元,如圖7(a)所示。倍增區中熱載流子熒光輻射光譜主要分布在900~1000 nm附近,如圖7(b)所示。Acerbi等人采用平面隔離溝道的方式,將串擾概率控制在5%~15%左右。

2009年,Younger等人通過在陣列芯片上設置光譜濾波層和空間濾波層的方法,用光譜濾波層直接將950 nm范圍附近的熒光輻射次級光子吸收掉,配合空間濾波層減少串擾光子數,使過偏壓2.4 V下的串擾從~1%降低至~0.1%,串擾概率下降了1個數量級,如圖7(c)所示。但在高偏壓下,依然存在串擾概率大的問題。2018年,Diagne等人進一步開發了結合襯底移除的像元隔離技術,實現像元正面和背面的完全隔離,切斷了次級光子傳播的路徑,使串擾概率下降約150倍,同時將光譜響應拓展到可見光波段。2020年,Yuan等人基于III-V族化合物工藝平臺研制的InGaP蓋革雪崩焦平面,也采用了該像元隔離技術,使雪崩焦平面在高探測效率下,仍然能夠有效抑制陣列像素的串擾。

圖7 (a)串擾來源示意圖;(b)SPAD自發輻射光譜;(c)串擾抑制

探測效率與暗計數

為提升InGaAs單光子雪崩焦平面的探測效率、暗計數等性能參數,研究人員做了諸多努力。探測效率方面,Donnelly等人通過建立數學模型,詳細分析了SPAD器件結構中各材料層參數對光電性能的影響。重慶光電技術研究所設計了一種增強吸收SPAD結構,將單光子探測效率提升了20%,最高探測效率達到60%。

在減少暗計數方面,提高外延材料質量也是實現高性能器件的重要方式。Chapman等人研究了有機金屬氣相外延的生長溫度、生長速率和V/III比值等工藝條件,使InGaAsP/InP材料300 K下的暗計數降低44%。

CMOS讀出電路及應用進展

InGaAs單光子雪崩焦平面是一種光子信號到數字信號轉換的陣列探測器,針對光子信號的種類與獲取頻率等不同功能的定制方案可以滿足多種不同的應用需求,包括激光雷達、超遠距離激光通信和稀疏光子成像等。其中讀出電路芯片是不同方案的主要差異,其負責完成焦平面除光電轉換外的其他功能的定義與實現。

激光雷達

快閃型激光雷達系統通過用激光短脈沖照射目標場景并在焦平面上接收反射回來的激光脈沖信號完成成像,焦平面上每個像素獨立完成回波脈沖的“光子飛行時間”測量,經數據算法處理后獲得空間深度三維圖像。其中激光回波的探測由SPAD陣列芯片實現,其輸出行為近似于光控數字開關,有光時輸出為“1”,無光時輸出為“0”,即便是單個“光子”量級的信號,其響應速度也可達皮秒級,因此,其極其適合需要精確量化“光子飛行時間”的應用。像素電路實現類似計時秒表功能,激光發射時開始計時,在檢測到回波光子事件后停止計時,在激光脈沖之間的時間間隔(數十微秒級)中讀出計時數據,較長的時間間隔可以有效抑制后脈沖,但也會導致激光雷達用焦平面只能工作在低時間占空比情況下。

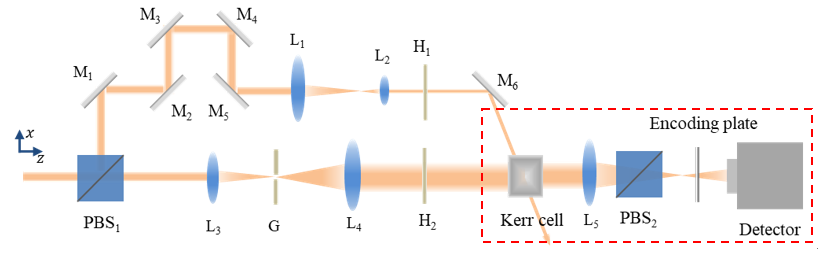

用于激光雷達的陣列讀出電路像元結構如圖8所示。讀出電路采用數字計數器記錄計時時鐘周期個數的原理完成時間測量,但是時鐘頻率會限制時間精度;為了降低計時時鐘頻率,采用帶游標位的多段時間-數字轉換器方案實現時鐘相位的細計數,完成亞ns級以上的計時精度;計時時鐘采用500 MHz,細計數采用4相位就可以實現0.5 ns的分辨率。

圖8 激光雷達用像素電路原理結構圖

隨著陣列規模的擴展,能效比提升在讀出電路架構設計中的重要性逐步增加。目前讀出電路的主流工藝節點為180 nm CMOS。相比早期的讀出電路架構(350 nm),其能效比得到大幅提高。在遠距離激光雷達應用中,每幀的光子事件比較稀疏,三維圖像通常使用多個幀的疊加處理來構建。最新的讀出電路架構設計中利用了這種稀疏檢測的特性,計時電路采用光子事件驅動計時的方案,只有檢測到光子事件的像素計時電路才開始計時工作,所有像素統一結束計時,并在讀出狀態讀出像素數據。讀出中還在讀出數據流中設計數據減薄算法,使功耗、數據量與陣列中活動像素數成正比。傳統方案由于功耗限制其幀頻只設計到20 kf/s的幀速率,而該方案的幀速率可以隨著光子事件越來越稀疏而增加,在每幀有1000個光子事件的稀疏度下,最大可以接近150 kf/s的幀速率,同時大幅降低功耗。

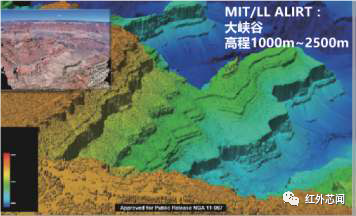

高時間分辨率和高幀頻帶來了更高的測繪精度和掃描速度。2011年,MIT林肯實驗室開發的機載激光雷達成像研究試驗臺(ALIRT),采用128×32 InGaAs單光子雪崩焦平面,在海拔9000 m下對大峽谷(高程差1000~2500 m)進行快速高分辨率廣域地形測繪,掃描速度達到2000 km2/h、分辨率可以達到10 cm級,可以清晰分辨輪廓細節(圖9)。2017年,MIT林肯實驗室基于256×64 InGaAs單光子雪崩焦平面開發了機載光學系統試驗臺(AOSTB),實現了對哈維颶風救災現場的快速成像,目標分辨率精度達到0.25 m。

圖9 美國大峽谷的激光雷達成像圖

超遠距離激光通信

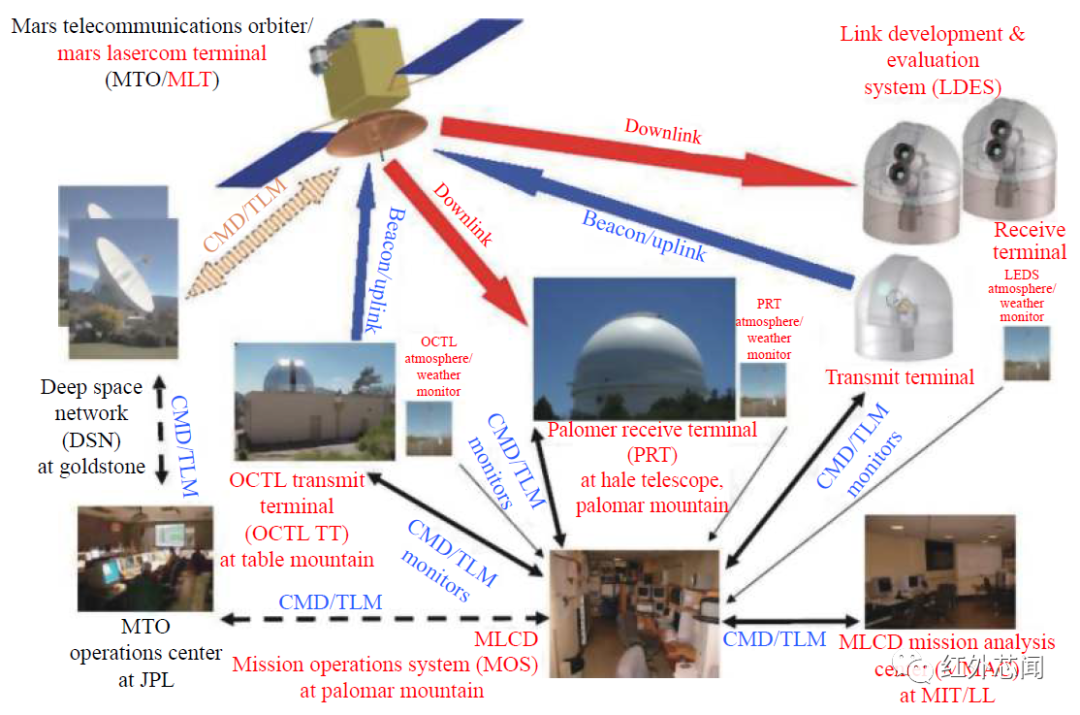

InGaAs單光子雪崩焦平面還可作為自由空間光通信鏈路的接收機,利用脈沖位置調制(PPM)格式完成發射信號調制,接收到的到達時間數據用于數據解調。相比于經典的相干通信系統,其接收機具有捕獲跟蹤通信一體化、體積小、探測靈敏度高的優點,在超遠距離激光通信優勢明顯,NASA已用于火星激光通信MLCD(約2億公里)、月地激光通信LLCD(約40萬公里)等驗證項目,激光通信系統及接收鏈路如圖10所示。

圖10 激光通信系統及接收鏈路示意圖

2013年,NASA完成了世界上第一個月球軌道與地面的雙向激光通信鏈路,采用基于8×8異步讀出InGaAs單光子雪崩焦平面的小型化激光終端(FLT),最高上行傳輸速率達到622 Mbps。同期,NASA近地應用高速激光通信旗艦項目—激光通信中繼演示項目(LCRD),其飛行有效載荷托管在一顆商業通信衛星上,由太空中的兩個激光通信終端組成,同時支持近地激光通信和深空激光通信。

與激光雷達用讀出電路一樣,激光通信用讀出電路同樣需要完成高精度的時間量化功能。然而光通信應用中信號光子到達的時間間隔平均比激光雷達脈沖之間的時間短三個數量級,這就需要更短讀出時間與更大數據量,否則會導致光子信號的堵塞現象。

為了解決這一問題,林肯實驗室于2004年報道了基于事件驅動讀出方法設計的8×8光子計時異步讀出電路陣列。在每個PPM幀中,像素采用與激光雷達讀出電路相同的方法標記光子到達時間。當每一行像素需要讀出時,僅將發生光子事件的像素串入讀出數據流。當下一個PPM幀開始時,沒有獲取光子事件的像素仍然處于活動狀態,而上一幀獲取光子事件的像素則進入等待模式以便抑制后脈沖。該芯片采用350 nm CMOS工藝技術制造并與一個8×8 SPAD陣列混合集成。在美國宇航局火星激光通信演示系統中,在非常高的背景光干擾的情況下,實現了每個光子兩位的數據速率。

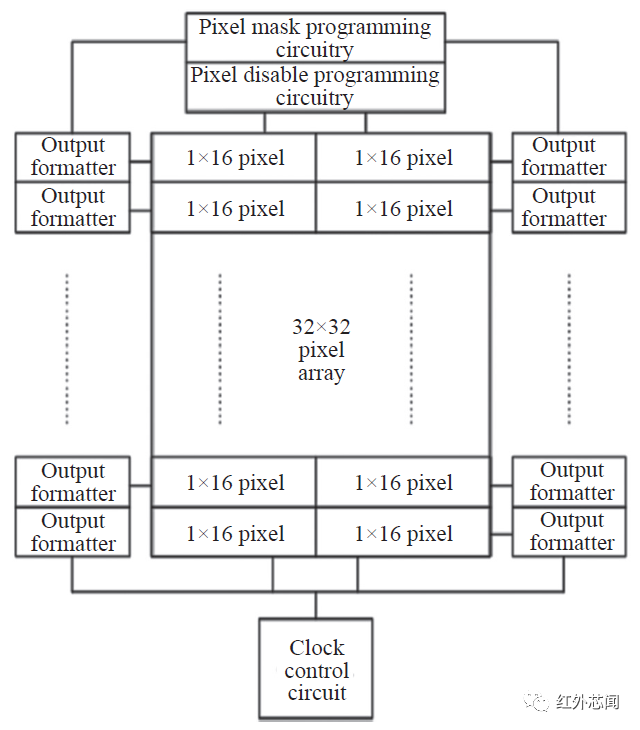

和激光雷達用讀出電路的情況一樣,激光通信用讀出電路同樣需要擴展到更大的陣列,并抑制功耗的增加。這一需求推動下,國外已經開發出32×32陣列的規格產品,并繼續開發256×256等更大規格陣列。32×32異步讀出電路體系結構如圖11所示,通過引入像素禁用、感興趣區域、計時信息與空間位置信息分開等方案與手段,進一步提高的事件驅動讀出的能效比。

圖11 32×32異步讀出電路體系結構框圖

該設計方案中,每個像素都包含計時信息與空間位置信息兩種數據信息,每一行數據讀出時會分為兩個數據流。第一個數據流是顯示所有光子事件的像素位置圖,第二個是帶有嵌入位置信息的計時數據包。該讀出電路還具有像素禁用選項,可以指定任一像素只輸出像素位置圖數據,而不輸出時間信息,這些特性可用于在不需要全部像素數據時減少功耗與輸出數據量。

稀疏光子成像

雪崩焦平面的另一類應用是統計到達每個像素上的光子個數。這些應用不需要精確的計時分辨率,而是需要高探測效率和低暗計數率。傳統的焦平面或圖形傳感器是通過每幀內測量一段積分時間的光子個數來進行強度測量,通過調節積分電容大小完成增益調節;基于蓋革模式的被動成像也類似,通過對一段固定時間的光子數進行多次測量完成積分過程,統計疊加生成強度測量數據,其可以通過調節固定時間大小實現近似增益調節。

稀疏光子成像用讀出電路中的每個像素都有一個計數器代替其他讀出電路中的計時電路,當檢測光子事件發生時,該計數器會增加計數。其難點是降低像素面積并提高陣列規模;降低像素面積一般通過改進計數器結構與更先進的流片工藝實現;另一個難點是提高動態范圍,文獻中報道了多種方案包括計數溢出位、多統計時間數據疊加等。

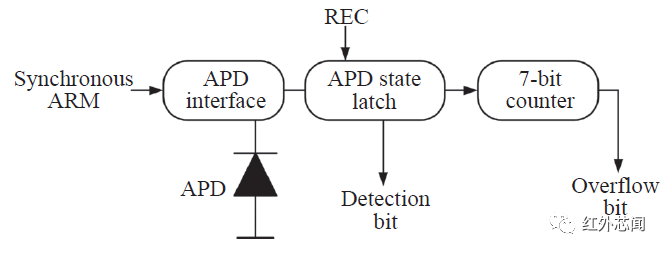

圖12所示為典型的溢出位被動成像讀出電路結構,包括SPAD接口電路、SPAD狀態寄存電路及7 bit計數器。接口電路與其他讀出電路類似,包括偏置與檢測電路;狀態寄存電路存儲每段統計時間的SPAD狀態信息;計數器記錄每幀光子事件的達到次數,計滿后復位重新開始計數,溢出位記錄計數器計滿的狀態,積分中單獨讀出后復位;讀出的數據通過行列尋址讀出到像素外相應像素的存儲位,積分中累加的值作為該像素高位計數數據。在積分結束時,如果7位計數器的數據對像素外高位數據值的貢獻小于暗噪聲,則可以讀出或丟棄7位計數器中的殘余數據。該溢出讀出方案有效地擴展了像素中計數位數。

圖12 帶溢出位被動成像讀出電路結構示意圖

百萬像素InGaAs單光子雪崩焦平面面臨的技術挑戰及未來展望

激光雷達、遠距離激光通信、稀疏光子成像以及未來新應用場景,對更大規模、更小像素、更高性能,以及更多功能的InGaAs單光子雪崩焦平面提出了要求。為了實現百萬像素級InGaAs單光子雪崩焦平面,需要面對SPAD陣列芯片、讀出電路芯片、封裝互連方式等諸多挑戰,具體包括:

(1)SPAD陣列芯片方面,未來InGaAs單光子雪崩焦平面的陣列規模會達到1 k × 1 k以上。為了在高密度、小尺寸像元下還能實現高增益、高計數率、低噪聲、低串擾,需要研究一些新型器件結構設計,如納米SPAD結構、集成負反饋電阻結構(NFAD)、瞬態載流子勢壘層(TCB)自淬滅結構、集成微諧振腔結構等。為了提高視場角和填充因子,超透鏡、自由曲面透鏡等新型微透鏡類型也在研究中。同時,陣列均勻性也是需要重點關注的問題。MIT-LL已經驗證了6 in(1 in=2.54 cm)InP晶圓工藝在提高SPAD陣列均勻性方面的優勢,未來在6 in InP工藝平臺上實現3D集成、高密度封裝變得越來越有吸引力。

(2)受限于SPAD芯片的淺制冷工作環境和讀出電路本身的特點,讀出電路的設計受到挑戰主要有三點如下:1)動態功耗問題,讀出電路存在功耗周期性大幅跳變的特點,導致其動態功耗遠大于同等規模的其他大規模集成電路,功耗大幅跳變會導致電源電壓極度不穩定,造成數據丟失和損壞等問題;2)深亞微米工藝的偏置電壓問題,標準深亞微米工藝中一般只能提供3.3 V的IO電壓,無法滿足SPAD陣列芯片高探測效率和小像素的應用需求;3)總輸出帶寬,讀出電路的最大數據量隨著陣列規模增長線性增長,大陣列高幀頻帶來超大數據量讀出必定會帶來功耗、工藝、設計復雜度等問題。

(3)面對一些新的探測需求,如可重構探測、主被動復合探測等,InGaAs單光子雪崩焦平面的發展需要不斷融合創新架構、創新算法。目前國際上已經出現了多種新型讀出電路架構以及針對偏置電壓和像素小型化問題提出了SPAD芯片、模擬電路與數字電路采用不同工藝三維異質集成封裝方案、工藝限制下采用低壓晶體管串聯疊加實現高偏置電壓像素電路方案等;針對芯片IO高輸出帶寬問題提出了多幀疊加計時直方圖數據減薄算法、低誤碼數據壓縮算法等;針對多功能需求,提出了多功能復合讀出電路,一種是局部多功能方案,全局像素功能是統計光子個數,局部選擇區域像素實現光子計時或異步光子計時。另一種是不同功能對應不同分辨率,全分辨率像素功能是統計光子個數,相鄰像素合并大像素后實現光子計時功能。

結論

作為一種高靈敏度、高時間分辨率的探測器,InGaAs單光子雪崩焦平面在激光三維成像、遠距離激光通信、稀疏光子探測等領域已成功應用。InGaAs單光子雪崩焦平面采用半導體工藝,在陣列擴展、功能擴展方面有明顯優勢。文中從器件結構設計、芯片工藝、電路設計等方面對InGaAs單光子雪崩焦平面進行了分析介紹,并對未來百萬像素級焦平面技術發展進行了展望。

審核編輯:劉清

-

PMT

+關注

關注

0文章

19瀏覽量

10795 -

光電二極管

+關注

關注

10文章

405瀏覽量

36053 -

光電倍增管

+關注

關注

3文章

62瀏覽量

13330 -

單光子探測器

+關注

關注

1文章

31瀏覽量

4479

原文標題:綜述:InGaAs單光子雪崩焦平面研究進展

文章出處:【微信號:MEMSensor,微信公眾號:MEMS】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

上海光機所在多路超短脈沖時空同步測量方面取得研究進展

AI大模型的最新研究進展

基于SPAD單光子相機的LiDAR技術革新

單光子雪崩探測器SPAD助力激光掃描顯微鏡發展

基于VLPE技術的碲鎘汞p-on-n雙層異質結材料與器件研究進展

在前照式SPAD像素上實現的兩代基于超構表面的平面微透鏡設計

綜述:高性能銻化物中紅外半導體激光器研究進展

什么是單光子探測器

基于PIN結構的碲鎘汞線性雪崩焦平面器件技術

InGaAs單光子雪崩焦平面研究進展

InGaAs單光子雪崩焦平面研究進展

評論