在定向測試用例中,我們就是在不同的時刻將“0”或者“1”驅動到接口總線上。如果我們希望提高這個總線操作的順序,會將相同的操作序列封裝成task(bfm model)。

在現代驗證環境中,激勵的生成要復雜得多,我們需要創建更真實的芯片外界環境。激勵生成的語言要更加抽象,我們需要

隨機某些字段

隨機某個數據驅動到接口的次數

在輸入數據流中注入錯誤

按照一定順序運行各種操作,同時并發運行其他操作

每一顆都會有相對固定的流程,所以激勵流程必須遵守這個流程才讓讓芯片正常work。但是這個事情并不簡單,當我們和設計溝通、當你讀規格或者使用手冊時會發現這個流程的驗證空間的復雜度非常爆炸。

問題越來越多,再怎么厲害的大腦也覺得復雜度不受控。

太多的選擇,太多的如果

事實上,“芯片的一天”也不是完全失控,其中會存在很多個基本的流程,復雜的事情都是在這個基本的流程下組合而來的。例如,芯片可能在復位后加載指令、執行任務、等待中斷等等。

團隊中的每個工程師(設計和驗證)都應該知道這個基本流程。對于驗證來說,應該先從基本的流程開始測試,然后擴展到各種復雜的場景隨機用例。

審核編輯:劉清

-

驅動接口

+關注

關注

0文章

10瀏覽量

2633

原文標題:驗證的激勵生成流程

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

使用HLS流程設計和驗證圖像信號處理設備

串聯諧振激勵變壓器定義與原理

如何在TI-NA里的信號編輯器中生成自己的激勵波形?

雙管正激勵磁復位電路的作用

大規模 SoC 原型驗證面臨哪些技術挑戰?

如何將SystemVerilog斷言屬性和覆蓋屬性置于在設計上?

E-Val Pro Plus有線驗證解決方案,功能升級,優化制藥流程,確保安全性和合規性!

fpga原型驗證流程

珠海南方集成電路設計服務中心引進芯華章全流程驗證工具

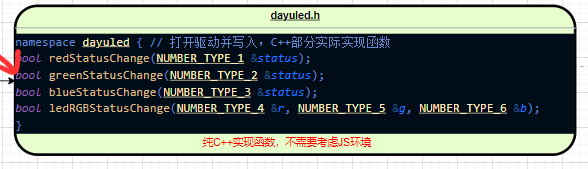

【鴻蒙】NAPI 框架生成工具實現流程

淺析驗證的激勵生成流程

淺析驗證的激勵生成流程

評論