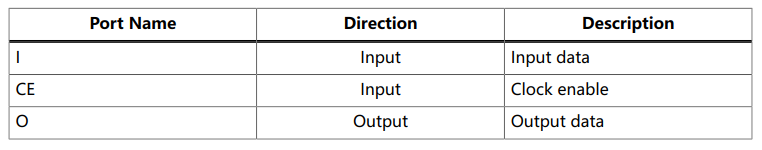

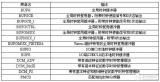

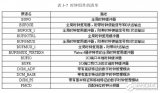

易靈思提供了原語文檔,可以查看每個原語。經(jīng)常有人會問,如果普通的GPIO怎么走全局時鐘網(wǎng)絡(luò),其實很簡單,打開原主文檔,找到EFX_GBUFCE,該部分提供了verilog和VHDL的用法。

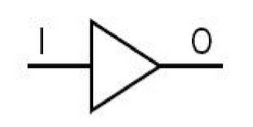

EFX_GBUFCE既可以讓GPIO走全局時鐘網(wǎng)絡(luò)也可以用于為時鐘添加使能控制,當并不是隨時需要該時鐘時可以把時鐘禁止以節(jié)省功耗。

CE_POLARITY用于指示CE是高有效還是低有效,如果為1則高有效,反之則低有效。

CE是時鐘O的輸出使能。

EFX_GBUFCE # ( .CE_POLARITY(1'b1) // 0 active low, 1 active high ) EFX_GBUFCE_inst ( .O(O), // Clock output to global clock network .I(I), // Clock input .CE(CE) // Clock gate );

審核編輯:劉清

-

GPIO

+關(guān)注

關(guān)注

16文章

1216瀏覽量

52377 -

時鐘網(wǎng)絡(luò)

+關(guān)注

關(guān)注

0文章

16瀏覽量

6583 -

VHDL電路

+關(guān)注

關(guān)注

0文章

4瀏覽量

1425

原文標題:GBUFCE原語

文章出處:【微信號:gh_ea2445df5d2a,微信公眾號:FPGA及視頻處理】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

Xilinx中的原語作用是啥啊?

xilinx原語問題

如何從Virtex原語切換到Spartan原語?

Xilinx FPGA常用原語介紹

基于URAM原語創(chuàng)建容量更大的RAM

Xilinx原語使用方法有哪些

Xilinx原語使用方法

GBUFCE原語介紹

GBUFCE原語介紹

評論