1 數(shù)的表示與布爾代數(shù)

1.1 數(shù)的編碼與二進(jìn)制表示

編碼是各種集合的元素映射到字符串的過程 。數(shù)字電路中的數(shù)字表示就是一串用已約定好的表示的 0 和 1 的組合。二進(jìn)制的優(yōu)點(diǎn):

運(yùn)算簡(jiǎn)單 ——算術(shù)運(yùn)算加法和乘法僅各有3條規(guī)則不易出錯(cuò) ;邏輯運(yùn)算可與“真”“假” 對(duì)應(yīng)

存儲(chǔ)簡(jiǎn)單 ——高低電壓表示兩種狀態(tài);有更大的噪聲容限

1.1.1 常見的編碼

二元編碼 ——條形碼

BCD碼 ——會(huì)計(jì)系統(tǒng)長(zhǎng)數(shù)字串計(jì)算

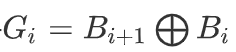

格雷碼 —— ,其中B為二進(jìn)制編碼首位補(bǔ)一個(gè)0。九連環(huán)341種狀態(tài)。2G一改零不改,G2奇變偶不變

,其中B為二進(jìn)制編碼首位補(bǔ)一個(gè)0。九連環(huán)341種狀態(tài)。2G一改零不改,G2奇變偶不變

1.2 二進(jìn)制補(bǔ)碼表示

1.2.1 補(bǔ)碼分類

有符號(hào)數(shù) ——開頭位0正1負(fù)

1補(bǔ)碼 ——負(fù)數(shù)對(duì)應(yīng)的二進(jìn)制正數(shù) N 按位取反,2n-1-N。0有兩種表示,-(2n-1-1)~2n-1-1

2補(bǔ)碼 ——按位取反再+1,2n-N。0有唯一表示便于減法轉(zhuǎn)加法,-2n-1~2n-1-1

1.2.2 溢出判斷

對(duì)數(shù)字最高有效位進(jìn)位和符號(hào)位進(jìn)位做異或,為1則溢出;或滿足其一即可判別:

符號(hào)異常 ——兩個(gè)加數(shù)符號(hào)位相同但是與結(jié)果符號(hào)位不同

進(jìn)位異常 ——內(nèi)部進(jìn)位(結(jié)果的符號(hào)位)≠外部進(jìn)位(結(jié)果擴(kuò)展位)

1.3 邏輯與布爾代數(shù)

1.3.1 基本定理

交換,結(jié)合,分配,互補(bǔ),01,重疊,對(duì)合

對(duì)偶 ——與或互換,01 互換,布爾變量不變

多數(shù) ——(X+Y)(Y+Z)(X’+Z)=(X+Y)(X’+Z) , XY+YZ+X’Z=XY+X’Z 可用于消除競(jìng)爭(zhēng)冒險(xiǎn)

1.3.2 德摩根定理

與或互換,01 互換,布爾變量求反得到 反函數(shù) (注意到和對(duì)偶只相差是否變量求反)

一般來說,將布爾函數(shù)表示成與非門,可以用最小的代價(jià)實(shí)際映射到電路

1.4 布爾函數(shù)表示

程序表達(dá)、二分決策圖、真值表、卡諾圖、邏輯電路

1.4.1 兩級(jí)邏輯

最小項(xiàng)或=互補(bǔ)序號(hào)的最大項(xiàng)與

1.4.2 布爾代數(shù)化簡(jiǎn)

代數(shù)化簡(jiǎn) ——并項(xiàng)、吸收、消去、配項(xiàng)(冗余定理)

卡諾圖化簡(jiǎn) ——能夠蘊(yùn)含一個(gè)函數(shù)的與項(xiàng)是 蘊(yùn)含項(xiàng) ;不存在蘊(yùn)含項(xiàng) I≠P,使得 P => I => F,則稱 P 為 本原蘊(yùn)含項(xiàng) ;某個(gè)元素僅由一個(gè)本原蘊(yùn)含項(xiàng)覆蓋,則該蘊(yùn)含項(xiàng)為本質(zhì)本原蘊(yùn)含項(xiàng)

QM化簡(jiǎn) ——搜索本原蘊(yùn)含項(xiàng),尋找最小覆蓋

在邏輯表達(dá)式中,如果能夠?qū)?a target="_blank">信號(hào)合并使得輸入端出現(xiàn) 盡可能少的信號(hào)種類 ,那么就有可能減少整個(gè)門電路的MOS管個(gè)數(shù)

2 組合電路與邏輯綜合

在實(shí)際電路中,想要實(shí)現(xiàn)與/或門,一般都采用 NAND/NOR + 非門的形式。組合邏輯是當(dāng)前的輸入變量取值決定當(dāng)前的輸出的 無記憶元件 ,且輸出是輸入邏輯變量的函數(shù)。

CMOS ——高密度、低功耗,系統(tǒng)成本低,適用于主流數(shù)字系統(tǒng)

BJT ——超高速、超低噪聲,適用于高速應(yīng)用例如一些模擬和射頻電路

2.1 組合邏輯分解

多級(jí)邏輯的基本表示方法是 復(fù)合函數(shù) 。一方面類似因式分解將函數(shù)計(jì)算進(jìn)行分解化簡(jiǎn);另一方面可以共享中間層次的計(jì)算。

2.2 組合邏輯中的競(jìng)爭(zhēng)與冒險(xiǎn)

毛刺 ——出現(xiàn)在組合邏輯電路輸出端的多余脈沖,本應(yīng)保持不變的輸出值出現(xiàn)了瞬時(shí)變化。輸出的毛刺是單端輸入取值變化的結(jié)果

冒險(xiǎn) ——有可能產(chǎn)生毛刺的電路存在冒險(xiǎn),冒險(xiǎn)是一個(gè)電路的固有特征,存在冒險(xiǎn)的電路可能產(chǎn)生毛刺,也可能不產(chǎn)生毛刺

靜態(tài)冒險(xiǎn) ——一個(gè)本應(yīng)保持不變的輸出經(jīng)歷瞬時(shí)轉(zhuǎn)換

- 靜態(tài)1冒險(xiǎn):取值為1的輸出瞬時(shí)經(jīng)歷0狀態(tài)

- 靜態(tài)0冒險(xiǎn):取值為0的輸出瞬時(shí)經(jīng)歷1狀態(tài)

動(dòng)態(tài)冒險(xiǎn) ——本應(yīng)單次跳變的輸出信號(hào)發(fā)生不止一次的跳變

- 多級(jí)電路存在多條路徑,且這些路徑的延時(shí)是不對(duì)稱的

- 一個(gè)無靜態(tài)冒險(xiǎn)的多級(jí)網(wǎng)絡(luò)仍可能存在動(dòng)態(tài)冒險(xiǎn)

2.2.1 組合邏輯靜態(tài)冒險(xiǎn)消除

增加冗余 ——如果輸入初始值和輸入最終值能被同一個(gè)本原蘊(yùn)含項(xiàng)覆蓋,則不會(huì)出現(xiàn)毛刺(靜態(tài)1冒險(xiǎn))。

采樣脈沖 ——采樣脈沖在D穩(wěn)定期間進(jìn)行采樣

2.3 評(píng)價(jià)邏輯電路的主要指標(biāo)因素

2.3.1 穩(wěn)態(tài)因素

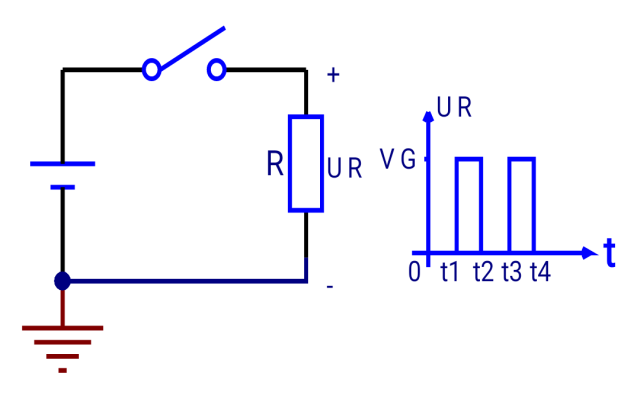

邏輯電平 ——邏輯0和1對(duì)應(yīng)的電壓范圍越寬,抗干擾的能力越強(qiáng),對(duì)電子元器件參數(shù)精度的要求及電源電壓范圍的穩(wěn)定度的要求越高

噪聲容限 ——輸出電壓與輸入電壓之間的電壓差稱為噪聲容限

扇出系數(shù) ——最壞負(fù)載情況下一個(gè)邏輯門能驅(qū)動(dòng)的輸入端數(shù)目。TTL電路的扇出系數(shù)一般小于10,MOS電路的扇出系數(shù)不受負(fù)載影響,但是隨著扇出的增大,負(fù)載電容增大,導(dǎo)致工作速度大幅下降

2.3.2 動(dòng)態(tài)因素

轉(zhuǎn)換時(shí)間 ——邏輯門的輸出從一個(gè)狀態(tài)變化到另一個(gè)狀態(tài)所用的時(shí)間

延時(shí) ——從邏輯門的輸入發(fā)生變化到相應(yīng)的輸出發(fā)生變化所用的時(shí)間,會(huì)導(dǎo)致冒險(xiǎn)的存在

功耗 ——分為動(dòng)態(tài)功耗(CMOS由開關(guān)電流和短路電流引起)和靜態(tài)功耗

- 開關(guān)電流是不斷對(duì)負(fù)載電容充放電所產(chǎn)生的

- 短路電流是輸入存在有限轉(zhuǎn)換時(shí)間引起PMOS/NMOS同時(shí)導(dǎo)通形成的

低功耗技術(shù) ——降低電路的功耗以延長(zhǎng)壽命,應(yīng)該降低電路的電壓和頻率,導(dǎo)致工作速度下降 ,因而追求低功耗延時(shí)積

2.4 常用的邏輯功能的實(shí)現(xiàn)與優(yōu)化

2.4.1 傳輸門

使能控制信號(hào)EN為低電平時(shí),TG截止,F(xiàn)為 高阻態(tài) ——相當(dāng)于懸空,如果用萬用表測(cè)可能是高電平也可能是低電平

總線應(yīng)用 ——各門的控制端EN輪流單獨(dú)為高電平

2.4.2 編碼器/譯碼器

編碼器 ——按照輸入是否有優(yōu)先級(jí)分為普通編碼器(單1)和優(yōu)先編碼器(多1)

譯碼器 ——每個(gè)輸出對(duì)應(yīng)一個(gè)最小項(xiàng)

2.4.3 多路選擇器

對(duì)應(yīng)通過地址查表的過程。2n個(gè)數(shù)據(jù)輸入, n個(gè)選擇輸入,1個(gè)數(shù)據(jù)輸出

n變量邏輯函數(shù) ——函數(shù)輸入變量加到地址端,數(shù)據(jù)輸入端賦值

m(>n)變量邏輯函數(shù) ——函數(shù)的m-1個(gè)輸入變量加到地址端,數(shù)據(jù)輸入端以第m個(gè)輸入變量的邏輯關(guān)系賦值

- m=n+1時(shí),不需要任何附加的邏輯門

2.4.4 加法器

半加器不考慮進(jìn)位;全加器考慮進(jìn)位,輸和Si和進(jìn)位Ci+1

串行加法器 ——電路簡(jiǎn)單、速度慢

并行加法器 ——電路復(fù)雜、速度快

組內(nèi)并行、組間串行進(jìn)位加法器 ——層次化設(shè)計(jì),解決扇出增大導(dǎo)致的加法器延時(shí)

3 時(shí)序邏輯與FSM

3.1 基本概念

過程在數(shù)學(xué)上可以表示為時(shí)間的函數(shù)。過程需要用不同的狀態(tài)表示,這些狀態(tài)需要用記憶元件來控制和預(yù)測(cè)

3.1.1 過程離散化與時(shí)鐘

過程離散化 ——即時(shí)間離散化、狀態(tài)數(shù)字化。將過程離散化是為了充分利用數(shù)字信號(hào)處理的快捷和高效

時(shí)鐘 ——分布于包含記憶元件的電路中的一個(gè)周期信號(hào),用來同步控制所有時(shí)序單元。保證所有元件都在同一時(shí)刻改變狀態(tài)的是 同步電路 ,沒有時(shí)鐘或不使用同一個(gè)時(shí)鐘信號(hào)的是異步電路

擺率 ——在單位時(shí)間里電壓升高/下降的幅度,影響上升和下降沿時(shí)間

時(shí)鐘信號(hào)產(chǎn)生 ——利用電路中的延時(shí),采用反相器或者環(huán)形振蕩器

3.1.2 時(shí)鐘域與同步處理

時(shí)鐘域 ——所有同步于同一個(gè)時(shí)鐘信號(hào)的信號(hào)集合。同一個(gè)時(shí)鐘域中的信號(hào)只能由同一個(gè)時(shí)鐘的時(shí)鐘沿來觸發(fā),時(shí)隙內(nèi)所有的信號(hào)不會(huì)發(fā)生變化

跨時(shí)鐘域 ——在兩個(gè)不同的時(shí)鐘域之間傳遞數(shù)據(jù),二者時(shí)鐘頻率不一樣,或者頻率相同但存在相位差,來自一個(gè)時(shí)鐘域的信號(hào)被另一個(gè)時(shí)鐘域認(rèn)為是異步的輸入信號(hào)

同步處理 ——當(dāng)數(shù)據(jù)與采樣時(shí)鐘異步時(shí),或跨時(shí)鐘域時(shí),就需要對(duì)信號(hào)事件順序的決定和處理。

3.1.3 狀態(tài)

狀態(tài) ——系統(tǒng)的基本數(shù)學(xué)特征

時(shí)序邏輯需要將輸入信號(hào)的歷史信息存儲(chǔ)下來。而狀態(tài)變量的取值就是用來記錄電路過去的信息,從而說明電路將來的行為

3.1.4 有限狀態(tài)機(jī)

狀態(tài)機(jī) ——離散數(shù)學(xué)模型,給定一個(gè)輸入集合,根據(jù)對(duì)輸入的接收次序來決定一個(gè)輸出集合

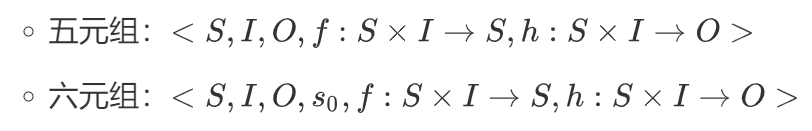

有限狀態(tài)機(jī) ——輸入集合和輸出集合都是有限的,且狀態(tài)數(shù)目是有限的。有限狀態(tài)集合S,有限輸入符號(hào)集合I,有限輸出符號(hào)集合O,初始狀態(tài)s0,狀態(tài)轉(zhuǎn)移規(guī)則f ,輸出規(guī)則h

** Mealy機(jī)** ——輸出依賴于當(dāng)前的網(wǎng)絡(luò)狀態(tài)和當(dāng)前的輸入

** Mealy機(jī)** ——輸出依賴于當(dāng)前的網(wǎng)絡(luò)狀態(tài)和當(dāng)前的輸入

Moore機(jī) ——輸出只依賴于電路當(dāng)前的狀態(tài),和當(dāng)前輸入無關(guān)

狀態(tài)轉(zhuǎn)換表 ——有限狀態(tài)機(jī)的描述方法:輸入、現(xiàn)態(tài)、次態(tài)、輸出

3.2 鎖存器

鎖存器 ——在任意時(shí)刻都連續(xù)監(jiān)測(cè)其輸入,并改變其輸出狀態(tài),與有無時(shí)鐘信號(hào)無關(guān)。鎖存就是將信號(hào)暫存以維持某種電平狀態(tài),在計(jì)算機(jī)或數(shù)字系統(tǒng)的輸入緩沖電路中廣泛使用。這樣可防止輸入信號(hào)的各個(gè)位到達(dá)時(shí)間不一致造成競(jìng)爭(zhēng)與險(xiǎn)象

可以有時(shí)鐘信號(hào)作為控制端,在有效期間時(shí)刻檢測(cè)輸入取值,具有透明性

3.2.1 SR 鎖存器、D 鎖存器

SR鎖存器 ——

門控SR鎖存器 ——C=1時(shí)S置位R復(fù)位,C=0時(shí)狀態(tài)不變

時(shí)序電路的競(jìng)爭(zhēng) ——最終電路產(chǎn)生的狀態(tài)與時(shí)間相關(guān),且不能事先預(yù)測(cè),通過約束輸入取值來避免競(jìng)爭(zhēng)條件的出現(xiàn)

門控D鎖存器 ——C=1時(shí)隨D變化,C=0時(shí)狀態(tài)不變

3.2.2 鎖存器的時(shí)間參數(shù)

最小脈寬 ——為了得到希望的輸出結(jié)果,輸入信號(hào)有效的最短時(shí)間

延時(shí) ——輸入信號(hào)發(fā)生變化,導(dǎo)致輸出信號(hào)發(fā)生相應(yīng)變化的時(shí)間

建立時(shí)間 ——鎖存操作開始之前,輸入信號(hào)應(yīng)保持不變的最短時(shí)間

保持時(shí)間 ——鎖存操作之后,輸入信號(hào)還應(yīng)保持不變的最短時(shí)間

3.2.3 亞穩(wěn)態(tài)

亞穩(wěn)態(tài) ——不確定狀態(tài)。若信號(hào)不滿足建立時(shí)間與保持時(shí)間約束,在時(shí)鐘的上升沿采樣的信號(hào)正在發(fā)生變化,則輸出可能為1或0

產(chǎn)生原因 ——不同時(shí)鐘域的存在,時(shí)鐘偏差的普遍存在

解決方法 ——同步器設(shè)計(jì),異步FIFO,被采樣信號(hào)滿足建立時(shí)間與保持時(shí)間約束

3.3 基本時(shí)序邏輯單元——觸發(fā)器

觸發(fā)器 ——僅在時(shí)鐘信號(hào)有效時(shí)采樣輸入,并改變其輸出狀態(tài)

3.3.1 主從SR觸發(fā)器

主從觸發(fā)器 ——脈寬觸發(fā)的觸發(fā)器,可避免鎖存器的透明性。在控制信號(hào)發(fā)生改變時(shí),觸發(fā)器狀態(tài)發(fā)生相應(yīng)的變化。具有一個(gè)主觸發(fā)器和一個(gè)從觸發(fā)器

主從SR觸發(fā)器 ——高電平主觸發(fā)器置位復(fù)位,下降沿從觸發(fā)器獲得主觸發(fā)器之前的狀態(tài)

3.3.2 邊沿D觸發(fā)器

邊沿觸發(fā)器 ——利用時(shí)鐘的上升沿或者下降沿進(jìn)行觸發(fā),改變輸出。只要在觸發(fā)沿處,輸入的取值在建立時(shí)間和保持時(shí)間內(nèi)固定不變,在觸發(fā)器的固有延時(shí)之后立即發(fā)生相應(yīng)的變化

邊沿D觸發(fā)器 ——高電平主觸發(fā)器置位復(fù)位,下降沿從觸發(fā)器獲得主觸發(fā)器之前的狀態(tài)

3.3.3 JK觸發(fā)器與T觸發(fā)器

JK觸發(fā)器 ——相比SR觸發(fā)器,JK=1時(shí)狀態(tài)反向

T觸發(fā)器 ——0不變1反向

3.3.4 觸發(fā)器的時(shí)間參數(shù)

建立時(shí)間 ——觸發(fā)器時(shí)鐘沿到來之前輸入信號(hào)應(yīng)保持不變的最短時(shí)間

保持時(shí)間 ——觸發(fā)器時(shí)鐘沿到來之后輸入信號(hào)還應(yīng)保持的最短時(shí)間

輸出響應(yīng)時(shí)間 ——從開始采樣到輸出信號(hào)的延時(shí)

3.4 同步時(shí)序電路分析和設(shè)計(jì)方法

避免反饋振蕩 ——插入時(shí)鐘控制的觸發(fā)器

3.4.1 同步時(shí)序電路的分析方法

- 寫出各觸發(fā)器的激勵(lì)方程( 驅(qū)動(dòng)方程 )

- 把得到的驅(qū)動(dòng)方程代入到觸發(fā)器的特性方程,得到次態(tài)方程

- 按照電路圖得到輸出方程

- 根據(jù)次態(tài)方程和輸出方程得到狀態(tài)表

- 得到時(shí)序電路的狀態(tài)圖

- 畫出時(shí)序圖

- 確定電路行為

3.4.2 Moore機(jī)和Mealy機(jī)輸出時(shí)序?qū)Ρ?/h4>

理論分析時(shí)僅在時(shí)鐘觸發(fā)沿時(shí)刻考慮外部輸入對(duì)時(shí)序電路的影響,而米利型電路的輸出與外部輸入時(shí)時(shí)刻刻都相連

Moore輸出 ——狀態(tài)數(shù)更多,與時(shí)鐘同步

Mealy輸出 ——狀態(tài)數(shù)更少,與時(shí)鐘異步,輸入變化則立即變化。可通過觸發(fā)器消除時(shí)序關(guān)聯(lián)

3.4.3 同步時(shí)序電路的設(shè)計(jì)方法

等價(jià)狀態(tài)對(duì) ——當(dāng)且僅當(dāng)它們輸出相同、次態(tài)等價(jià)

狀態(tài)不等價(jià) ——至少有一種輸入序列會(huì)使得它們作為起始狀態(tài)時(shí)產(chǎn)生不同的輸出序列

- 確定輸入輸出并抽象出有限狀態(tài)機(jī),得到狀態(tài)表或狀態(tài)圖

- 狀態(tài)化簡(jiǎn) ——行匹配技術(shù)(合并具有相同次態(tài)和輸出的行)、蘊(yùn)含表技術(shù)(輸出不同x,次態(tài)輸出都相同√,其他待定)

- 狀態(tài)分配

- 順序編碼(二進(jìn)制/格雷)

- 隨機(jī)編碼、緊湊型編碼、單點(diǎn)編碼、面向輸出的編碼

- 啟發(fā)式方法(最少位變化:基于次態(tài)和輸入/輸出的準(zhǔn)則[*])

- 確定激勵(lì)方程和輸出方程

- 畫出兩級(jí)或者多級(jí)邏輯電路圖

[*]基于次態(tài)和輸入/輸出的準(zhǔn)則

Rule I ——具有相同次態(tài)的狀態(tài)應(yīng)該具有相鄰的狀態(tài)編碼

Rule II ——同一狀態(tài)的次態(tài)應(yīng)該具有相鄰的狀態(tài)編碼

Rule III ——具有相同輸出的狀態(tài)應(yīng)具有相鄰的狀態(tài)編碼

3.4.4 典型的時(shí)序邏輯電路——寄存器

(存儲(chǔ))寄存器 ——數(shù)字系統(tǒng)的存儲(chǔ)元件,由n個(gè)觸發(fā)器構(gòu)成

移位寄存器 ——數(shù)字系統(tǒng)中既能寄存二進(jìn)制信息又能移位的邏輯元件,分為左移寄存器、右移寄存器、雙向移位寄存器。也可按照并/串行輸入輸出分類

串行輸入 ——簡(jiǎn)單,存儲(chǔ)時(shí)間長(zhǎng)(n周期)

并行輸入 ——多路選擇實(shí)現(xiàn)移位/加載模式,單周期全加載

串行輸出 ——僅最后一個(gè)存儲(chǔ)單元值可見,減少輸出端數(shù)目

并行輸出 ——所有觸發(fā)器儲(chǔ)值可見

3.4.5 典型的時(shí)序邏輯電路——計(jì)數(shù)器

計(jì)數(shù)器 ——記錄輸入脈沖的個(gè)數(shù),其最大值稱作 模 ,用于定時(shí)、分頻、產(chǎn)生節(jié)拍脈沖及數(shù)字運(yùn)算等等。可以分為加法、減法、可逆計(jì)數(shù)器;特殊進(jìn)制計(jì)數(shù)器;利用移位寄存器構(gòu)成的計(jì)數(shù)器

自啟動(dòng) ——非正常工作狀態(tài)能經(jīng)過若干次狀態(tài)轉(zhuǎn)換進(jìn)入正常工作狀態(tài)

- 增加組合電路

- 利用觸發(fā)器預(yù)置位和復(fù)位端重新加載觸發(fā)器狀態(tài)使回到正常序列或起始狀態(tài)

環(huán)形計(jì)數(shù)器 —— 循環(huán)的移位寄存器 。將移位寄存器的串行輸出接回串行輸入。電路簡(jiǎn)單,浪費(fèi)狀態(tài)

扭環(huán)形計(jì)數(shù)器 ——將移位寄存器的串行輸出反接回串行輸入。加倍模值,提高狀態(tài)利用率。

異步計(jì)數(shù)器 ——低位計(jì)數(shù)器的反向輸出是高位計(jì)數(shù)器的時(shí)鐘信號(hào),低位都為1時(shí)高位才翻轉(zhuǎn),最低位每次翻轉(zhuǎn)

同步計(jì)數(shù)器 ——組合邏輯實(shí)現(xiàn)翻轉(zhuǎn)規(guī)則:與門輸入數(shù)目增加或延時(shí)增加

-

編碼

+關(guān)注

關(guān)注

6文章

957瀏覽量

54951 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1629瀏覽量

80822 -

邏輯運(yùn)算

+關(guān)注

關(guān)注

0文章

57瀏覽量

9785

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

模擬和數(shù)字電路基礎(chǔ)知識(shí)匯總

模擬和數(shù)字電路基礎(chǔ)知識(shí)匯總

模擬和數(shù)字電路基礎(chǔ)知識(shí)匯總

數(shù)字電路基礎(chǔ)知識(shí)相關(guān)資料下載

電子電路基礎(chǔ)知識(shí)

數(shù)字電路基礎(chǔ)知識(shí)

數(shù)字電路基礎(chǔ)知識(shí)

17個(gè)圖解數(shù)字電路基礎(chǔ)知識(shí)

數(shù)字電路基礎(chǔ)知識(shí)匯總1

數(shù)字電路基礎(chǔ)知識(shí)匯總2

數(shù)字電路基礎(chǔ)知識(shí)匯總2

評(píng)論