在傳統(tǒng)硬件電路的設(shè)計(jì)方法中,當(dāng)設(shè)計(jì)工程師需要設(shè)計(jì)一個(gè)新的硬件、數(shù)字電路或數(shù)字邏輯系統(tǒng)時(shí),需要為此設(shè)計(jì)并畫出一張線路圖, 隨后在 CAE(計(jì)算機(jī)輔助工程分析)工作站上進(jìn)行設(shè)計(jì)。

所設(shè)計(jì)的線路圖由線和符號(hào)組成,其中線代表了線路,符號(hào)代表了基本設(shè)計(jì)單元, 其取自于工程師構(gòu)造此線路圖使用的零件符號(hào)庫(kù)。對(duì)于不同邏輯器件的設(shè)計(jì),需要選擇對(duì)應(yīng)的符號(hào)庫(kù),如當(dāng)設(shè)計(jì)工程師選擇的時(shí)標(biāo)準(zhǔn)邏輯器件( 74 系列等)作為板級(jí)設(shè)計(jì)線路圖,那么此線路圖的符號(hào)則需要取自標(biāo)準(zhǔn)邏輯零件符號(hào)庫(kù);若設(shè)計(jì)工程師進(jìn)行了 ASIC 設(shè)計(jì),線路圖的符號(hào)就要取自 ASIC 庫(kù)專用的宏單元。

這就是傳統(tǒng)的原理圖設(shè)計(jì)方法,原理圖設(shè)計(jì)法存在著許多弊端,如當(dāng)設(shè)計(jì)者想要實(shí)現(xiàn)線路圖的邏輯優(yōu)化時(shí),就需要利用 EDA 工具或者人工進(jìn)行布爾函數(shù)邏輯優(yōu)化。除此之外,傳統(tǒng)原理圖設(shè)計(jì)還存在難以驗(yàn)證的缺點(diǎn),設(shè)計(jì)工程師想要驗(yàn)證設(shè)計(jì),必須通過(guò)搭建硬件平臺(tái)(比如電路板), 為設(shè)計(jì)驗(yàn)證工作帶來(lái)了麻煩。

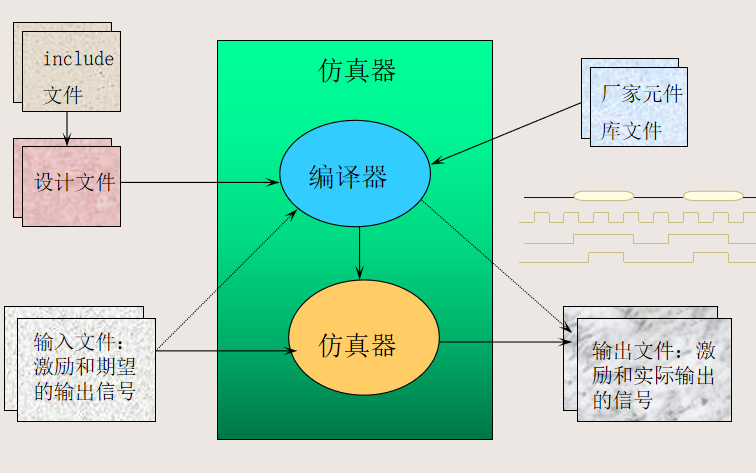

隨著人們對(duì)于科技的要求與期待越來(lái)越高,電子設(shè)計(jì)技術(shù)發(fā)展也越來(lái)越快,設(shè)計(jì)的集成度、復(fù)雜程度也逐漸加深,傳統(tǒng)的設(shè)計(jì)方法已經(jīng)無(wú)法滿足高級(jí)設(shè)計(jì)的需求,最終出現(xiàn)了借助先進(jìn) EDA 工具的一種描述語(yǔ)言設(shè)計(jì)方法,可以對(duì)數(shù)字電路和數(shù)字邏輯系統(tǒng)進(jìn)行形式化的描述,這種語(yǔ)言就是硬件描述語(yǔ)言。硬件描述語(yǔ)言,英文全稱為 Hardware Description Language,簡(jiǎn)稱 HDL, HDL 是一種用形式化方法來(lái)描述數(shù)字電路和數(shù)字邏輯系統(tǒng)的語(yǔ)言。設(shè)計(jì)工程師可以使用這種語(yǔ)言來(lái)表述自己的設(shè)計(jì)思路,通過(guò)利用 EDA 工具進(jìn)行仿真、自動(dòng)綜合到門級(jí)電路,最終在 ASIC 或 FPGA 實(shí)現(xiàn)其功能。

以 2 輸入的與門為例來(lái)對(duì)比原理圖設(shè)計(jì)方法與 HDL 設(shè)計(jì)方法之間的區(qū)別, 在傳統(tǒng)的設(shè)計(jì)方法中設(shè)計(jì) 2 輸入與門可能需到標(biāo)準(zhǔn)器件庫(kù)中調(diào)用 74 系列的器件,但在硬件描述語(yǔ)言中“ &”就是一個(gè)與門的形式描述,“ C = A & B”就是一個(gè) 2 輸入與門的描述。而“ &”就代表了一個(gè)與門器件。

硬件描述語(yǔ)言發(fā)展至今已有二十多年歷史,當(dāng)今業(yè)界的標(biāo)準(zhǔn)中( IEEE 標(biāo)準(zhǔn))主要有 VHDL 和Verilog HDL 這兩種硬件描述語(yǔ)言。 本書采用的是 VerilogHDL 硬件描述語(yǔ)言,接下來(lái)著重對(duì)其發(fā)展的歷史及特點(diǎn)進(jìn)行介紹。

Verilog HDL 語(yǔ)言最初是在 1983 年由 Gateway Design Automation 公司為其模擬器產(chǎn)品開發(fā)的硬件建模語(yǔ)言, 當(dāng)時(shí)這只是公司產(chǎn)品的專用語(yǔ)言。隨著公司模擬、仿真器產(chǎn)品的廣泛使用, Verilog HDL 作為一種實(shí)用語(yǔ)言逐漸為眾多設(shè)計(jì)者所接受。 1990 年一次致力于增加語(yǔ)言普及性的活動(dòng)中,Verilog HDL 語(yǔ)言被推向公眾領(lǐng)域從而被更多人熟知。

Open Verilog International( OVI)是促進(jìn) Verilog 發(fā)展的國(guó)際性組織。 1992 年, OVI 決定致力于推廣 Verilog OVI 標(biāo)準(zhǔn)成為 IEEE 標(biāo)準(zhǔn)。這一推廣最后獲得成功, Verilog 語(yǔ)言于 1995 年成為IEEE 標(biāo)準(zhǔn),稱為 IEEE Std1364-1995。 其完整標(biāo)準(zhǔn)在 Verilog 硬件描述語(yǔ)言參考手冊(cè)中有詳細(xì)描述。

Verilog HDL 語(yǔ)言具有許多 優(yōu)點(diǎn),例如 Verilog HDL 語(yǔ)言提供了編程語(yǔ)言接口,通過(guò)該接口可以在模擬、驗(yàn)證期間從設(shè)計(jì)外部訪問(wèn)設(shè)計(jì),包括模擬的具體控制和運(yùn)行。 Verilog HDL 語(yǔ)言不僅定義了語(yǔ)法,而且對(duì)每個(gè)語(yǔ)法結(jié)構(gòu)都定義了清晰的模擬、仿真語(yǔ)義 。因此,用這種語(yǔ)言編寫的模型能夠使用 Verilog 仿真器進(jìn)行驗(yàn)證。 Verilog HDL 提供了擴(kuò)展的建模能力,其中許多擴(kuò)展最初很難理解,但是 Verilog HDL 語(yǔ)言的核心子集非常易于學(xué)習(xí)和使用,這對(duì)大多數(shù)建模應(yīng)用來(lái)說(shuō)已經(jīng)足夠。當(dāng)然,完整的硬件描述語(yǔ)言足以對(duì)從最復(fù)雜的芯片到完整的電子系統(tǒng)進(jìn)行描述。

————————————————

版權(quán)聲明:本文為CSDN博主「原來(lái)如此呀」的原創(chuàng)文章,遵循CC 4.0 BY-SA版權(quán)協(xié)議,轉(zhuǎn)載請(qǐng)附上原文出處鏈接及本聲明。

原文鏈接:https://blog.csdn.net/Royalic/article/details/121146033

-

硬件電路

+關(guān)注

關(guān)注

39文章

244瀏覽量

29316 -

數(shù)字邏輯

+關(guān)注

關(guān)注

0文章

74瀏覽量

16699 -

CAE

+關(guān)注

關(guān)注

0文章

77瀏覽量

23498

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA技術(shù)的發(fā)展歷史和動(dòng)向

Xilinx FPGA無(wú)痛入門,海量教程免費(fèi)下載

剛開始自學(xué)FPGA和Verilog求教一個(gè)入門問(wèn)題。。。

FPGA入門之ModelSim的安裝步驟

FPGA雙沿發(fā)送之Verilog HDL實(shí)現(xiàn) 精選資料推薦

FPGA雙沿采樣之Verilog HDL實(shí)現(xiàn) 精選資料分享

Verilog HDL作為現(xiàn)在最流行的FPGA開發(fā)語(yǔ)言 是入門的基礎(chǔ)

FPGA的Verilog學(xué)習(xí)教程課件免費(fèi)下載

Verilog HDL語(yǔ)言的發(fā)展歷史和能力綜述

FPGA CPLD中的Verilog設(shè)計(jì)小技巧

FPGA入門之Verilog的歷史

FPGA入門之Verilog的歷史

評(píng)論