引言

這些高選擇性蝕刻工具能夠在不損壞設備其他部分的情況下沿任何方向(各向同性)去除材料。在某些情況下,高選擇性蝕刻工具還可以在一個方向(各向異性)去除材料。今天,一些現有的蝕刻工具可以在一定程度上執行選擇性蝕刻,但它們在這方面的能力有限,無法在高級節點上創建新的器件結構。

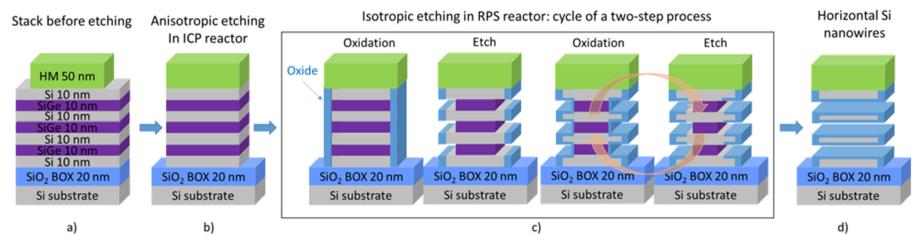

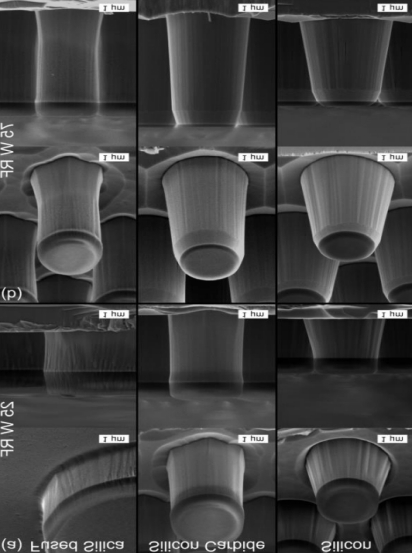

圖 1:從 finFET 到 GAA 的過渡推動了關鍵的各向同性選擇性蝕刻要求

蝕刻是晶圓廠中必不可少的工藝。在一個簡單的工藝流程中,系統將二氧化硅材料沉積在晶圓上。然后光刻系統在晶圓上每個芯片的材料上繪制微小特征,蝕刻工具去除每個芯片上不需要的材料以創建各種結構,目標是埃級精度(1? = 0.1nm)。(江蘇英思特半導體科技有限公司)

基本上,先進的蝕刻工具是帶有腔室的獨立系統。在操作中,晶片被插入腔室中。在一種類型的蝕刻中,等離子體——一種電離氣體——在腔室中產生。“首先,我們制造等離子體。電子撞擊氣體分子,這會產生離子和更多的電子。它們還會產生自由基。自由基成為在等離子蝕刻系統中執行化學蝕刻的物質。這些自由基擴散到晶圓表面。它可能會與一種材料發生反應,但不會與另一種材料發生反應。最后,你有一個蝕刻。結果是各向同性過程。 如果化學成分合適,它可以具有很高的選擇性。基本上,自由基是一個原子、分子或離子。并非所有芯片工藝都需要高選擇性蝕刻。在芯片生產中,許多蝕刻步驟都很簡單,并且使用現有的蝕刻工具。對于要求更高的芯片工藝,蝕刻供應商提供了涉及更復雜工具的各種選項。高選擇性蝕刻就是這樣一種選擇。使用專有的化學物質,具有這些功能的蝕刻工具可以去除目標材料,而無需修改或去除周圍的層。(江蘇英思特半導體科技有限公司)

蝕刻模式

在 IC 行業的早期,芯片制造商自己制造設備。在那些日子里,蝕刻工藝是在通風罩下的水槽中進行的。基本上,將晶圓浸入裝滿化學蝕刻劑的水槽中,然后進行沖洗。這去除了晶圓上的材料。

早期,蝕刻技術演變為兩個部分——濕法蝕刻和干法蝕刻。在一個系統中,濕法蝕刻通過將晶圓浸沒在液體溶液中來去除材料。

干法蝕刻是兩個市場中較大的一個,廣泛用于當今芯片的生產。干法蝕刻分為三個部分或模式——等離子蝕刻、反應離子蝕刻 (RIE) 和濺射蝕刻(又名離子束蝕刻)。每種模式用于不同的應用。

從技術上講,選擇性蝕刻是一種應用,而不是一個單獨的類別。它適合濕法和干法蝕刻類別。在所有情況下,目標都是在晶圓上執行具有良好均勻性的精確蝕刻。

圖2:各向同性或多向蝕刻(頂部)與各向異性或定向蝕刻

ALE 與選擇性蝕刻

許多高級芯片都需要高度選擇性蝕刻。多年來,半導體行業為存儲器和邏輯開發了新的復雜設備。從 2011 年開始,一些代工供應商開始提供使用最先進的finFET晶體管的先進工藝。IC 供應商圍繞 finFET 開發了芯片。如今,代工客戶正在運送采用 16 納米/14 納米、7 納米和 5 納米工藝節點的 finFET 的芯片。3nm finFET 正在研發中。此外,在 3nm 和/或 2nm,一些代工廠將遷移到環柵,這是比 finFET 功耗更低的更快晶體管。但 GAA FET 也更昂貴且更難制造。

圖3:Lam 的 Selis-Prevos 系統在納米片 FET 和其他工藝中蝕刻 SiGe/Si 堆棧__。__

應用

高選擇性蝕刻有多種應用。例如,使用各向異性高選擇性蝕刻形成自對準觸點。在芯片中,觸點是將晶體管與設備中的第一層銅互連連接起來的微小結構。基本上,蝕刻工具修整薄膜或材料以形成所需的結構形狀。該工藝可用于 finFET 和 GAA。GAA 中還使用了其他選擇性蝕刻工藝。在 3nm 和/或 2nm 工藝節點,領先的代工廠及其客戶最終將遷移到稱為納米片 FET的 GAA 晶體管類型。納米片FET是旋轉90度的 finFET,產生水平堆疊的鰭片,每個鰭片之間有垂直柵極材料。每個類似于薄片的鰭都是一個通道。(江蘇英思特半導體科技有限公司)

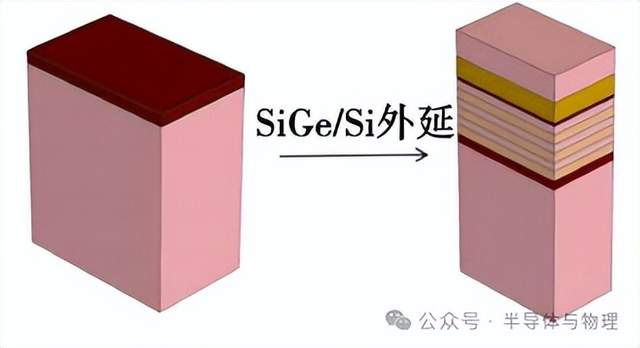

為了在晶圓廠制造納米片,外延工具在基板上沉積超薄的硅鍺 (SiGe) 和硅交替層,形成超晶格結構。這種結構可能具有三層、五層或更多層的每種材料。

在超晶格結構中圖案化和蝕刻微小的垂直鰭。然后,形成內間隔物。為此,超晶格結構中 SiGe 層的外部凹陷,然后填充介電材料。接下來,形成源極/漏極。然后,去除超晶格結構中的 SiGe 層,留下構成通道的硅基層或片。最后,通過沉積高k電介質和金屬柵極材料形成柵極。每一步都會帶來一些挑戰,尤其是內部墊片和通道釋放過程。(江蘇英思特半導體科技有限公司)

審核編輯 黃宇

-

芯片

+關注

關注

456文章

51170瀏覽量

427261 -

半導體

+關注

關注

334文章

27703瀏覽量

222637 -

晶圓

+關注

關注

52文章

4973瀏覽量

128315 -

蝕刻

+關注

關注

9文章

419瀏覽量

15508

發布評論請先 登錄

相關推薦

遠程等離子體選擇性蝕刻的新途徑

高通下一代頂級SoC驍龍855,以打造下一代5G設備

【MPS電源評估板試用申請】下一代接入網的芯片研究

Qualcomm 推出下一代物聯網專用蜂窩技術芯片組!精選資料分享

中興選擇Tundra公司PCI Express產品創建下一代

蘋果為下一代芯片做技術準備

東芝推出支持下一代內容安全技術SeeQVault?的橋接芯片

SiGe與Si選擇性刻蝕技術

為下一代芯片推出高選擇性蝕刻

為下一代芯片推出高選擇性蝕刻

評論