MOSFET等開關器件可能會受各種因素影響而失效。因此,不僅要準確了解產品的額定值和工作條件,還要全面考慮電路工作中的各種導致失效的因素。本系列文章將介紹MOSFET常見的失效機理。

什么是SOA(Safety Operation Area)?

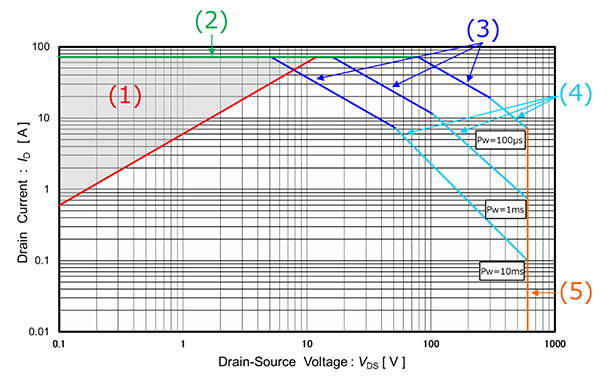

SOA是“Safety Operation Area”的縮寫,意為“安全工作區”。要想安全使用MOSFET,就需要在SOA范圍內使用MOSFET,超過這個范圍就有可能造成損壞。在SOA范圍之外工作時造成的損壞稱為“SOA失效”。例如,SJ MOSFET(Super Junction MOSFET)R6024KNX的SOA如下所示:

SJ MOSFET R6024KNX的SOA

SOA由縱軸上的漏極電流ID和橫軸上的漏源電壓VDS來表示。也就是說,VDS、ID及它們的乘積(功率損耗PD)、以及二次擊穿區決定了MOSFET的安全工作范圍。另外,施加功率的脈沖寬度PW也是決定SOA的重要因素。SOA劃分為圖中所示的(1)~(5)個區域。

SOA的區域劃分、限制以及與失效之間的關系

下面介紹一下圖中的區域(1)~(5)。

■區域(1):漏極電流ID受MOSFET的導通電阻RDS(ON)限制的區域

是指即使施加的VDS小于絕對最大額定值,ID也會受到RDS(ON)限制的區域。根據歐姆定律I=V/R,ID只能流到紅線位置。※圖中的區域是VGS=10V時的示例

■區域(2):由施加脈沖時漏極電流的絕對最大額定值IDP決定的區域

(2)的綠線是規格書中規定的IDP的絕對最大額定值。當然,絕對最大額定值是絕對不能超過的,因此當IDP超過該值時是無法使用的。如果在超過該值的范圍(電流值)使用,由于超出了保證的工作范圍,因此可能會造成損壞。

■區域(3):熱限制區域

這是由MOSFET的容許損耗PD決定的區域。受施加功率的脈沖寬度PW和瞬態熱阻的限制。只要在該范圍內,Tj通常不會超過絕對最大額定值TjMAX,因此可以安全使用。但是請注意,該線會因環境溫度、MOSFET的實際安裝條件和散熱條件等因素而異。此外,作為開關使用MOSFET時,可能會瞬間被施加高電壓和大電流,因此即使在開關的瞬態狀態下也必須注意不要超過區域(3)的限制。

■區域(4):二次擊穿區域

當在施加高電壓的狀態下流過電流時,元器件內部的局部可能會流過大電流并造成損壞,這稱為“二次擊穿”。這條線是用來防止造成二次擊穿狀態的限制線。與區域(3)的熱限制區域一樣,二次擊穿區域也受環境溫度等因素的影響。

■區域(5):由MOSFET漏源電壓的絕對最大額定值VDSS決定的區域

這是規格書中規定的受VDSS限制的區域,如果超過這個區域,就可能發生擊穿并造成損壞。需要注意的是,由反激電壓和寄生電感引起的電壓變化,可能會瞬間超過該限制。

什么是雪崩擊穿

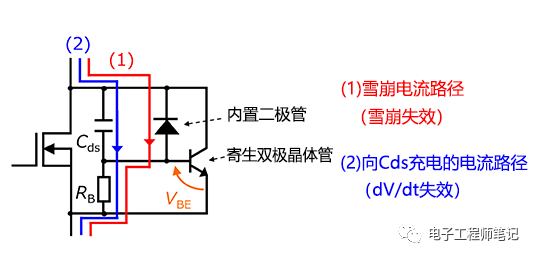

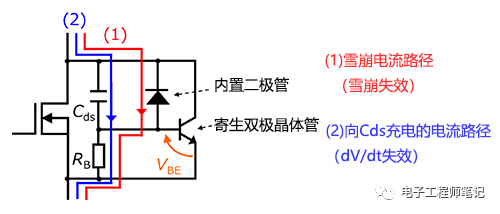

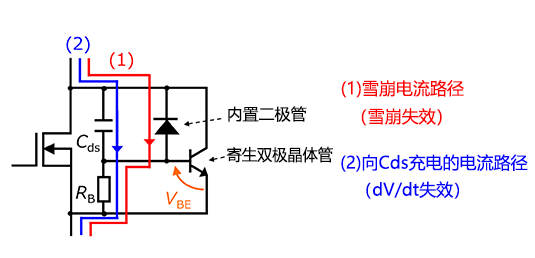

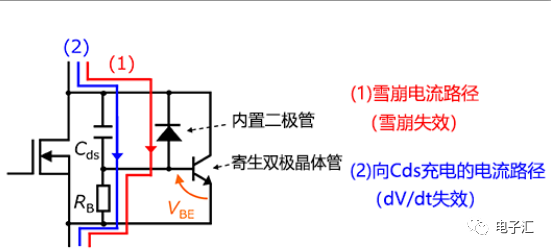

當向MOSFET施加高于絕對最大額定值BVDSS的電壓時,就會發生擊穿。當施加高于BVDSS的高電場時,自由電子被加速并帶有很大的能量。這會導致碰撞電離,從而產生電子-空穴對。這種電子-空穴對呈雪崩式增加的現象稱為“雪崩擊穿”。在這種雪崩擊穿期間,與 MOSFET內部二極管電流呈反方向流動的電流稱為“雪崩電流IAS”,參見下圖(1)。

MOSFET的雪崩失效電流路徑示意圖(紅色部分)

雪崩失效:短路造成的失效

如上圖所示,IAS會流經MOSFET的基極寄生電阻RB。此時,寄生雙極型晶體管的基極和發射極之間會產生電位差VBE,如果該電位差較大,則寄生雙極晶體管可能會變為導通狀態。一旦這個寄生雙極晶體管導通,就會流過大電流,MOSFET可能會因短路而失效。

雪崩失效:熱量造成的失效

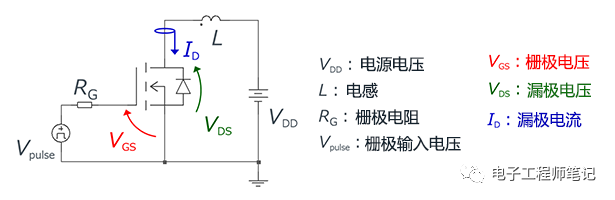

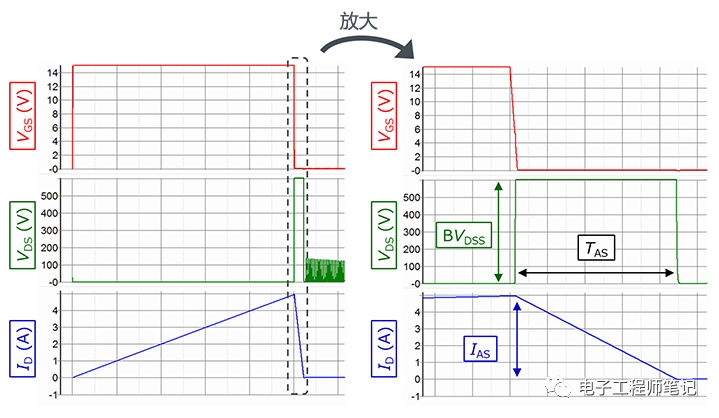

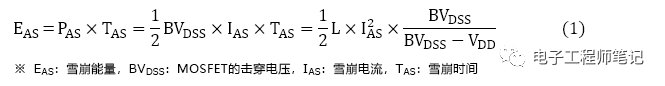

在雪崩擊穿期間,不僅會發生由雪崩電流導致寄生雙極晶體管誤導通而造成的短路和損壞,還會發生由傳導損耗帶來的熱量造成的損壞。如前所述,當MOSFET處于擊穿狀態時會流過雪崩電流。在這種狀態下,BVDSS被施加到MOSFET并且流過雪崩電流,它們的乘積成為功率損耗。這種功率損耗稱為“雪崩能量EAS”。雪崩測試電路及其測試結果的波形如下圖所示。此外,雪崩能量可以通過公式(1)來表示。

雪崩測試的電路簡圖

雪崩測試中MOSFET的電壓和電流波形

雪崩能量公式

一般情況下,有抗雪崩保證的MOSFET,在其規格書中會規定IAS和EAS的絕對最大額定值,因此可以通過規格書來了解詳細的值。在有雪崩電流流動的工作環境中,需要把握IAS和EAS的實際值,并在絕對最大額定值范圍內使用。

引發雪崩擊穿的例子包括反激式轉換器中的MOSFET關斷時的反激電壓和寄生電感引起的浪涌電壓等。針對反激電壓引起的雪崩擊穿,對策包括在設計電路時采用降低反激電壓的設計或使用具有更高耐壓性能的MOSFET。而針對寄生電感引起的雪崩擊穿,改用引腳更短的封裝的MOSFET或改善電路板布局以降低寄生電感等都是比較有效的措施。

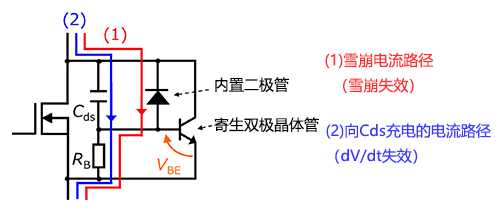

什么是dV/dt失效

如下圖(2)所示,dV/dt失效是由于MOSFET關斷時流經寄生電容Cds的瞬態充電電流流過基極電阻RB,導致寄生雙極晶體管的基極和發射極之間產生電位差VBE,使寄生雙極晶體管導通,引起短路并造成失效的現象。通常,dV/dt越大(越陡),VBE的電位差就越大,寄生雙極晶體管越容易導通,從而越容易發生失效問題。

MOSFET的dV/dt失效電流路徑示意圖(藍色部分)

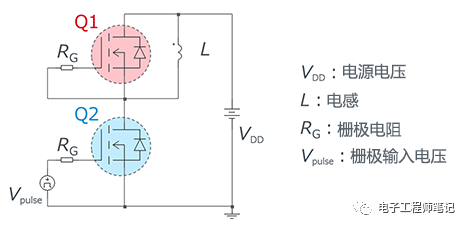

此外,在逆變器電路或Totem-Pole PFC等上下橋結構的電路中,反向恢復電流Irr會流過MOSFET。受該反向恢復電流影響的dV/dt,可能會使寄生雙極晶體管誤導通,這一點需要注意。dV/dt失效與反向恢復特性之間的關系可以通過雙脈沖測試來確認。雙脈沖測試的電路簡圖如下:

雙脈沖測試的電路簡圖

關于在雙脈沖測試中的詳細情況,請參考R課堂基礎知識 評估篇中的“通過雙脈沖測試評估MOSFET的反向恢復特性”。

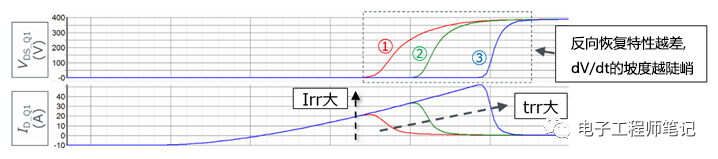

dV/dt和反向恢復電流的仿真結果如下圖所示。設MOSFET①~③的柵極電阻RG和電源電壓VDD等電路條件相同,僅反向恢復特性不同。圖中列出了Q1從續流工作轉換到反向恢復工作時的漏源電壓VDS和漏極電流(內部二極管電流)ID。

雙脈沖測試的仿真結果

一般情況下,與MOSFET①相比,MOSFET③可以說是“反向恢復特性較差(Irr和trr大)”的產品。從這個仿真結果可以看出,反向恢復特性越差,dV/dt的坡度就越陡峭。這一點通過流經電容器的瞬態電流通常用I=C×dV/dt來表示也可以理解。此外,在上述仿真中,Irr的斜率(di/dt)均設置為相同條件,但當di/dt陡峭時,dV/dt也會變陡峭。

綜上所述,可以說,在橋式電路中使用MOSFET時,反向恢復特性越差的MOSFET,發生MOSFET的dV/dt失效風險越大。

至此,我們已經介紹了MOSFET的SOA失效、MOSFET的雪崩失效和MOSFET的dV/dt失效。要想安全使用MOSFET,首先不能超過MOSFET規格書中的絕對最大額定值,另外,了解這些MOSFET的失效機理之后再進行電路設計和工作條件設置是非常重要的。

審核編輯:湯梓紅

-

二極管

+關注

關注

147文章

9702瀏覽量

167559 -

MOSFET

+關注

關注

147文章

7240瀏覽量

214262 -

失效機理

+關注

關注

2文章

27瀏覽量

11686 -

SOA

+關注

關注

1文章

293瀏覽量

27572 -

開關器件

+關注

關注

1文章

192瀏覽量

16921

原文標題:總結:MOSFET的失效機理

文章出處:【微信號:電子工程師筆記,微信公眾號:電子工程師筆記】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

MOSFET的失效機理

MOSFET的失效機理:什么是SOA(Safety Operation Area)失效

MOSFET的失效機理:什么是雪崩失效

MOSFET的失效機理:什么是dV/dt失效

MOSFET的失效機理

MOSFET的失效機理

評論