1. 背景介紹:

在TI最新一代JacintoTM 7處理器芯片中,為了保證客戶系統安全以及功能隱私,保證應用鏡像不被惡意篡改、復制以及刪除,TI為每一顆JacintoTM 7 家族的SoC芯片都提供了HS(high security)的芯片類型。

而JTAG作為嵌入式開發過程中必不可少的調試接口,在應用開發以及產品發布階段,推薦進行不同的處理,從而避免第三方通過JTAG接口對產品系統進行攻擊從而造成損失。針對這種考慮,在GP和HS芯片中,JTAG接口具有不同的權限,如下表1所示:

表 1 不同芯片類型中的JTAG狀態

| 芯片類型 | 芯片狀態 | M3 JTAG 狀態 | 其它核心JTAG 狀態 |

| General Purpose (GP) | GP | Open | Open |

| High Security (HS) | HS-FS | Closed | Open |

| High Security (HS) | HS-SE | Closed | Controlled |

本文旨在介紹并幫助開發人員在HS-SE芯片中實現對JTAG的控制,進而保證產品的安全以及隱私性

2. 測試條件:

DRA821 EVM開發板

開發環境:Linux Ubuntu 18.04

值得一提的是,本文基于DRA821 HS-SE芯片進行測試以及介紹,但此方法適用于JacintoTM 7家族其它系列芯片,例如TDA4x系列SoC。

3. JTAG Debug Unlock的兩種方法及適用場景

一般來說,JacintoTM 7家族HS-SE系列SoC中,如上表1所示,M3/M4F核心的JTAG默認關閉且不能打開,從而確保DMSC核心的安全,進而保證芯片內部的時鐘電源安全。

而對于其它核心,例如R5F/A72/DSP等等,則可以通過JTAG Debug的預加鎖/預解鎖以及實時解鎖兩種方案來實現對JTAG的控制。

JTAG Debug的預加鎖/預解鎖方案通過直接對各個核心鏡像的x509證書進行授權,使其在運行時在芯片內部直接進行對JTAG的加鎖/解鎖,從而實現對JTAG的控制。其適用于能夠對鏡像進行實時更新的開發環境。

JTAG Debug的實時解鎖方案默認對JTAG進行鎖死,然后通過外部JTAG口或者TISCI等方式向芯片發送特定的解鎖證書,從而實現對指定核心的JTAG進行解鎖;芯片下電后,會繼續保持JTAG死鎖。其適用于對鏡像文件更新受限的開發環境。

總的來說,相對于預加鎖/解鎖方案,實時解鎖方案的安全性更高,部署成功后操作更加便捷且高效;相對的,預加鎖/解鎖方案在前期部署工作上會更加簡單。

4. JTAG Debug的預加鎖/預解鎖方案

所有在HS-SE芯片中執行的binary,都需要對鏡像進行簽名/加密才可正常運行,具體的流程可以參考應用手冊“SPRAD04“中的第二章節。而JTAG Debug的預加鎖/預解鎖則是在對binary進行簽名加密生成x509證書時,通過配置默認的debug extension來設置芯片JTAG Debug的權限。以SBL為例,在 /packages/ti/build/makerules/common.mk文件中,當開發人員執行make sbl_mmcsd_img_hs編譯SBL時,會調用下述指令對SBL進行簽名并設置debug extension的權限。

其中“DBG_FULL_ENABLE”代表默認將JTAG Debug設置為full,即打開對應核心的所有debug權限,即預解鎖。若刪除此編譯選項,即默認JTAG Debug設置為關閉,即預加鎖。

5. JTAG Debug的實時解鎖方案

出于安全性考慮,在實時解鎖方案中,可以首先默認配置JTAG是鎖死狀態。以DRA821 SBL為例,在SDK8.2中,在SBL的Makefile中默認會配置x509證書的debug extension并設置其為FULL權限,即MCU1_0 JTAG enable狀態,所以需要將其先進行關閉并刪除debug extension,改動如下patch所示:

其次,需要在板級配置文件中,設置其為支持外部實時解鎖JTAG Debug,其改動如下patch所示:

其中變量allow_jtag_unlock 等于0x5A代表支持外部進行實時的JTAG unlock,同樣的,JTAG Debug中其它變量的取值以及對應含義如下圖1所示。

圖 1 boardcfg中Secure Debug配置中的參量取值及含義

修改完成之后,需要重新編譯boardcfg以及SBL等文件:

5.1 JTAG Debug的實時解鎖流程:

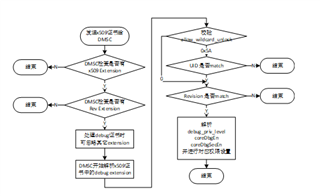

外部設備通過JTAG來解鎖對應核心JTAG調試權限時,首先需要將設計過的且符合ANS.1規則的x509證書傳輸給DMSC,DMSC會解析此x509證書,并經過校驗UID,revision等通過之后,對JTAG Debug進行對應的權限解鎖。其大致流程如下圖2所示:

圖 2 JTAG Debug的實時解鎖流程

5.2 創建x509調試證書配置文件:

如5.1中圖2所示的,首先要編寫一個能夠通過DMSC檢查,并通過各項UID,revision等校驗的x509證書,而在生成證書之前,首先需要按照ANS.1的規則編寫一個配置文件。這樣才能保證生成的調試證書能夠被DMSC正確識別并進行配置。如下所示,為在DRA821中的x509調試證書配置文件模板。

值得注意的是,在不同芯片平臺(TDA4x或DRA8x),亦或同一芯片平臺的不同UID芯片中,進行不同核心(R5F/A72/DSP)的JTAG Unlock權限配置,開發人員只需對【debug】下的內容進行更改。下面將對【debug】中的四個配置參數含義以及設置原則進行介紹:

a. UID獲取

UID是對于每顆芯片的獨一無二的標志,在JacintoTM 7家族中,其為256bit的64個16進制數構成。一般來說,獲取UID的方法有三種:

在UART boot模式下通過MCU UART獲取,并經過腳本解析得到。

利用dbgauth工具通過命令行獲取。

利用TISCI在代碼中獲取TISCI_MSG_GET_SOC_UID

其中第一種方法可參考應用手冊“SPRAD04“中的第四章節獲取。

其中第二中方法,將在本文5.4小節中介紹。

第三種方法參照TISCI手冊。

開發人員只需根據自身開發環境選擇其一即可。在獲取到UID之后,只需將其替換到 【debug】規則下的deviceUID中即可。

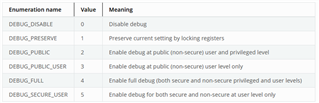

b. DebugType配置原則

DebugType為一個32bit數,其中低16bit數為debug level權限控制,高16bit目前為保留位,默認取全0即可。其中debug level的取值以及對應的含義如圖3所示:

圖 3 debug level取值及其含義

c. coreDbgEn配置原則

coreDbgEn控制哪些核心的non-secure debug將被打開,以Processor ID的形式列出,以DRA821為例,其內部所有處理器核心的processor ID如下所示:

圖 4 DRA821芯片內部處理器核心對應ID取值

d. coreDbgSecEn配置原則

coreDbgSecEn控制哪些核心的secure debug將被打開,以Processor ID的形式列出,以DRA821為例,其內部所有處理器核心的processor ID同樣可參照圖4所示。

5.3 通過x509配置文件生成x509證書并簽名:

開發人員根據需求設計完配置文件后,需要適用openssl來生成對應的x509證書,并適用自己的密鑰對此證書進行簽名,才能保證此證書能被對應的HS-SE板子驗簽并解析。

其中“-key”后需要保持和開發人員HS-SE板子中燒寫的密鑰保持一致;“-out”后的文件即為將生成的x509證書文件;“-config”中即為在本文5.2小節中設計得到的配置文件。

5.4 CCS環境及dbgauth工具搭建:

在使用外部JTAG進行實時解鎖JTAG Debug時,需要使用CCS中的組件工具dbgauth。開發人員需要安裝CCS,建議安裝CCS 9.3及其之后版本:https://www.ti.com/tool/CCSTUDIO

安裝完畢后,按照下列步驟來配置環境:

針對芯片類型新建CCS configuration并進行launch,完畢后會在~/.ti/《ccs_version》/0/0/BrdDat/目錄下有對應的配置文件dat。

同樣的,安裝后dbgauth工具會在《ccs install》/ccs/ccs_base/common/uscif/目錄下。

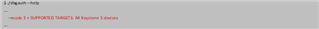

需要確認當前版本的dbgauth是支持JacintoTM 7系列SoC的K3架構的:

至此,環境搭建完畢。

5.5 利用證書進行實時JTAG解鎖:

基于5.4小節建立的環境,可通過dbgauth工具來獲取設備UID,以及實時解鎖JTAG等操作。首先需要將5.1小節中編譯得到的SBL以及TIFS放到boot media中,確認MCU1_0以及DMSC已經正常運行起來,例如獲取UID的命令以及打印為:

此時如果通過CCS直接鏈接MCU1_0的核心是無法連接的,因為默認的JTAG配置為lock狀態。

通過5.3小節中生成的證書進行JTAG解鎖的命令及打印為:

執行完上述指令后,JTAG Debug將被打開,可以通過CCS對MCU1_0進行連接。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19407瀏覽量

231185 -

芯片

+關注

關注

456文章

51170瀏覽量

427255 -

soc

+關注

關注

38文章

4204瀏覽量

219093

發布評論請先 登錄

相關推薦

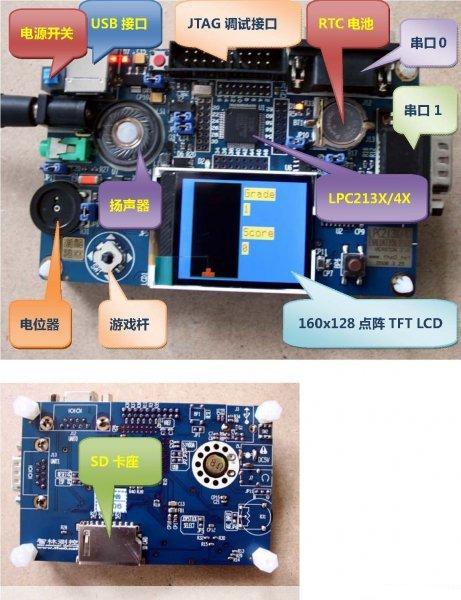

可以實現的JTAG調試器的嵌入式系統

Trimedia DSP芯片JTAG接口的仿真器設計

ARM JTAG調試的基本原理

ARM JTAG 調試原理

JTAG調試快速入門

基于ARM開發的JTAG仿真器的調試設計

基于JTAG的ARM芯片系統調試

《ARM JTAG 調試原理》下載

digilent JTAG-HS3編程電線 介紹

JacintoTM 7家族HS芯片中的JTAG加解鎖控制

Jacinto 7系列HS芯片中的JTAG調試控制

Jacinto 7系列HS芯片中的JTAG調試控制

評論