1、門電路

數字電路的基礎就是門電路,數字電路中用以實現基本邏輯運算和符合邏輯運算的單元電路稱為門電路,在電子電路中,用高低電平分別表示1和0兩種狀態,反映到電子電路中實際就是晶體管的導通與截止,但是單開關電路的主要缺點是功耗比較大,為了克服這個缺點,將單開關電路中的電阻用另外的一個開關代替。

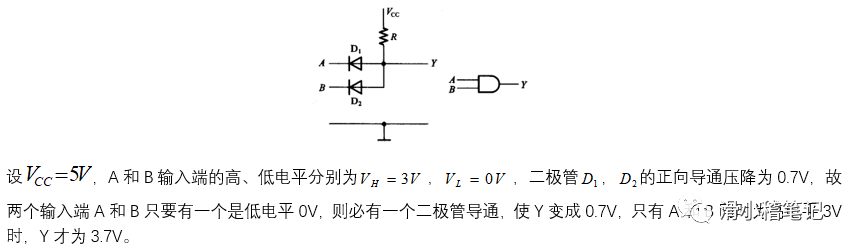

(1)二極管與門

最簡單的與門可以采用二極管和電阻構成,下圖所示是一個二輸入的與門電路。

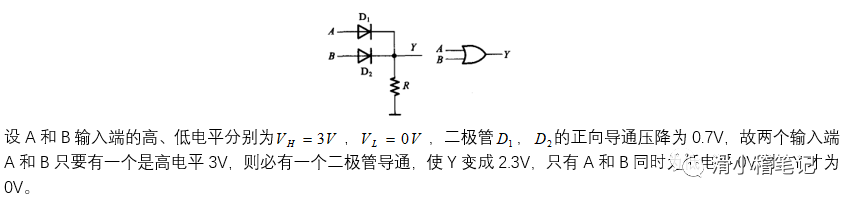

(2)二極管或門

最簡單的或門也可以采用二極管和電阻構成,下圖所示是一個二輸入的或門電路。

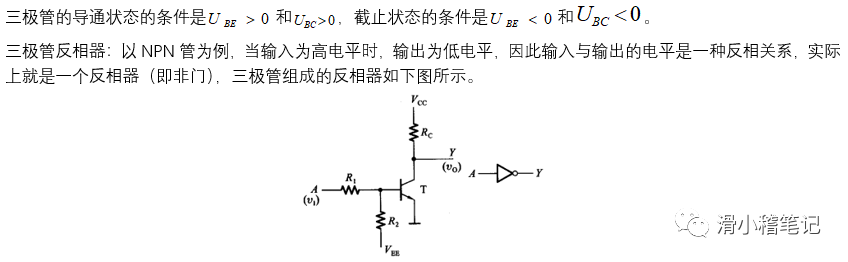

(3)TTL門電路

TTL門電路就是采用雙極性晶體管組成的門電路,之前的模擬電路可以知道,三極管有三種工作狀態,導通,放大和截止,模擬電路中經常利用三極管的放大特性,在數字電路中則經常利用三極管的導通和截止狀態,我們可以來回顧一下模擬電路所學的知識,

(4)CMOS門電路

與TTL門電路一樣,CMOS也有三個工作狀態,即導通,截止和可變電阻狀態,數字電路中經常用到CMOS的導通和截止狀態,并且現在CMOS的場合也逐漸取代了TTL的場合,這是因為CMOS的結構是電壓型驅動,且由于柵極與源極的電阻無窮大(二氧化硅導致的),所以CMOS天生就比三極管要省電的多,并且耐壓范圍寬,便于制作,所以在現在的集成門電路中,CMOS變成了集成電路的主體。

由于CMOS的柵極和源極之間的電阻接近于無窮大,這就導致了做成門電路時,若柵極懸空,則相當于接高電平,而TTL電路若一個輸入端懸空,則相當于接低電平,所以在選用門電路的時候,必須要根據芯片設計的晶體管還是CMOS來設計電路。

盡管CMOS門電路輸入端懸空為高電平,但是由于CMOS的結構導致了制作成的門電路不用的輸入端不允許懸空,因為即使很小的靜電附加在柵極上也會產生高壓導致CMOS擊穿。

(5)漏極開路門OD門

在CMOS電路中,為了滿足輸出電平變化,吸收大負載電流以及實現線與連接等需要,有時候需要將輸出級電路改成一個漏極開路輸出的MOS管,組成漏極開路輸出(Open—DrainOutput)門電路,簡稱OD門。OD輸出與非門的電路結構如下圖所示。菱形下方的橫線代表輸出低電平時為低輸出電阻。

OD門工作時必須將輸出端經過上拉電阻接到電源上。

(6)CMOS傳輸門

利用P溝道MOS管和N溝道MOS管的互補特性可以組成CMOS傳輸門,CMOS傳輸門如同CMOS反相器一樣,也是構成電路的一種基本邏輯電路,CMOS傳輸門的電路結構和邏輯符號如下圖所示。

由于CMOS的兩個開關管的結構形式是對稱的,因此CMOS傳輸門屬于雙向器件,它的輸入端和輸出端也可以互易使用。

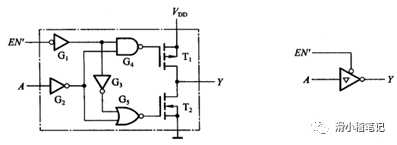

(7)三態門

一般數字電路的門電路只有兩種形態,但是存在一種情況,即數字電路的第三個狀態—高組態,三態輸出反相器的電路結構如下圖所示。

因為這種電路結構總是接在集成電路的輸出端,所以也將這種電路稱為輸出緩沖器(OutputBuffer)。

在一些比較復雜的數字系統中,為了減少各個單元之間的連接數目,希望可以用同一條導線分別傳遞若干個門電路的輸出信號,這時可以采用下圖所示的連接方式。

圖中的G1~Gn均為三態輸出反相器,只要工作過程中控制各個反相器的EN端口輪流等于1,而且任何時候僅有一個等于1,就可以輪流的把各個反相器的輸出信號送到公共的傳輸線—總線上,而互不干擾,這種連接方式稱為總線結構。

利用三態門還可以實現數據的雙向傳輸,當EN為1時,G1工作而G2為高組態,數據D0經過G1反相后送到總線上去,當EN=0時,G2工作而G1為高組態,來自總線的數據D1經過G2反相后送入電路內部。

2、組合邏輯電路設計方法

根據邏輯功能的不同特點,可以將數字電路分為兩大類,即組合邏輯電路(簡稱組合電路,是一種無記憶性質的電路)和時序邏輯電路(簡稱時序電路,是一種具有存儲功能的電路)。這一章節主要討論組合邏輯電路的設計與分析方法。

(1)分析方法:分析一個組合邏輯電路通常是從電路的輸入到輸出逐級寫出邏輯函數式,最后得到表示輸出與輸入關系的邏輯函數式,然后用公式化簡法或卡諾圖化簡法得到函數式的最簡形式,為了使電路的邏輯功能更加直觀,有時還可以將邏輯函數式轉換為真值表的形式。

(2)設計方法:根據給出的實際問題,來設計某種電路完成這個功能,這就是設計組合邏輯電路時要完成的工作,這里的“最簡”是指電路所用器件數最少,器件的種類最少,而且器件之間的連線也最少,組合邏輯電路的設計工作通常可以按照以下步驟進行。

①進行邏輯抽象:根據所需要實現的功能,列寫真值表。

②寫出邏輯函數表達式:根據真值表列寫出邏輯函數表達式。

③選定器件的類型:根據現有的器件,將邏輯函數表達式化為現有器件的邏輯運算。

④將邏輯函數式化簡:這一步是為了用最簡的電路來完成要求的邏輯功能。

⑤根據化簡后的邏輯函數表達式,畫出邏輯電路的連接圖:這一步做完之后,原理性設計已經完成。

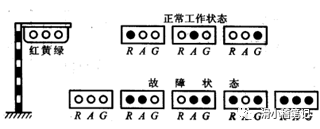

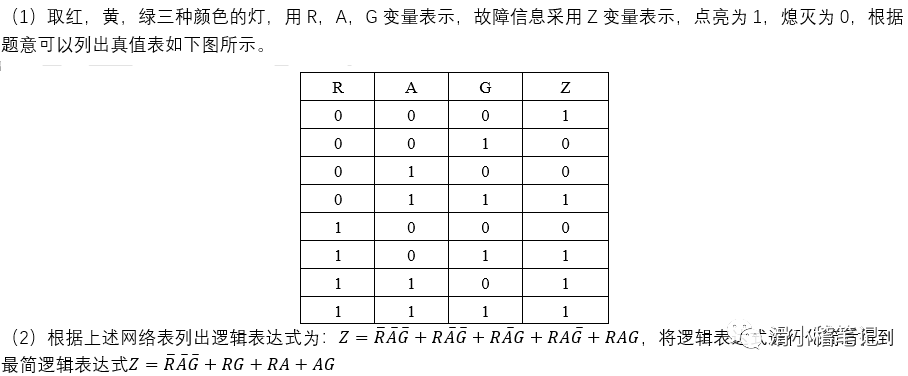

例題分析:設計一個監視交通燈工作狀態的邏輯電路,每一組信號燈均由紅黃綠三種燈組成,正常情況下,任何時刻必有一盞燈亮,而且只允許有一盞燈亮,而當出現其他五種點亮狀態時,電路發生故障,這時要求發出故障信號,以提醒維護人員前去修理。

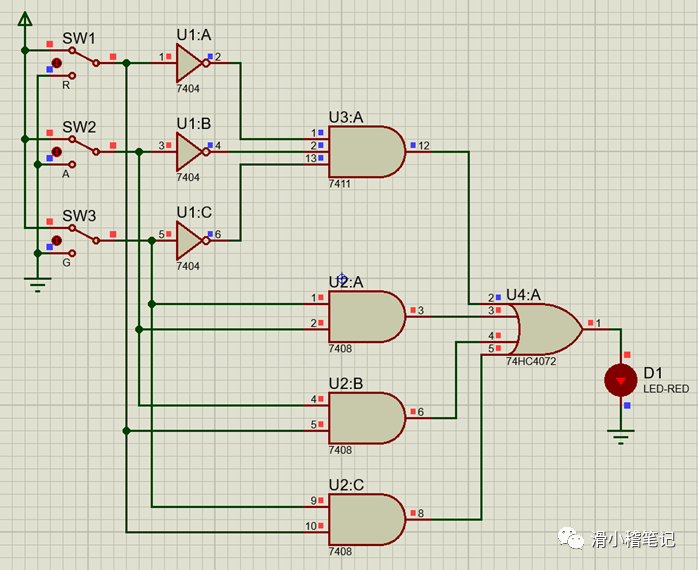

(3)根據邏輯最簡表達式可以畫出最終邏輯電路如下圖所示。

3、編碼器

為了區分一系列不同事物,將其中的每個事物用一個二進制代碼表示,編碼器就是把輸入的每一個高低信號轉換為一個固定的二進制編碼,編碼器可以分為普通編碼器(例如8-3編碼器)和優先編碼器兩大類,在普通編碼器中,任何時刻只允許輸入一個編碼信號,否則將會影響輸出。

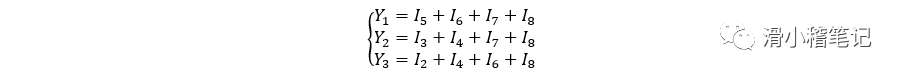

(1) 普通編碼器 (以8-3譯碼器為例):8-3編碼器是將8位二進制轉換為3位二進制代碼的編碼器,具有8個輸入,3個輸出,真值表如下表所示。

| 輸入信號 | 輸出信號 |

|---|---|

| 1 | 0 |

| 0 | 1 |

| 0 | 0 |

| 0 | 0 |

| 0 | 0 |

| 0 | 0 |

| 0 | 0 |

| 0 | 0 |

根據上述真值表可以列寫出邏輯函數表達式,然后化簡得到以下結果

根據邏輯表達式可以繪制出邏輯電路如下圖所示,為了便于設計過程,將8-3編碼器用右邊的元件符號進行表示,形成了芯片74HC148編碼器,其中HC代表的是COMS器件。

(2) 優先編碼器 :在優先編碼器中,允許同時輸入兩個以上的編碼信號,不過在設計時已經將所有的輸入信號按照優先順序排了隊,如果幾個輸入信號同時出現時,只對其中優先權最高的一個進行編碼。

4、譯碼器

譯碼器的邏輯功能是將每個輸入的二進制代碼解釋成對應的輸出高低信號,因此,譯碼器實際是編碼器的逆運算,常用的譯碼器電路有二進制譯碼器,二-十進制譯碼器和顯示譯碼器三大類。

(1) 二進制譯碼器 (以3-8譯碼器為例):實際是8-3譯碼器的逆運算,工作原理與8-3譯碼器的推導過程相同。常見的二進制譯碼器有74HC138譯碼器。

(2) 二-十進制譯碼器 :邏輯功能是將輸入BCD碼的10個代碼變為10個高低電平輸出信號,常見的二-十進制譯碼器有74HC42譯碼器。

(3) 顯示譯碼器 :一般用于將輸入的BCD碼或者二進制代碼變為顯示需要用到的二進制編碼輸出。

5、數據選擇器

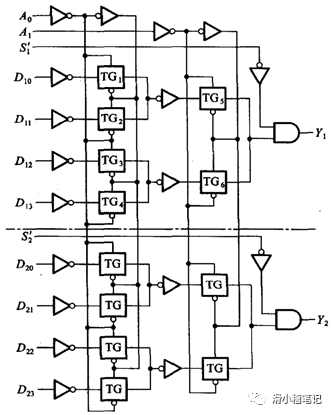

在數字信號的傳輸過程中,需要從一組輸入數據中選出某一個來,這時,就需要用到一種數據選擇器(多路開關)的邏輯電路,以4選1數據選擇器為例,解釋它的工作原理,74HC153是常用的雙4選1數據選擇器芯片,邏輯電路結構如下圖所示。

74HC153包含兩個結構完全相同的4選1數據選擇器,兩個數據選擇器有公共的地址輸入端,而數據輸入端與輸出端完全獨立,通過不同的地址代碼,即和的電平組合,從4個輸入數據中選中需要的一個,并輸出給輸出端Y,圖中的和是附加控制端,用于控制電路工作狀態和擴展功能。

6、加法器

在目前的計算機中,所有的計算都是轉化為若干步加法運算進行的,因此,加法器是構成算術運算器的基本單元,加法器可以分為1位加法器(半加器),全加器,多位加法器和超前進位加法器四種。

(1)半加器

如果不考慮進位問題,只將兩個二進制位想加,稱為半加,實現這種運算的電路稱為半加器,按照二進制加法運算規則可以繪制真值表,其中A和B是兩個加數,S是相加的和,C是高位的進位,真值表如下表所示。

| A | B | S | C |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

半加器的邏輯電路和元件符號如下圖所示,圖a是邏輯電路,圖b則是元件符號。

(2)全加器

在進行2位二進制相加時,除了最低位以外,每一位都應該考慮來自低位的進位,這種三個數相加的電路稱為全加器,根據以上描述可以列出全加器的真值表如下圖所示。其中A,B是兩個相加的二進制數,CI代表進位輸入,S代表相加的結果,CO代表進位輸出。

| 輸入 | 輸出 |

|---|---|

| CI | A |

| 0 | 0 |

| 0 | 0 |

| 0 | 1 |

| 0 | 1 |

| 1 | 0 |

| 1 | 0 |

| 1 | 1 |

| 1 | 1 |

(3)多位加法器

兩個多位數相加時每一位都是帶進位相加的,所以必須采用全加器,只要依次將低位全加器的進位輸出端CO接到高位全加器的進位輸入端CI就可以構成多位加法器。常見的雙全加器是74LS183,74LS183屬于4位加法器,多位全加器的元件符號如下圖所示。

7、競爭-冒險

(1)競爭-冒險的產生原因

在邏輯電路中,輸入端在進行電平跳變的時候,會產生一個瞬時過程,下面詳細解釋這個過程,例程電路如下圖所示。

與門電路中,穩態下無論A=1,B=0還是A=0,B=1,輸出均為Y=0.但是再輸入信號A從1跳變為0時,如果B從0跳變為1,A從1跳變到0,并且A的速度比B的速度慢1ms,那么暫態過程如下表所示

| 時間 | A | B | Y |

|---|---|---|---|

| 0ms | 1 | 0 | 0 |

| 1ms | 1 | 1 | 1 |

| 2ms | 0 | 1 | 0 |

顯然,此時在1ms時間點上Y會輸出1個高電平的窄脈沖,這個脈沖是不符合門電路穩態下的邏輯功能的,因此屬于一種系統內部的噪聲,我們將門電路的輸入信號同時向相反的邏輯電平跳變的現象稱為 **競爭** 。而由于競爭導致產生的尖峰脈沖就稱為 **競爭-冒險** 。

(2)檢查競爭-冒險的方法(適用于手算):在輸入變量每次只有一個狀態的簡單情況下,可以通過化簡邏輯表達式判斷競爭-冒險現象是否存在。如果輸出端門電路的兩個輸入信號A和是輸入變量經過兩個不同的傳輸途徑而來的,那么這種情況下,A的狀態改變時就會產生競爭-冒險現象,因此,只要輸出端的邏輯函數在一定條件下能簡化為或者的形式,則可以判定存在競爭-冒險現象。

(3)消除競爭-冒險的方法

①接入濾波電容:利用電容兩端電壓不能突變的特性,可以在輸入端或者輸出端并聯電容,消除尖峰脈沖。

②引入選通脈沖:在電路中引入選通脈沖,只有當指定的電平加在電路中時,輸入的電平信號才有效,這也是一個消除競爭-冒險現象的辦法。

③修改邏輯設計:采用增加冗余項的方式來消除競爭-冒險現象。

-

門電路

+關注

關注

7文章

199瀏覽量

40260 -

數字電路

+關注

關注

193文章

1629瀏覽量

80822 -

電子電路

+關注

關注

78文章

1227瀏覽量

67034

發布評論請先 登錄

相關推薦

組合邏輯電路的分析與設計-邏輯代數

組合邏輯電路的設計說明

什么是組合邏輯電路 如何使用verilog描述組合邏輯電路

組合邏輯電路

組合邏輯電路

評論