你可能已經(jīng)在智能手機(jī)上播放過成百上千個(gè)視頻了,那么,你有沒有想過當(dāng)你按下“播放”鍵時(shí)發(fā)生了什么?

? 一觸碰那個(gè)小三角形按鍵,便會(huì)立刻發(fā)生很多事。在幾微秒內(nèi),手機(jī)處理器上空閑的計(jì)算內(nèi)核就啟動(dòng)了。與此同時(shí),它們的電壓和時(shí)鐘頻率會(huì)迅速上升,以確保視頻解壓和顯示不會(huì)延遲。同時(shí),在后臺(tái)運(yùn)行任務(wù)的其他內(nèi)核也會(huì)降低速度。電荷會(huì)涌進(jìn)活躍內(nèi)核的數(shù)百萬個(gè)晶體管中,在新閑置的內(nèi)核中則慢得像涓涓細(xì)流。

?這種跳動(dòng)在片上系統(tǒng)(SoC)的處理器中不斷發(fā)生著,被稱為“動(dòng)態(tài)電壓和頻率縮放”(DVFS),它支撐著手機(jī)和筆記本電腦以及服務(wù)器的運(yùn)行。

這一切都是為了平衡計(jì)算的性能和功耗,這對(duì)智能手機(jī)來說尤其具有挑戰(zhàn)性。應(yīng)用DVFS的電路會(huì)力圖確保在電流激增時(shí),時(shí)鐘和電壓水平穩(wěn)定可靠,它們也是最難設(shè)計(jì)的部分之一。 這主要是因?yàn)椋瑫r(shí)鐘產(chǎn)生電路和電壓調(diào)節(jié)電路與智能手機(jī)SoC上的任何東西都不同,它們是模擬電路。得益于半導(dǎo)體制造業(yè)的進(jìn)步,我們已越來越習(xí)慣于每年都會(huì)出現(xiàn)運(yùn)算能力大大提高的新處理器。將一個(gè)數(shù)字設(shè)計(jì)從舊半導(dǎo)體工藝“移植”到新工藝中絕非易事,但與嘗試將模擬電路移植到一個(gè)新工藝上相比,這算不了什么。

實(shí)現(xiàn)DVFS的模擬元件,尤其是一種稱為“低壓差穩(wěn)壓器”(LDO)的電路,并不會(huì)像數(shù)字電路那樣按比例縮小,基本上每一代新產(chǎn)品都必須從頭開始重新設(shè)計(jì)。 如果我們可以用數(shù)字元件來制作LDO或其他模擬電路,那么其移植難度就會(huì)大大降低,從而節(jié)省大量設(shè)計(jì)成本,并且能解放工程師,讓他們?nèi)ソ鉀Q尖端芯片設(shè)計(jì)面臨的其他問題。此外,由此制成的數(shù)字LDO會(huì)比模擬LDO小得多,且在某些方面的表現(xiàn)會(huì)更好。過去幾年,業(yè)界和學(xué)術(shù)界的研究團(tuán)隊(duì)已經(jīng)測(cè)試了至少十幾種設(shè)計(jì),盡管還存在一些缺點(diǎn),但商業(yè)上有用的數(shù)字LDO可能很快就能實(shí)現(xiàn)。

典型的智能手機(jī)SoC是一個(gè)集成奇跡。它在一塊硅片上集成了多個(gè)中央處理機(jī)(CPU)核、一個(gè)圖形處理單元、一個(gè)數(shù)字信號(hào)處理器、一個(gè)神經(jīng)處理單元、一個(gè)圖像信號(hào)處理器、一個(gè)調(diào)制解調(diào)器,以及其他專用邏輯塊。當(dāng)然,提高驅(qū)動(dòng)這些邏輯塊的時(shí)鐘頻率會(huì)提高它們完成工作的速度。不過,要在更高的頻率下工作,也需要更高的電壓。否則,晶體管就無法在處理器時(shí)鐘下一次走動(dòng)之前打開或關(guān)閉。當(dāng)然,更高的頻率和電壓是以耗電為代價(jià)的。因此,根據(jù)完成分配工作(拍攝視頻、播放音樂文件、在通話中傳輸語音等)所需的能源效率和性能之間的平衡,這些內(nèi)核和邏輯單元會(huì)動(dòng)態(tài)地改變其時(shí)鐘頻率和電源電壓,通常在0.95到0.45伏之間。

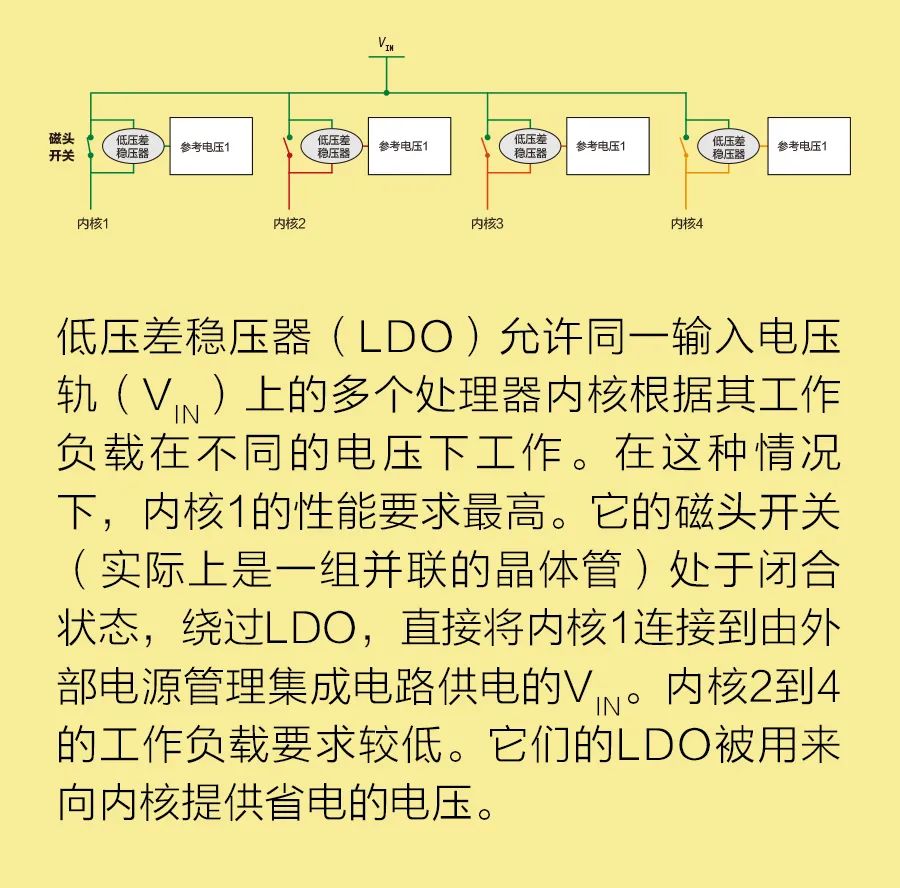

通常,外部電源管理集成電路會(huì)為手機(jī)SoC生成多個(gè)輸入電壓(VIN)值。這些電壓會(huì)沿著被稱為“軌”的寬連接線被輸送到SoC芯片的各個(gè)區(qū)域,但是電源管理芯片與SoC之間的連接數(shù)量有限,因此,SoC上的多個(gè)內(nèi)核必須共享同一個(gè)VIN軌。 不過,由于存在低壓差穩(wěn)壓器,它們不必都具備相同的電壓。LDO以及專用的時(shí)鐘發(fā)生器允許共享軌上的每個(gè)內(nèi)核按照獨(dú)有的電源電壓和時(shí)鐘頻率運(yùn)行。需要最高電源電壓的內(nèi)核會(huì)決定共享的VIN值。電源管理芯片將VIN設(shè)置為這個(gè)值,該內(nèi)核則會(huì)通過被稱為“磁頭開關(guān)”的晶體管繞過LDO。

為了將功耗降到最低,其他內(nèi)核可以在較低的電源電壓下工作。軟件決定了這個(gè)電壓值應(yīng)該是多少,而模擬LDO在提供相應(yīng)電壓方面做得相當(dāng)好。它們結(jié)構(gòu)緊湊、制造成本低,而且集成在芯片上也相對(duì)簡(jiǎn)單,因?yàn)樗鼈儾恍枰笮?a target="_blank">電感器或電容器。

不過,這些LDO只能在特定的電壓窗口下工作。就其高值而言,目標(biāo)電壓必須低于VIN和LDO本身的電壓下降(也叫“電壓差”)之間的差值。例如,如果內(nèi)核最有效的電源電壓為0.85伏,但VIN為0.95伏,LDO的電壓差為0.15伏,則該內(nèi)核無法利用LDO來達(dá)到0.85伏,相反必須在0.95伏下工作,這就浪費(fèi)了一些功率。

類似地,如果VIN已經(jīng)被設(shè)置在某個(gè)電壓限制以下,那么LDO的模擬元件將無法正常工作,電路也無法進(jìn)一步降低該內(nèi)核的電源電壓。 如果所需電壓落在LDO的窗口內(nèi),軟件將啟用電路并激活與目標(biāo)電源電壓相等的參考電壓。

那么LDO如何提供正確的電壓呢?

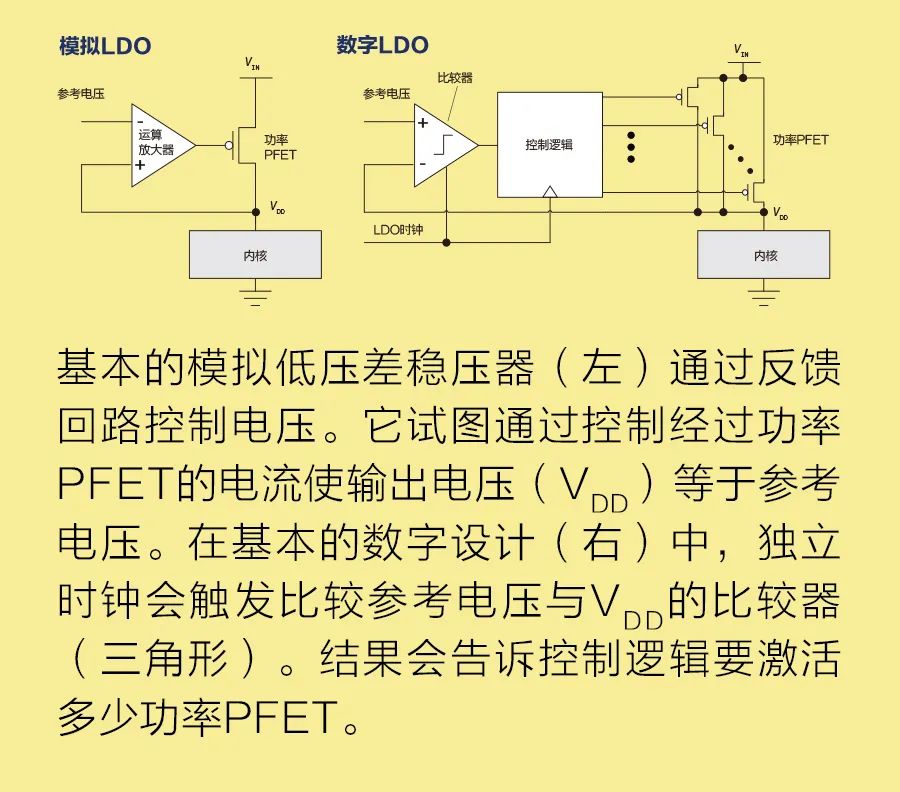

在基本的模擬LDO設(shè)計(jì)中,它是通過運(yùn)算放大器、反饋和專用功率p溝道場(chǎng)效應(yīng)晶體管(PFET)實(shí)現(xiàn)的。后者是一種晶體管,可隨著電壓增加至柵極而減小其電流。該功率PFET的柵極電壓來自運(yùn)算放大器的模擬信號(hào),范圍在0伏和VIN之間。

運(yùn)算放大器會(huì)持續(xù)比較電路的輸出電壓(內(nèi)核的電源電壓或VDD)與目標(biāo)參考電壓。如果LDO的輸出電壓下降到參考電壓以下,就像新激活的邏輯突然需要更多電流時(shí)一樣,運(yùn)算放大器會(huì)降低功率PFET的柵極電壓,增加電流并將VDD提升到參考電壓值。相反,如果輸出電壓上升到參考電壓以上,就像內(nèi)核的邏輯不太活躍時(shí)一樣,那么運(yùn)算放大器就會(huì)提高晶體管的柵極電壓以降低電流和VDD。

另一方面,一個(gè)基本的數(shù)字LDO由一個(gè)電壓比較器、控制邏輯和多個(gè)并聯(lián)功率PFET組成。(LDO也有自己的時(shí)鐘電路,與處理器內(nèi)核使用的時(shí)鐘電路分開。)在數(shù)字LDO中,電源PFET的柵極電壓是二進(jìn)制值而不是模擬值,所以要么是0伏要么是VIN。 隨著時(shí)鐘的每一次走動(dòng),比較器會(huì)測(cè)量輸出電壓是低于還是高于基準(zhǔn)源提供的目標(biāo)電壓。

比較器輸出會(huì)引導(dǎo)控制邏輯確定要激活多少功率PFET。如果LDO的輸出低于目標(biāo)值,則控制邏輯會(huì)激活更多功率PFET。它們的組合電流支撐著內(nèi)核的電源電壓,而該值會(huì)反饋給比較器,使其與目標(biāo)一致。如果高于目標(biāo)值,比較器就會(huì)向控制邏輯發(fā)送信號(hào),關(guān)閉一些PFET。

當(dāng)然,無論是模擬LDO還是數(shù)字LDO都不是理想的選擇。模擬設(shè)計(jì)的主要優(yōu)點(diǎn)在于,它可以快速響應(yīng)電源電壓的瞬態(tài)下降和過沖,當(dāng)涉及急劇變化時(shí)這尤為重要。之所以會(huì)發(fā)生這些瞬變,是因?yàn)閮?nèi)核對(duì)電流的需求可以在幾納秒內(nèi)大幅上升或下降。除了快速響應(yīng)外,模擬LDO還能很好地抑制來自軌上其他內(nèi)核的VIN變化。

最后,在電流需求變化不大時(shí),它還能嚴(yán)格控制輸出,而不會(huì)以一種在VDD中引入波紋的方式不斷地對(duì)目標(biāo)進(jìn)行過沖和下沖。 這些特性使得模擬LDO不僅在提供處理器內(nèi)核方面具有優(yōu)勢(shì),而且在幾乎所有要求安靜、穩(wěn)定電源電壓的電路中都具備優(yōu)勢(shì)。然而,有一些關(guān)鍵性挑戰(zhàn)因素限制了這些設(shè)計(jì)的有效性。

首先,模擬元件比數(shù)字邏輯復(fù)雜得多,在先進(jìn)的技術(shù)節(jié)點(diǎn)上實(shí)現(xiàn)它們需要長(zhǎng)時(shí)間的設(shè)計(jì)。其次,VIN較低時(shí),它們無法正常工作,從而限制了它們向內(nèi)核傳輸?shù)腣DD最低值。最后,模擬LDO的電壓差并不像設(shè)計(jì)者希望的那么小。 綜合最后這幾點(diǎn),模擬LDO提供了一個(gè)其能夠工作的有限電壓窗口。這意味著無法用LDO實(shí)現(xiàn)省電,而用LDO實(shí)現(xiàn)省電能夠顯著提高智能手機(jī)電池的壽命。 數(shù)字LDO則解決了其許多弱點(diǎn):沒有復(fù)雜的模擬元件,設(shè)計(jì)師能夠利用豐富的工具和其他資源進(jìn)行數(shù)字設(shè)計(jì)。

因此,為了使用一種新的工藝技術(shù)而縮小電路規(guī)模所需要做的工作更少。數(shù)字LDO也將在更大的電壓范圍內(nèi)工作。在低電壓端,數(shù)字元件可以在超出模擬元件范圍的VIN值下工作。在高電壓端,數(shù)字LDO的電壓差將更小,從而能有效地節(jié)省內(nèi)核功率。 不過,凡事各有利弊,數(shù)字LDO也有一些嚴(yán)重的缺點(diǎn)。其中大部分是因?yàn)殡娐分粫?huì)間歇性地測(cè)量和改變其輸出,而不會(huì)連續(xù)測(cè)量和改變輸出。這意味著電路對(duì)電源電壓下降和過沖的響應(yīng)相對(duì)較慢。它對(duì)VIN的變化也更敏感,而且往往會(huì)在輸出電壓中產(chǎn)生小波動(dòng),這兩種情況都會(huì)降低內(nèi)核的性能。

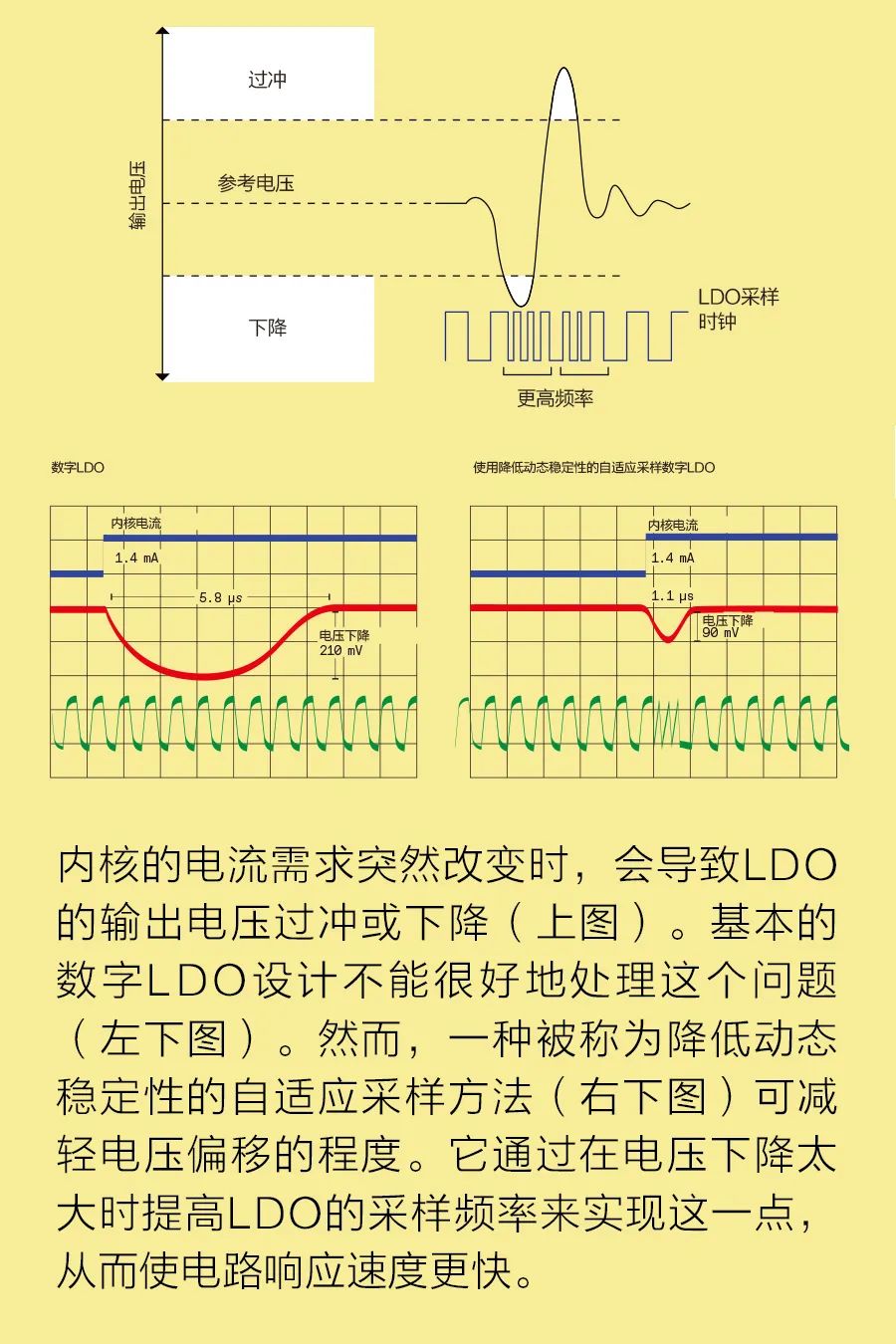

目前,限制數(shù)字LDO使用的主要障礙是其緩慢的瞬態(tài)響應(yīng)。當(dāng)內(nèi)核汲取的電流在響應(yīng)其工作負(fù)載的變化時(shí)突然發(fā)生變化,則內(nèi)核會(huì)經(jīng)歷下降和過沖。要限制電壓下降的程度和持續(xù)時(shí)間,LDO對(duì)下降事件的響應(yīng)時(shí)間至關(guān)重要。傳統(tǒng)內(nèi)核給電源電壓增加了一個(gè)安全裕度,以確保其在下降期間能正常工作。更多的預(yù)期下降意味著裕度必須更大,這就降低了LDO的能效效益。因此,加快數(shù)字LDO對(duì)下降和過沖的響應(yīng)是這一領(lǐng)域前沿研究的主要焦點(diǎn)。

最近取得的一些進(jìn)步有助于加速電路對(duì)下降和過沖的響應(yīng)。其中一種方法將數(shù)字LDO的時(shí)鐘頻率作為控制旋鈕,以穩(wěn)定性和功率效率換取響應(yīng)時(shí)間。 較低的頻率提高了LDO的穩(wěn)定性,這是因?yàn)檩敵霾粫?huì)經(jīng)常改變。它還降低了LDO的功耗,因?yàn)闃?gòu)成LDO的晶體管切換頻率較低。

不過,其代價(jià)是對(duì)來自處理器內(nèi)核的瞬態(tài)電流需求的響應(yīng)較慢。細(xì)想可知,如果頻率太低,就可能在一個(gè)單一時(shí)鐘周期內(nèi)發(fā)生一個(gè)瞬態(tài)事件,因此會(huì)出現(xiàn)這種情況。 高LDO時(shí)鐘頻率反而會(huì)縮短瞬態(tài)響應(yīng)時(shí)間,因?yàn)楸容^器進(jìn)行輸出采樣的頻率足以在瞬態(tài)事件發(fā)生之前改變LDO的輸出電流。

然而,這種恒定采樣會(huì)降低輸出的穩(wěn)定性并消耗更多的功率。 這種方法的要點(diǎn)是引入一種其頻率能夠適應(yīng)這種情況的時(shí)鐘,即降低動(dòng)態(tài)穩(wěn)定性的自適應(yīng)采樣頻率方法。當(dāng)電壓下降或過沖超過一定水平時(shí),時(shí)鐘頻率會(huì)提高,以更快地減少瞬態(tài)效應(yīng)。然后它會(huì)減慢速度以消耗更少的功率并保持輸出電壓穩(wěn)定。

這種效果是通過添加一對(duì)額外的比較器來檢測(cè)過沖和下降情況,并觸發(fā)時(shí)鐘來實(shí)現(xiàn)的。在測(cè)量使用這種技術(shù)的測(cè)試芯片時(shí),VDD的電壓下降從210毫伏降低到了90毫伏,與標(biāo)準(zhǔn)的數(shù)字LDO設(shè)計(jì)相比降低了57%。電壓恢復(fù)到穩(wěn)定狀態(tài)的時(shí)間從5.8微秒縮短到1.1微秒,所需時(shí)間縮短了81%。

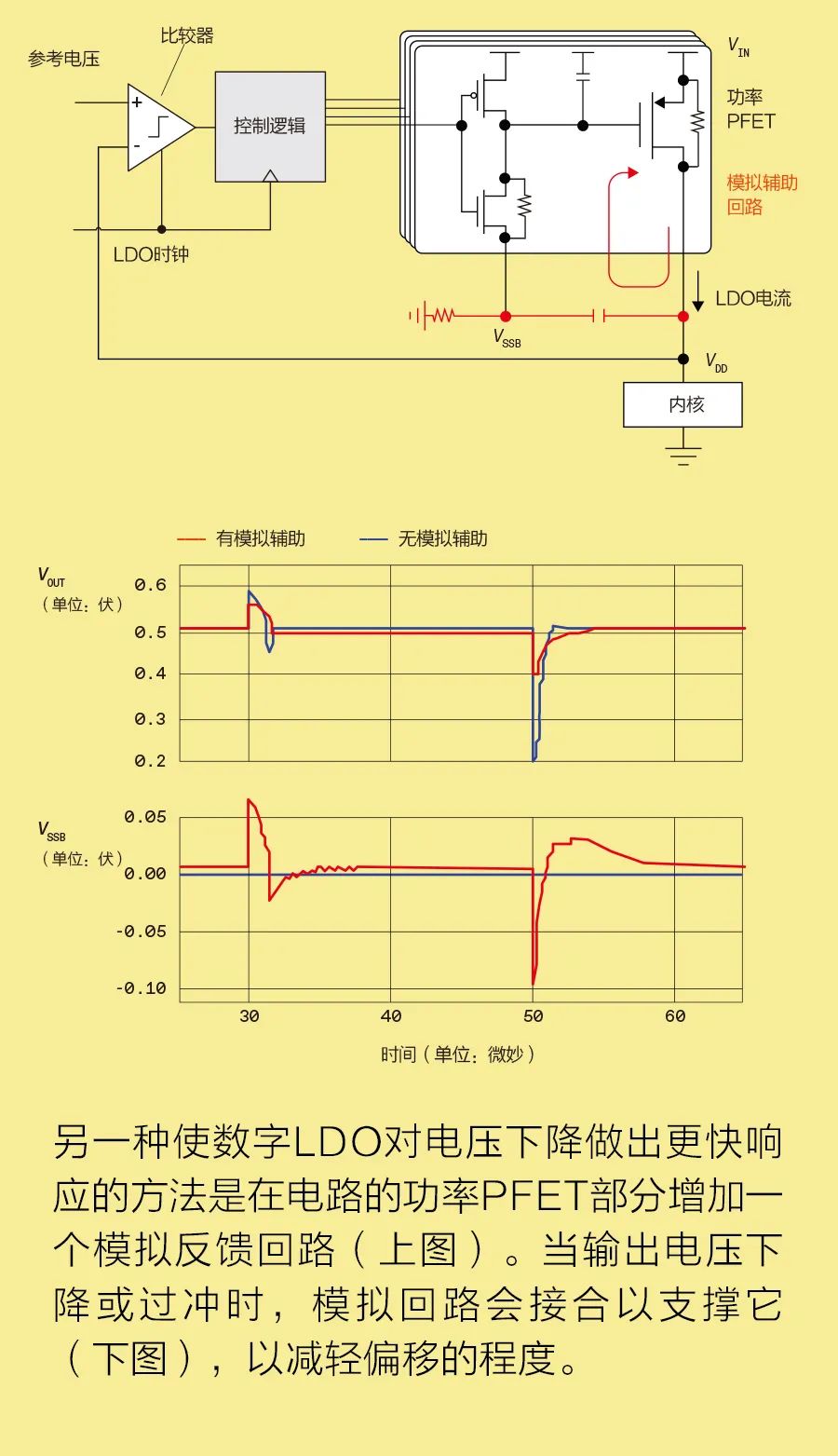

另一種縮短瞬態(tài)響應(yīng)時(shí)間的方法是給數(shù)字LDO增加一點(diǎn)模擬性。這種設(shè)計(jì)集成了一個(gè)獨(dú)立的模擬輔助回路,可對(duì)負(fù)載電流瞬變作出即時(shí)響應(yīng)。模擬輔助回路可通過一個(gè)電容器將LDO的輸出電壓耦合到LDO的并聯(lián)PFET,從而形成一個(gè)僅在輸出電壓急劇變化時(shí)才接合的反饋回路。因此,當(dāng)輸出電壓下降時(shí),它會(huì)降低已激活PFET柵極的電壓,并瞬間增加流向內(nèi)核的電流,以降低電壓下降幅度。

現(xiàn)已證明,這種模擬輔助回路可以將電壓下降從300毫伏降低到106毫伏(改善65%),可將過沖從80毫伏降低到70毫伏(改善13%)。 當(dāng)然,這兩種技術(shù)都有各自的缺點(diǎn)。首先,兩者都不能真正匹配現(xiàn)在的模擬LDO的響應(yīng)時(shí)間。此外,自適應(yīng)采樣頻率技術(shù)需要兩個(gè)額外的比較器,還需要生成并校準(zhǔn)下降和過沖參考電壓,以便電路知道何時(shí)使用更高的頻率。

模擬輔助回路包括了一些模擬元件,會(huì)減少全數(shù)字系統(tǒng)的設(shè)計(jì)時(shí)間效益。 商用SoC處理器的發(fā)展即使不能完全匹配模擬性能,也可能有助于數(shù)字LDO取得更大的成功。如今,商用SoC處理器集成了全數(shù)字自適應(yīng)電路,以便在出現(xiàn)電壓下降時(shí)緩解性能問題。

例如,這些電路會(huì)暫時(shí)延長(zhǎng)內(nèi)核的時(shí)鐘周期,防止計(jì)時(shí)錯(cuò)誤。這種緩解技術(shù)可以放寬瞬態(tài)響應(yīng)時(shí)間限制,允許使用數(shù)字LDO并提高處理器效率。如果是這樣,我們就可以期待更高效的智能手機(jī)和其他電腦,同時(shí)讓它們的設(shè)計(jì)過程更加輕松簡(jiǎn)單。

審核編輯:劉清

-

穩(wěn)壓器

+關(guān)注

關(guān)注

24文章

4258瀏覽量

94187 -

晶體管

+關(guān)注

關(guān)注

77文章

9746瀏覽量

138916 -

低壓差穩(wěn)壓器

+關(guān)注

關(guān)注

0文章

158瀏覽量

20774 -

DVFS

+關(guān)注

關(guān)注

1文章

18瀏覽量

12027 -

LDO電路

+關(guān)注

關(guān)注

0文章

26瀏覽量

2479

原文標(biāo)題:可延長(zhǎng)電池壽命的電路

文章出處:【微信號(hào):CloudBrain-TT,微信公眾號(hào):云腦智庫(kù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

LDO低壓差線性穩(wěn)壓器

LDO低壓差線性穩(wěn)壓器的簡(jiǎn)介

1μAIi同步升壓轉(zhuǎn)換器可延長(zhǎng)便攜式設(shè)備的電池壽命

80μA靜態(tài)電流同步降壓控制器可延長(zhǎng)汽車應(yīng)用中的電池壽命

SOT-23 SMBus風(fēng)扇速度控制器可延長(zhǎng)電池壽命并降低噪音

低壓差線性穩(wěn)壓器LDO的相關(guān)資料分享

低壓差線性穩(wěn)壓器(LDO)的壓差和功耗

低壓差線性穩(wěn)壓器LDO

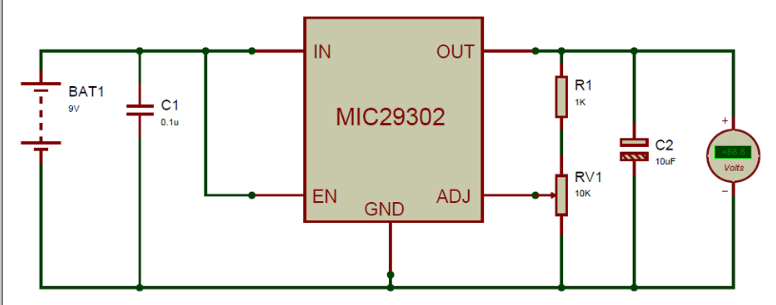

使用MIC29302構(gòu)建LDO穩(wěn)壓器或低壓差穩(wěn)壓器電路

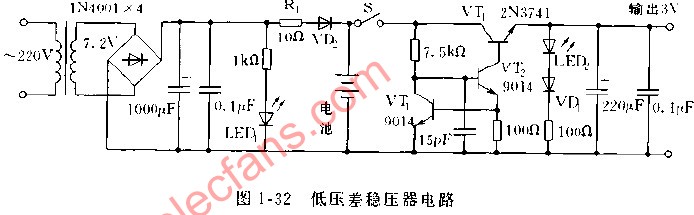

低壓差穩(wěn)壓器(LDO)電路設(shè)計(jì)

具有ULQ? 模式、可延長(zhǎng)電池壽命的4.5V至24V、8A同步降壓穩(wěn)壓器TPS51396A數(shù)據(jù)表

可延長(zhǎng)電池壽命的電路—低壓差穩(wěn)壓器LDO電路

可延長(zhǎng)電池壽命的電路—低壓差穩(wěn)壓器LDO電路

評(píng)論