前言

數字經濟已成為繼農業經濟、工業經濟之后的主要經濟形態。算力作為數字經濟的核心生產力,將直接影響數字經濟發展的速度,決定社會智能的發展高度。存算一體作為一種新型算力,有望解決傳統馮·諾依曼架構下的“存儲墻”、“功耗墻”問題。存算一體將存儲與計算有機融合以其巨大的能效比提升潛力,有望成為數字經濟時代的先進生產力。存算一體芯片設計迭代和投產的效率至關重要,如何能夠設計出更低損耗、更低噪聲、更低能耗,并符合信號完整性、電源完整性指標性能的存算一體芯片,從而提高存算一體芯片的設計效率呢?

存算一體芯片市場概況

據IDC預測,2025年全球物聯網設備數將超過400億臺,產生數據量接近80ZB。在智慧城市、智能家居、自動駕駛等諸多場景中超過一半的數據需要依賴終端本地處理,單設備算力需求約在0.1~64TOPS之間,海量數據將在邊緣側進行處理,流量模型逐漸從云側擴展到邊側。邊緣計算場景下對單設備算力需求約在64~256TOPS之間,時延要求高。到2030年將帶動智能算力需求增長500倍,以AI算力為核心的智算中心將成為算力基礎設施主流,大規模的AI芯片集約化建設帶來高功耗挑戰,每機架平均功耗將由3~5kw逐漸升至7~10kW。未來智算中心呼喚新型AI芯片,以滿足云側大算力、高帶寬、低功耗等特性。 與傳統方案相比,存算一體在深度學習等領域有獨特優勢,可以提供比傳統設備高幾十倍的算效比。此外存算一體芯片通過架構創新可以提供綜合性能全面的芯片及板卡,預計將在邊側推理場景中有著廣泛的應用。存算一體可通過多核協同集成大算力芯片,結合可重構設計打造通用計算架構,存算一體作為智算中心下一代關鍵AI芯片技術,正面向大算力、通用性、高計算精度等方面持續演進,有望為智算中心提供綠色節能的大規模AI算力。

存算一體芯片設計中的挑戰

1. 基于3DIC架構的三維堆疊芯片

電磁場求解挑戰

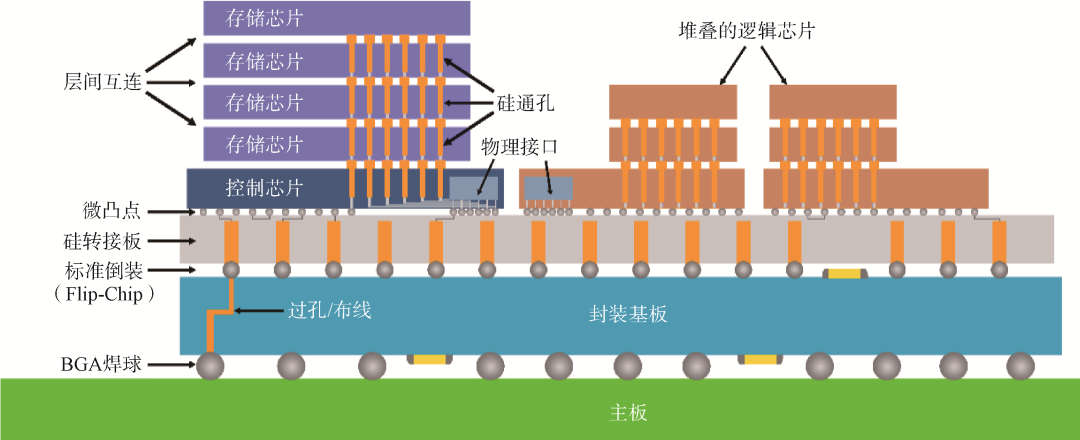

在存算一體芯片中,按照封裝結構可以分為2D、2.5D 和3D。不通過額外中介層,直接在有機基板上互連芯片的形式稱為2D 封裝,該方案成本低,但互連線的密度不高,采用高速串行互連技術一定程度上可以彌補低帶寬問題。臺積電的CoWoS芯片(Chip on Wafer on Substrate, CoWoS)技術是典型的2.5D 封裝技術,即通過硅轉接板實現多顆芯片的互連和集成。3D封裝是指兩顆或多顆芯粒通過硅通孔、以面對背(Face-to-Back)的形式,或通過微凸點或混合鍵合技術、以面對面(Face-to-Face)的形式,在垂直方向直接堆疊,并實現芯粒間和對外界的信號連接的技術(圖1)。目前主流的3D 封裝技術主要包括臺積電的系統整合芯片(System on Integrated Chip, SoIC)技術和英特爾的Foveros3D 封裝技術等。3D 封裝互連密度更高,距離更短,速度更快,但是成本更高且存在散熱和應力等問題。

圖 1

3DIC示意圖

基于3D架構的存算一體芯片,通過混合鍵合(Hybrid Bonding)技術進行存儲芯片和ASIC之間的高密度互連通信,Bump數量達到數千甚至數萬、幾十萬的級別,Die內的RDL和Via數量更是龐大,整個結構的電磁場求解未知量規模是一般求解器難以進行計算的,如何對模型進行合理的堆疊,內部細節如何合理有效簡化對仿真速率和求解精度將至關重要。

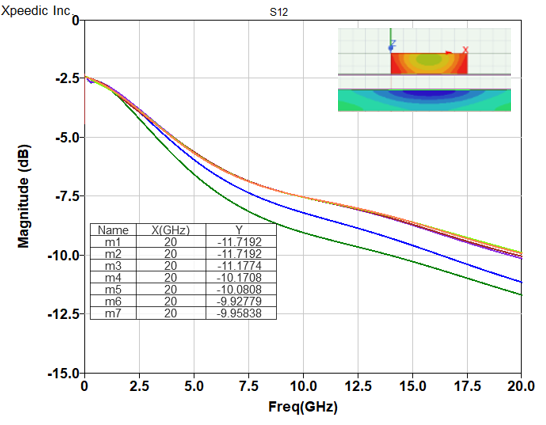

2. um尺寸級別下仿真精度挑戰

在2.5D/3D的存算一體芯片中,芯片間的高密度互連將進入um階段,基于CoWoS封裝的互連走線線寬甚至能到達到0.4um。由于趨膚效應,傳統PCB和有機封裝基板中的傳輸線電流大多流經導體的表面(圖2)。當線寬接近于趨膚深度時,傳輸線截面基本上全部有電流經過,這使得我們在采用傳統電磁場仿真引擎時,需要設置對導體內部進行求解,這會導致整體模型的網格數量急劇增加,同時對工程師的操作經驗要求極高。

圖 2

20Ghz時,典型CoWoS-S工藝下導體截面

電流分布和網格密度對損耗的影響

以TSMCCoWoS-S為例,Metal層的厚度在0.6um左右,RDL層布線一般在2um左右,最小可達0.4um。在該尺度下,如何能夠兼顧仿真精度與效率,將考驗電磁場仿真算法和工程師的設置技巧。

3. 大規模求解對高性能運算(HPC)的需求

對于3DIC架構的存算一體芯片來說,傳統RC提取工具無法滿足精度要求,大量高速SerDes和Memory互連線需要強大的全波三維電磁仿真引擎進行快速分析。由于互連結構的復雜程度,需要在進行網格剖分和未知量求解時采用多機器、多核心、多任務來進行仿真任務管理,SI/PI仿真分析時間在很大程度上決定產品的迭代周期。

芯和存算一體芯片仿真解決方案

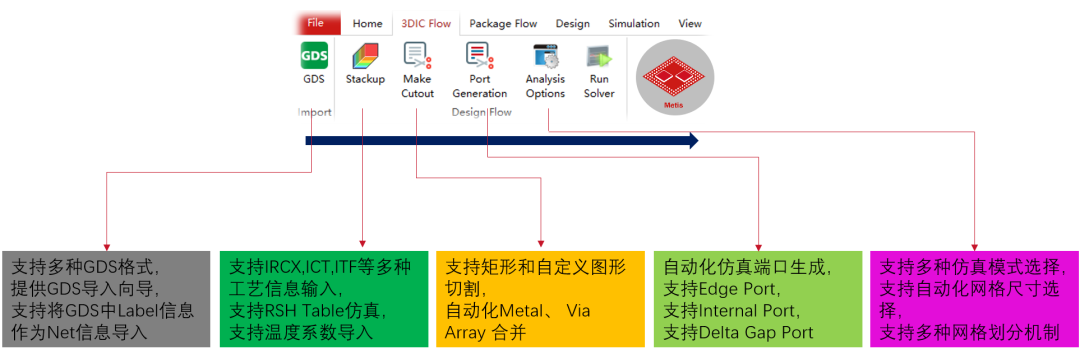

芯和半導體針對3D封裝存算一體芯片提供了完整的信號完整性解決方案。Metis 作為整個解決方案中的關鍵電磁場求解引擎,是一款應用于3DIC先進封裝聯合仿真的 EDA 仿真平臺,其內置了操作友好的3DIC先進封裝仿真流程(圖3),同時與3DIC Compiler 設計環境無縫集成,用戶在設計的任何階段都可以調用Metis工具來進行版圖的電磁仿真;三維全波高精度電磁仿真可以滿足異構集成中高速高頻等應用的精度要求,并可以支持納米到厘米級別的跨尺度仿真,實現芯片、封裝的聯合仿真;被用戶廣泛應用于CoWoS-S/CoWoS-R/FOCos/等3DIC先進封裝的電磁場建模。

圖3

Metis提供的3DIC建模流程

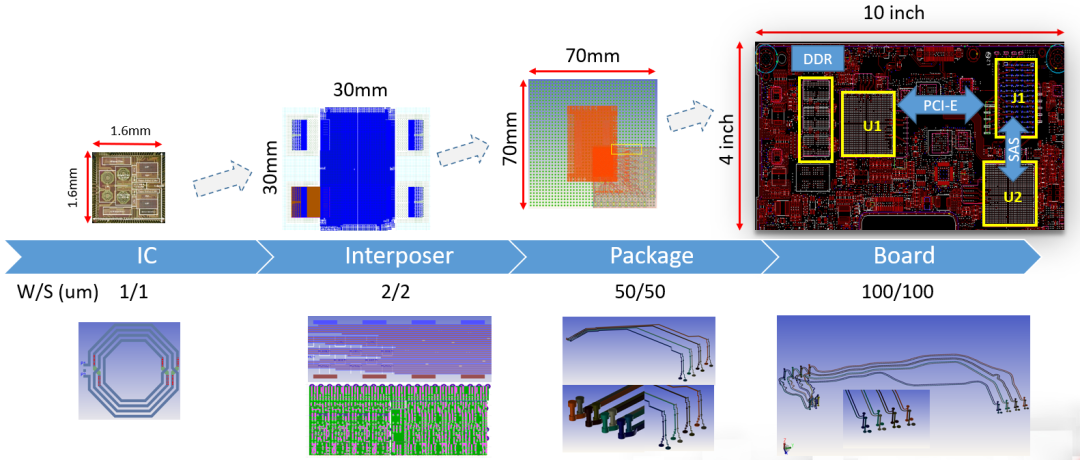

1.支持從0-100um多尺度跨越的

電磁場求解器

在芯片、封裝和系統的電磁聯合仿真上,由于模型尺寸跨度太大,難以進行統一的網格剖分。芯片走線的寬度和間距在1um以下級別,硅載板走線在2um左右,基板封裝走線在50um左右,而PCB走線能達到100um左右(圖4),如果對芯片使用基板封裝的剖分機制,精度顯然是不夠的,同樣,如果對基板封裝使用芯片的網格剖分機制,那么對規模和速度上又會是巨大的挑戰。

圖4

芯片、封裝和系統的物理尺度

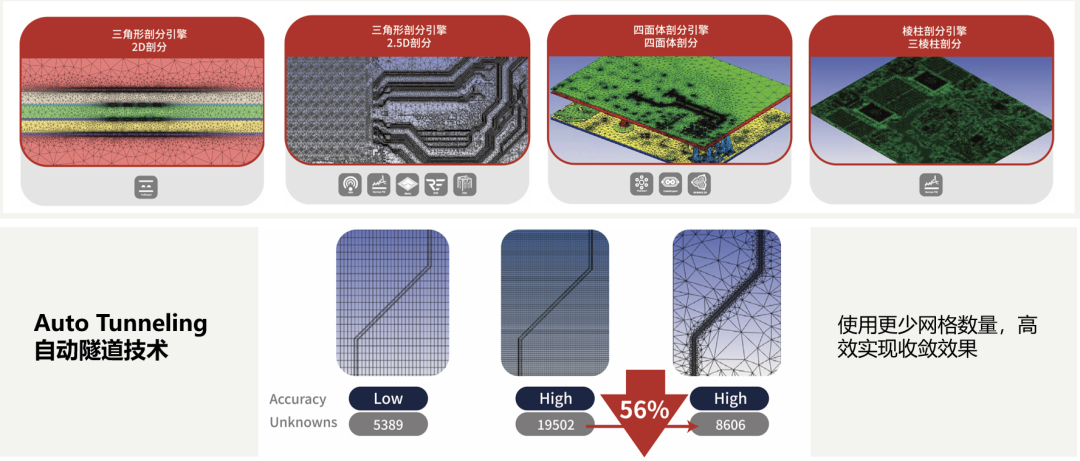

針對這一場景,Metis平臺有其自身的優勢和特點,它內置了芯和的AI智能網格剖分融合技術(圖5)能夠根據結構的特點自動選擇合適的網格尺寸,集成的多尺度快速電磁場求解算法,可以解決芯片、硅載板、有機封裝到PCB的不同尺度所帶來的聯合仿真問題。

圖5

AI智能網格剖分融合技術

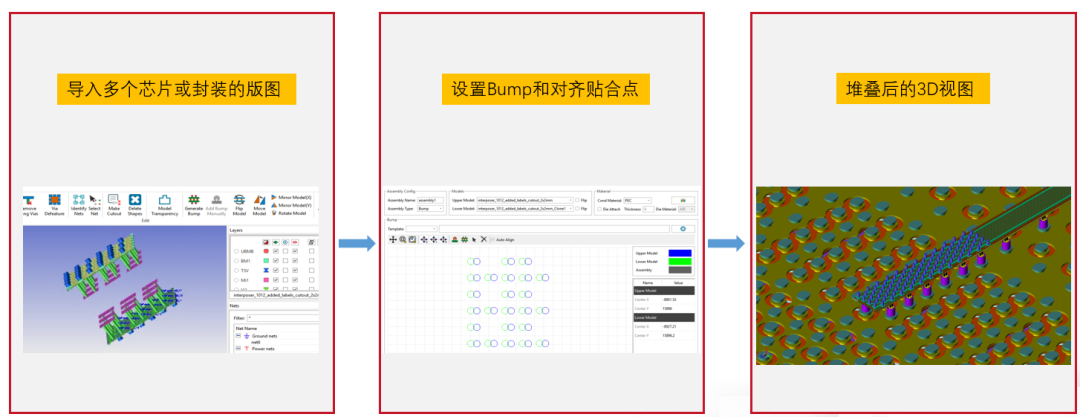

2.支持多Die三維堆疊建模和聯合仿真

基于3D堆疊的存算一體芯片中,異構集成的芯片通過混合鍵合技術進行高密度互連,芯和半導體的Metis提供了多芯片堆疊的建模向導(圖6),用戶可以導入多個芯片GDS或封裝版圖,然后設置用于連接的TSV和bump的尺寸、填充材料等屬性,這時也可以對芯片進行flip,mirror等操作,之后,可以進行坐標定位,或是bump位置的自動對齊,實現多個芯片的堆疊互連。最后使用堆疊后的3D互聯結構,進行統一的網格劃分和電磁求解,可對互聯結構的電磁場分布和損耗、串擾等進行精確模擬。

圖 6

Metis三維堆疊建模流程

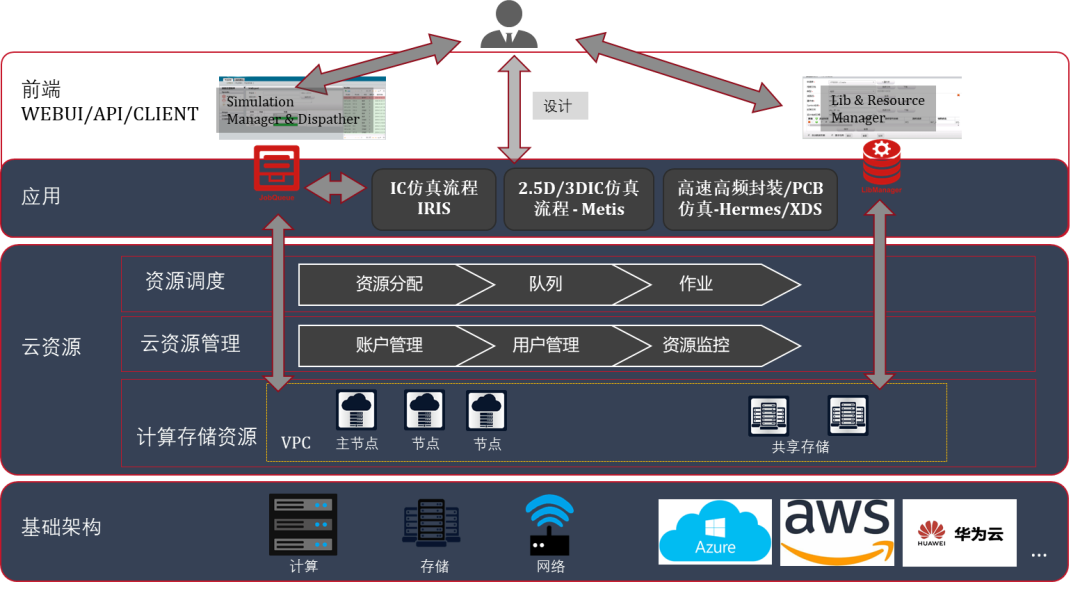

3.支持云平臺的高性能計算

多芯片或Die+Package的堆疊建模仿真中,其網格密度高,普通單臺服務器難以快速仿真并得到結果。芯和電子系統設計仿真云平臺已登錄微軟、亞馬遜、華為云等領先平臺(圖7),其解決方案集成核心差異化的電磁場仿真技術與軟件、本地集群仿真技術、MPI仿真技術、云計算技術和分布式集群管理技術,使芯片、封裝、系統設計大規模電磁仿真EDA的資源管理和資源統一調度使用成為了可能,通過使用優秀的管理系統和管理策略,達到資源統一分配和管理,不僅增加了各計算中的資源利用率,降低了計算中心的維護和部署成本,同時發揮芯和仿真軟件的Intelligent Mesh、Scalable EM Solver多尺度電磁引擎、Parallel Computing并行計算能力,為電子系統設計中的芯片,封裝,PCB,系統進行大規模復雜電磁場仿真提供了可能。

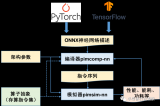

圖 7

Xpeedic EDA 云平臺架構

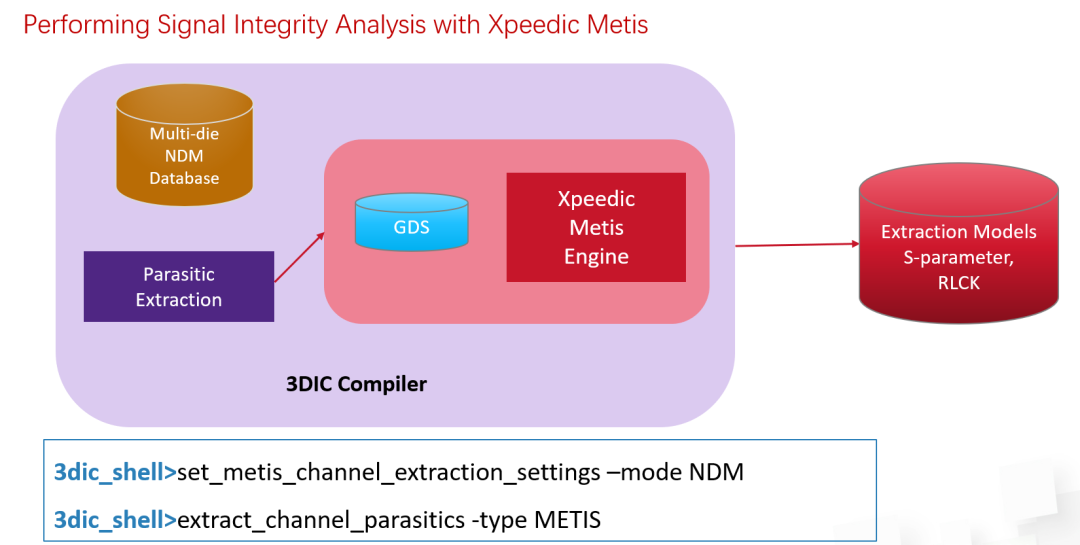

4.支持從3DIC設計到仿真的全流程解決方案

傳統的EDA流程在進行2.5D、3DIC集成設計的時候,需要在多個工具的圖形用戶環境中設計、分析及交換數據。存在全系統分散式管理,多種點工具的協作交互繁瑣,系統容量和結構形式受限,設計和分析工具之間的第三方接口不夠順暢等問題。

芯和半導體的2.5D/3DIC先進封裝分析方案Metis與3DIC Compiler現有的設計流程無縫結合,為客戶構建了一個完全集成、性能卓著且易于使用的環境(圖8),提供了從開發、設計、驗證、信號完整性仿真、電源完整性仿真到最終簽核的3DIC全流程解決方案。突破了傳統封裝技術的極限,該方案能同時支持芯片間幾十萬根數據通道的互聯。

圖 8

在3DIC Compiler中調用Metis電磁場求解引擎

總結

本文首先講述了存算一體芯片的發展現狀和市場情況,然后總結了存算一體芯片仿真分析中所面臨的挑戰。針對這些挑戰,芯和半導體推出的存算一體芯片仿真方案集成了差異化的電磁場仿真技術、內置了AI智能網格剖分融合技術、多尺度快速電磁場求解算法、3DIC流程化建模向導、HPC加速技術,使存算一體芯片、封裝、系統設計大規模電磁仿真成為可能。同時,3DIC Compiler到Metis工具中的無縫對接,大大減少數據交換風險,統一的設計、仿真、驗證平臺減少了用戶芯片的設計迭代。

審核編輯:湯梓紅

-

芯片

+關注

關注

456文章

51170瀏覽量

427227 -

仿真

+關注

關注

50文章

4124瀏覽量

133987 -

AI

+關注

關注

87文章

31513瀏覽量

270326 -

3DIC

+關注

關注

3文章

83瀏覽量

19443 -

存算一體

+關注

關注

0文章

104瀏覽量

4328

原文標題:【解決方案】基于3DIC架構的存算一體芯片仿真解決方案

文章出處:【微信號:Xpeedic,微信公眾號:Xpeedic】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

存算一體大算力AI芯片將逐漸走向落地應用

新思科技推出3DIC Compiler平臺,轉變了復雜的2.5和3D多裸晶芯片系統的設計與集成

現在3DIC設計面臨哪些挑戰?

基于RISC-V開放架構的存算一體化芯片解決方案

基于3DIC架構的存算一體芯片仿真解決方案

基于3DIC架構的存算一體芯片仿真解決方案

評論