1. 電源結構

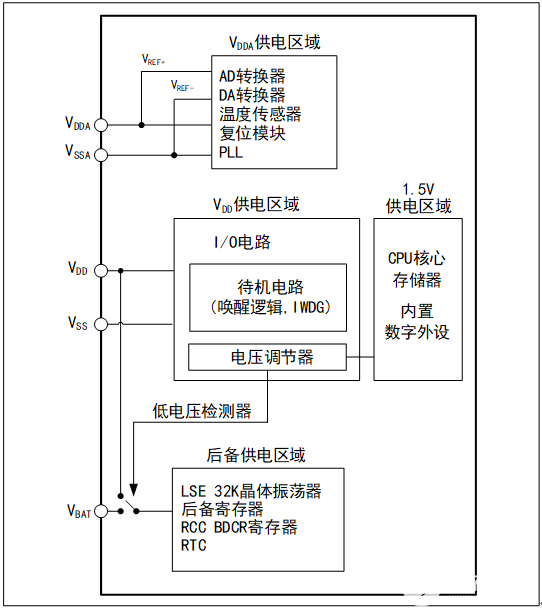

CH32V307供電結構如下圖所示:

通常CH32V307工作電壓VDD的范圍為2.4V~3.6V,當使用ETH或USB時,工作電壓VDD的范圍為 3.0V~3.6V

內置電壓調節器提供內核所需的1.5V電源。

VDDA和VSSA為模擬部分供電

為了提高AD等模擬部分的精度,可以使用獨立的電源為VDDA和VSSA供電。

CH32V307VCT6 LQFP100封裝的VREF+和VREF-引腳引出,用戶可連接一個獨立的參考電壓用于ADC測量,參考電壓范圍:2.4V ≤ VREF+ ≤ VDDA。

其他封裝的CH32V307的VREF+和VREF-引腳未引出,在芯片內部與VDDA和VSSA相連。

VBAT為后備電源引腳,當VDD斷電時,掉電復位功能會自動切換VBAT為后備供電區域供電,用于維持RTC以及后備寄存器的內容。

當切換到VBAT供電時:

PC14和PC15只能用作LSE引腳

PC13可以作為TAMPER侵入檢測引腳、RTC鬧鐘或秒輸出

當VDD恢復供電穩定后,系統自動切換開關,后備區由VDD供電,此時PC13~PC15可以做為GPIO。因為模擬開關只能通過少量的電流,當用在輸出時,速度必須限制在2MHz以下,最大負載電容為30pF,并且禁止用在持續輸出和吸收電流的場合,比如LED驅動。

如果沒有使用外部電池為VBAT供電,VBAT引腳必須連接到VDD引腳上

電池到VBAT的連線要盡可能的短

在主電源VDD恢復供電過程中,內部VBAT 電源仍然通過對應的VBAT 引腳連在外部備用電源上,若 VDD在小于復位滯后時間 tRSTTEMPO 內就達到穩定,并且高于 VBAT的值 0.6V 以上,則有可能存在較短瞬間,電流通過 VDD 與 VBAT之間的二極管灌入 VBAT,進而通過 VBAT 引腳注入電池等后備電源,如果后備電源無法承受這樣瞬時注入電流,建議在后備電源和VBAT 引腳之間加一只正向導通低壓降二極管。

2. 電源管理

2.1 上電復位和掉電復位

系統內部集成了上電復位POR 和掉電復位PDR 電路。

當芯片供電電壓VDD 和VDDA 低于對應門限電壓時,系統被相關電路復位,無需外置額外的復位電路。

上電門限電壓 VPOR 和掉電門限電壓 VPDR 的參數請參考對應的數據手冊。

2.2 可編程電壓監測器(PVD)

可編程電壓監測器 PVD,主要被用于監控系統主電源的變化,與電源控制寄存器 PWR_CTLR 的PLS[2:0]所設置的門檻電壓相比較,配合外部中斷寄存器(EXTI)設置,可產生相關中斷,以便及時通知系統進行數據保存等掉電前操作。

PVD詳細配置參考。

3. 低功耗模式

微控制器目前提供了3 種低功耗模式,從處理器、外設、電壓調節器等的工作差異上分為:

睡眠模式 :內核停止運行,所有外設(包含內核私有外設)仍在運行

停止模式 :停止所有時鐘,喚醒后系統繼續運行。

待機模式 :停止所有時鐘,喚醒后系統復位(電源復位)。

低功耗模式一覽:

| 低功耗模式 | 進入方式 | 喚醒源 | 對時鐘的影響 | 電壓調節器 |

|---|---|---|---|---|

| 睡眠 | WFI WFE | WFI:任意中斷喚醒 WFE:喚醒事件喚醒 | 內核時鐘關閉, 其他時鐘無影響 | 正常 |

| 停止 |

1) SLEEPDEEP置1 2) PDDS清0 3) WFI或WFE |

任一外部中斷/事件(在外部中斷寄存器中設置) WKUP引腳上升沿 | 關閉HSE、HSI、PLL 和外設時鐘 | 正常:LPDS=0 低功耗:LPDS=1 |

| 待機 |

1) SLEEPDEEP置1 2) PDDS置1 3) WFI或WFE |

WKUP引腳上升沿 RTC鬧鐘事件 NRST引腳復位 IWDG復位 注:任意外部中斷/事件也可以喚醒系統, 但喚醒后系統不復位 | 關閉HSE、HSI、PLL 和外設時鐘 | 正常:LPDS=0 低功耗:LPDS=1 |

-

mcu

+關注

關注

146文章

17319瀏覽量

352650 -

電源管理

+關注

關注

115文章

6193瀏覽量

144950 -

電源系統

+關注

關注

3文章

628瀏覽量

37900 -

VDD

+關注

關注

1文章

312瀏覽量

33543 -

RISC-V

+關注

關注

45文章

2323瀏覽量

46592

發布評論請先 登錄

相關推薦

擁抱RISC-V的開發世界 兆易創新推GD32VF103系列RISC-V MCU

青稞RISC-V通用系列MCU一覽

國產RISC-V MCU推薦

RISC-V的MCU與ARM對比

RISC-V的MCU關于USB高速通信設計的難點

risc-v的mcu對RTOS兼容性如何

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

RISC-V MCU開發相關資料分享

RISC-V MCU開發相關資料分享

RISC-V MCU開發的相關資料分享

RISC-V MCU開發(一):集成開發環境

RISC-V MCU電源系統概述

RISC-V MCU電源系統概述

評論