展示的是可以如何使用 AXI Video Direct Memory Access (VDMA) IP 來(lái)實(shí)現(xiàn)視頻剪裁、畫中畫或軟模式生成器功能。

示例 1:使用 AXI VDMA IP 的視頻裁剪

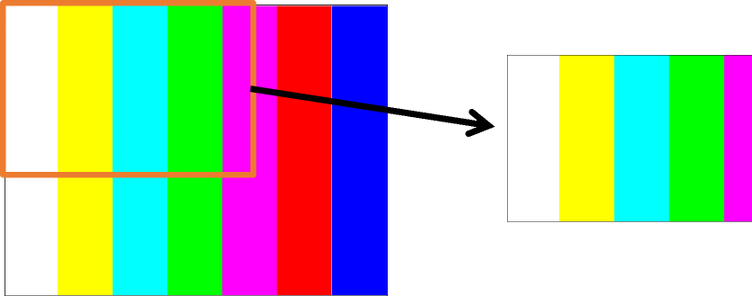

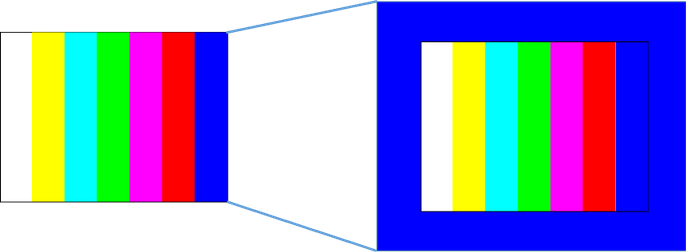

視頻裁剪在某些情況下,您可能需要輸出分辨率比輸入分辨率小。視頻剪裁是您可以通過(guò) AXI 視頻直接存儲(chǔ)器訪問(wèn)(VDMA) IP 執(zhí)行的一項(xiàng)操作。

視頻剪裁是對(duì)圖像的特定部分進(jìn)行的“剪切”。我們可以通過(guò)只讀取傳入視頻的一部分來(lái)完成此操作。

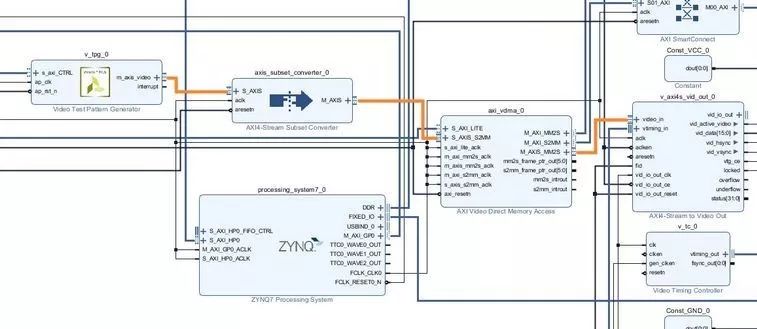

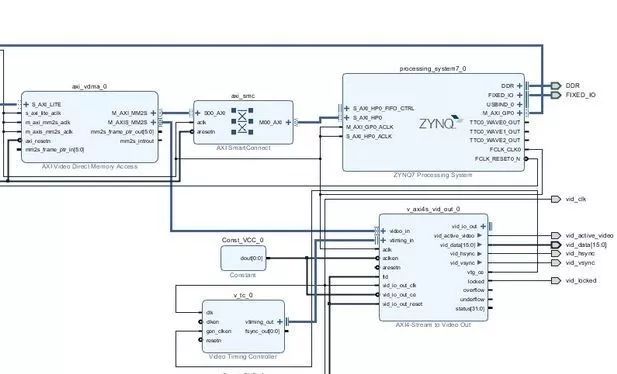

在此示例中,我要將測(cè)試模式生成器(TPG) IP 用作源,并且將 AXI VDMA IP 配置為已啟用讀寫通道。這與視頻系列 24 中的設(shè)計(jì)相同。

在這個(gè)應(yīng)用中,我要把TPG IP設(shè)置為可以生成分辨率為1024x768的視頻(而會(huì)把HDMI輸出分辨率固定為800x600)

//Configure the TPG app_hdmi_conf_tpg(&tpg_inst, 768, 1024, 0x2, XTPG_BKGND_COLOR_BARS);

必須完成的主要配置是 AXI VDMA IP。

寫入接口被設(shè)置為1024x768

//S2MM Frame delay / Stride register Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xA8, 1024*2); // S2MM HSIZE register Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xA4, 1024*2); // S2MM VSIZE register Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xA0, 768);

讀取接口被設(shè)置為 800x600。

// MM2S Frame delay / Stride register Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x58, 1024*2); // MM2S HSIZE register Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x54, 800*2); // MM2S VSIZE register Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x50, 600);

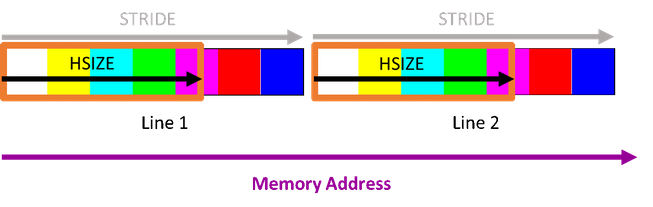

請(qǐng)注意,此處的 STRIDE 參數(shù)不等于 HSIZE 參數(shù)。這是我們確實(shí)可以使用此參數(shù)的一種情況。

如果 STRIDE 等于 HSIZE,那么 AXI VDMA IP 會(huì)在沒(méi)有任何跳轉(zhuǎn)的情況下讀取幀緩存。但是,由于輸入大小大于輸出大小,我們需要在地址之間跳轉(zhuǎn)以便能夠正確地對(duì)齊下一行的開頭。

STRIDE 參數(shù)用于描述每個(gè)視頻行第一個(gè)像素之間的地址的字節(jié)數(shù)。

如果我們想在輸入幀中移動(dòng)剪裁窗口,我們只需在幀緩存地址中添加偏移,使 HSIZE 和 STRIDE 參數(shù)值保持一致即可。

例如,如果我們想要讓剪裁窗口水平居中,可以為讀取接口的幀緩存地址添加 224 的偏移((hsize_in –hsize_out)/2 * bytes/pixel = (1024 - 800)/2 * 2 = 224)。

// MM2S Start Address 1 Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x5C, 0x10000000 + 224); // MM2S Start Address 2 Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x60, 0x10200000 + 224); // MM2S Start Address 3 Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x64, 0x10400000 + 224);

注意:在此示例中,偏移需要是存儲(chǔ)器映射數(shù)據(jù)寬度字節(jié)(32 位)的倍數(shù),因?yàn)樵凇癆XI VDMA IP”配置中未啟用“Allow Unaligned Transfers”。

示例 2:使用 AXI VDMA IP 的畫中畫

畫中畫如果設(shè)計(jì)中的輸入分辨率小于輸出分辨率,則可能采用的解決方案就是使用畫中畫。例如,我們可以添加藍(lán)色背景,然后使輸入居中。

設(shè)計(jì)的硬件與示例 1 中的硬件相同。

在這個(gè)應(yīng)用中,TPG IP被設(shè)置為可以生成分辨率為640x480的視頻(而HDMI輸出分辨率固定為800x600)

//Configure the TPG app_hdmi_conf_tpg(&tpg_inst,480,640, 0x2, XTPG_BKGND_COLOR_BARS);

我們需要做的第一件事就是用背景的藍(lán)色填充幀緩存。

這是通過(guò)代碼中的以下行來(lái)完成的:

UINTPTR Addr1=0x10000000,Addr2=0x10200000,Addr3=0x10400000;

…

print("Initialize frame buffer data...");

//Disable the data cache to initialize the frame buffer with a blue color

Xil_DCacheDisable();

//Write a blue background in the memory

for(line=0; line < OUTPUT_HEIGHT; line++)

{

for(column=0; column < OUTPUT_WIDTH/2; column++)

{

//Write the blue color to the frame buffer(0x6B1DFF1D in YUV422)

Xil_Out32(Addr1, 0x6B1DFF1D);

Xil_Out32(Addr2, 0x6B1DFF1D);

Xil_Out32(Addr3, 0x6B1DFF1D);

Addr1+=4;

Addr2+=4;

Addr3+=4;

}

}

//Re-enable the data cache

Xil_DCacheEnable();

print("Done

");

您可以看到,在將數(shù)據(jù)寫入內(nèi)存之前,我會(huì)禁用數(shù)據(jù)高速緩存(Xil_DCacheDisable())并在寫入完成后重新啟用它。

寫入或讀入高速緩存存儲(chǔ)器而不是 DDR 存儲(chǔ)器是一個(gè)常見的錯(cuò)誤。使用內(nèi)存時(shí),您需要確保從正確的位置讀取/寫入。

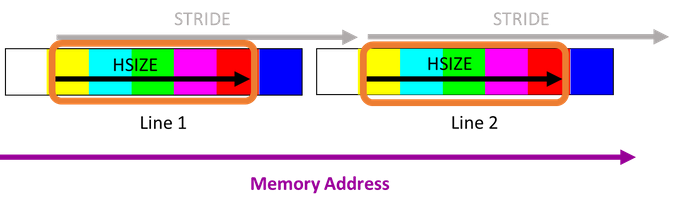

然后,在進(jìn)行 AXI VDMA IP 配置時(shí),我們將執(zhí)行與示例 1 中所執(zhí)行操作相反的操作。

在這個(gè)示例中,我們會(huì)使用寫入接口(而不是前面示例中的讀取接口)上的步幅(現(xiàn)在已與 HSIZE 不同)在 800 * 600背景上正確地寫入內(nèi)存。

對(duì)于緩存存儲(chǔ)器地址,我添加了一個(gè)偏移以便能夠使輸入水平和垂直居中。

//Offset to center the pattern on the buffer

offset = 0x177A0;

//S2MM Start Address 1

Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xAC, 0x10000000 + offset);

//S2MM Start Address 2

Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xB0, 0x10200000 + offset);

//S2MM Start Address 3

Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xB4, 0x10400000 + offset);

//S2MM Frame delay / Stride register

Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xA8, OUTPUT_WIDTH*2);

// S2MM HSIZE register

Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xA4, 640*2);

// S2MM VSIZE register

Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xA0, 480);

示例 3:使用 AXI VDMA IP 的軟模式發(fā)生器

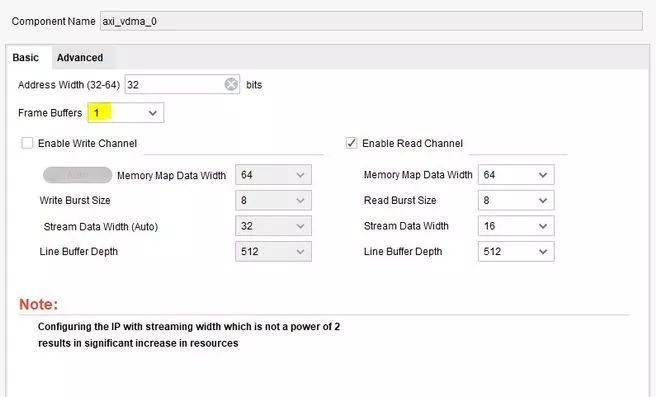

通過(guò)AXI VDMA IP來(lái)實(shí)現(xiàn)在此示例中,AXI VDMA IP 配置為僅啟用讀取接口。

在應(yīng)用開始時(shí),處理器在 DDR 中寫入模式。

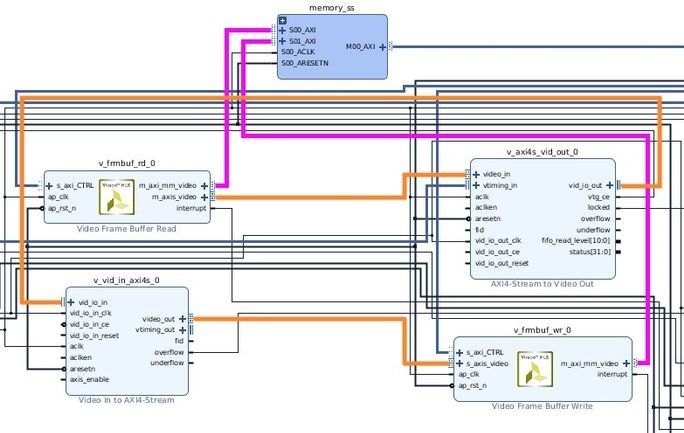

在 Vivado Design 中,我刪除了“測(cè)試模式生成器”:

因?yàn)槲覀冋谧x取一個(gè)靜止模式,所以在 AXI VDMA IP 讀取時(shí)不會(huì)同時(shí)寫入與幀緩存對(duì)應(yīng)的存儲(chǔ)器。因此,AAXI VDMA IP 中只需要一個(gè)幀緩存器。

寫入存儲(chǔ)器的方式與示例 2 中所用的方式類似,在需要訪問(wèn) DDR 存儲(chǔ)器時(shí)禁用高速緩存。

另外請(qǐng)注意,在配置 AXI VDMA IP 的 MM2S 接口時(shí),同步鎖相會(huì)被禁用。

構(gòu)建SDK工作空間和Vivado Designs

注意:這些示例僅針對(duì) ZC702 電路板。

構(gòu)建SDK工程-

從 Windows 菜單中選擇以下內(nèi)容:

“Start > All Program > Xilinx Design Tools > Xilinx Software Command Line Tool 2018.1”。

-

從命令行:

使用 xsct 命令(需要設(shè)置 SDK 2018.1 的環(huán)境變量)。

-

在 xsct 中,使用 cd 導(dǎo)航到您要構(gòu)建的示例的路徑(example_x/sw)。

然后輸入下列命令:

source create_SW_proj.tcl -

打開 SDK,然后選擇“example_x/sw/sdk_workspace”作為工作空間。

-

打開 Vivado 。

-

在 Tcl 控制臺(tái)中,使用 cd 導(dǎo)航到解壓縮的目錄(cd example_x/hw)。

-

在 Tcl 控制臺(tái)中,用 source 來(lái)寫腳本 tcl (source ./create_proj.tcl)。

審核編輯 :李倩

-

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7528瀏覽量

164348 -

分辨率

+關(guān)注

關(guān)注

2文章

1072瀏覽量

42039 -

AXI

+關(guān)注

關(guān)注

1文章

128瀏覽量

16712

原文標(biāo)題:AXI VDMA IP 的高級(jí)用例

文章出處:【微信號(hào):Hack電子,微信公眾號(hào):Hack電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Video Frame Buffer IP初學(xué)者入門案例分析

XILINX FPGA IP之AXI Traffic Generator

AXI VDMA可以工作,但是少數(shù)線路不正確,總是丟包

什么會(huì)導(dǎo)致VDMA(AXI視頻直接存儲(chǔ)器訪問(wèn))的S2MM中的幀計(jì)數(shù)器中斷?

zynq上的AXI視頻直接內(nèi)存訪問(wèn)v6.2 IP

如何將兩個(gè)VDMA的同步鎖相模式和Axi的定時(shí)模式設(shè)置為視頻OUTIP?

PCIE項(xiàng)目中AXI4 IP核例化詳解

如何使用axi tpg和axi vdma?

請(qǐng)問(wèn)如何擴(kuò)展AXI VDMA幀緩沖器?

IP definition not found for VLNV: xilinx.com:ip:axi_vdma:6.2 ERROR: [Common 17-39] 'create_bd_cell' failed due to earlier errors.要如何解決呢

Xilinx VDMA 24位流輸出與32位AXI總線的內(nèi)存流數(shù)據(jù)關(guān)系

PCIE通信技術(shù):通過(guò)AXI-Lite ip配置的VDMA使用

你必須了解的AXI總線詳解

全面介紹ZYNQ-AXI互聯(lián)IP

AXI VDMA IP 的高級(jí)用例

AXI VDMA IP 的高級(jí)用例

評(píng)論