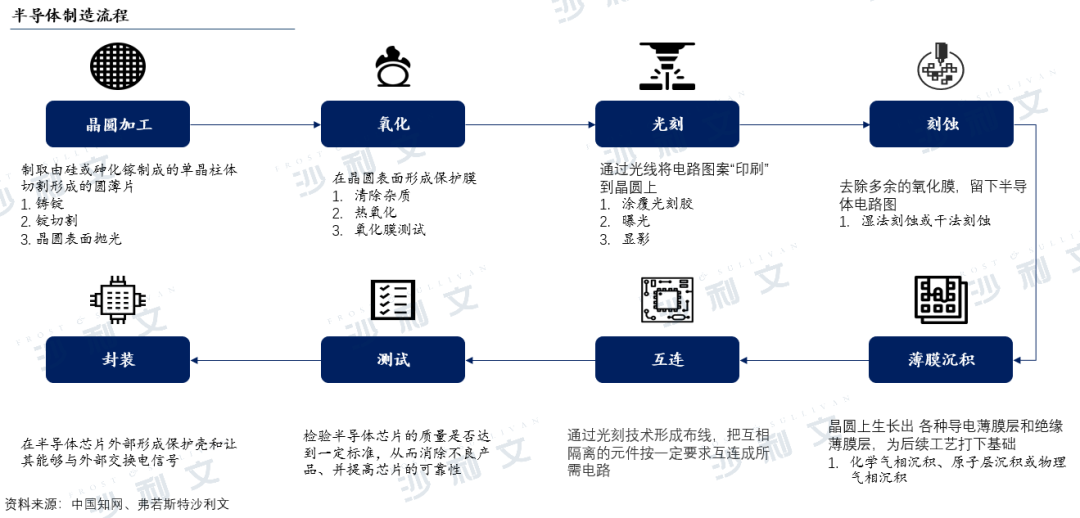

每個(gè)半導(dǎo)體產(chǎn)品的制造都需要數(shù)百個(gè)工藝,整個(gè)制造過(guò)程分為八個(gè)步驟:晶圓加工 - 氧化 - 光刻 -刻蝕 - 薄膜沉積 - 互連 - 測(cè)試 - 封裝。

第一步 晶圓加工

所有半導(dǎo)體工藝都始于一粒沙子!因?yàn)樯匙铀墓枋巧a(chǎn)晶圓所需要的原材料。晶圓是將硅 (Si)或砷化鎵 (GaAs) 制成的單晶柱體切割形成的圓薄片。要提取高純度的硅材料需要用到硅砂,一種二氧化硅含量高達(dá) 95% 的特殊材料,也是制作晶圓的主要原材料。晶圓加工就是制作獲取上述晶圓的過(guò)程。

鑄錠

首 先 需 將 沙 子 加 熱, 分 離 其中的一氧化碳和硅,并不斷重復(fù)該過(guò)程直至獲得超高純度的電子級(jí)硅 (EG-Si)。高純硅熔化成液體,進(jìn)而再凝固成單晶固體形式,稱為“錠”,這就是半導(dǎo)體制造的第一步。硅錠(硅柱)的制作精度要求很高,達(dá)到納米級(jí),其廣泛應(yīng)用的制造方法是提拉法。

錠切割

前一個(gè)步驟完成后,需要用金剛石鋸切掉鑄錠的兩端,再將其切割成一定厚度的薄片。錠薄片直徑?jīng)Q定了晶圓的尺寸,更大更薄的晶圓能被分割成更多的可用單元,有助于降低生產(chǎn)成本。切割硅錠后需在薄片上加入“平坦區(qū)”或“凹痕”標(biāo)記,方便在后續(xù)步驟中以其為標(biāo)準(zhǔn)設(shè)置加工方向。

晶圓表面拋光

通過(guò)上述切割過(guò)程獲得的薄片被稱為“裸片”,即未經(jīng)加工的“原料晶圓”。裸片的表面凹凸不平,無(wú)法直接在上面印制電路圖形。因此,需要先通過(guò)研磨和化學(xué)刻蝕工藝去除表面瑕疵,然后通過(guò)拋光形成光潔的表面,再通過(guò)清洗去除殘留污染物,即可獲得表面整潔的成品晶圓。

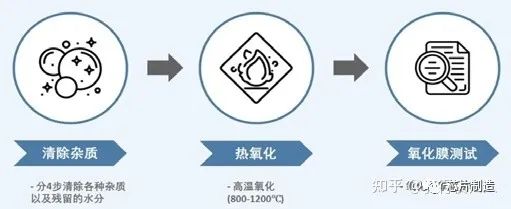

第二步 氧化

氧化過(guò)程的作用是在晶圓表面形成保護(hù)膜。它可以保護(hù)晶圓不受化學(xué)雜質(zhì)影響、避免漏電流進(jìn)入電路、預(yù)防離子植入過(guò)程中的擴(kuò)散以及防止晶圓在刻蝕時(shí)滑脫。氧化過(guò)程的第一步是去除雜質(zhì)和污染物,需要通過(guò)四步去除有機(jī)物、金屬等雜質(zhì)及蒸發(fā)殘留的水分。清潔完成后就可以將晶圓置于 800至 1200 攝氏度的高溫環(huán)境下,通過(guò)氧氣或蒸氣在晶圓表面的流動(dòng)形成二氧化硅(即“氧化物”)層。氧氣擴(kuò)散通過(guò)氧化層與硅反應(yīng)形成不同厚度的氧化層,可以在氧化完成后測(cè)量它的厚度。

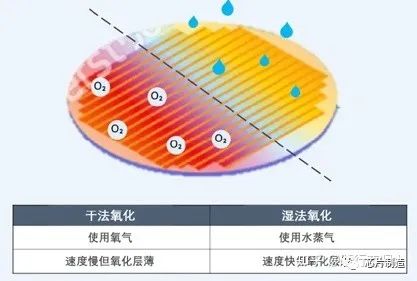

干法氧化和濕法氧化根據(jù)氧化反應(yīng)中氧化劑的不同,熱氧化過(guò)程可分為干法氧化和濕法氧化,前者使用純氧產(chǎn)生二氧化硅層,速度慢但氧化層薄而致密,后者需同時(shí)使用氧氣和高溶解度的水蒸氣,其特點(diǎn)是生長(zhǎng)速度快但保護(hù)層相對(duì)較厚且密度較低。

除氧化劑以外,還有其他變量會(huì)影響到二氧化硅層的厚度。首先,晶圓結(jié)構(gòu)及其表面缺陷和內(nèi)部摻雜濃度都會(huì)影響氧化層的生成速率。此外,氧化設(shè)備產(chǎn)生的壓力和溫度越高,氧化層的生成就越快。在氧化過(guò)程,還需要根據(jù)單元中晶圓的位置而使用假片,以保護(hù)晶圓并減小氧化度的差異。

第三步 光刻

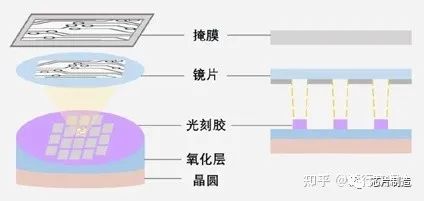

光刻是通過(guò)光線 將 電 路 圖 案“ 印刷”到晶圓上,我們可以將其理解為在晶圓表面繪制半導(dǎo)體制造所需的平面圖。電路圖案的精細(xì)度越高,成品芯片的集成度就越高,必須通過(guò)先進(jìn)的光刻技術(shù)才能實(shí)現(xiàn)。具體來(lái)說(shuō),光刻可分為涂覆光刻膠、曝光和顯影三個(gè)步驟。

涂覆

光刻膠在晶圓上繪制電路的第一步是在氧化層上涂覆光刻膠。光刻膠通過(guò)改變化學(xué)性質(zhì)的方式讓晶圓成為“相紙”。晶圓表面的光刻膠層越薄,涂覆越均勻,可以印刷的圖形就越精細(xì)。這個(gè)步驟可以采用“旋涂”方法。根據(jù)光(紫外線)反應(yīng)性的區(qū)別,光刻膠可分為兩種:正膠和負(fù)膠,前者在受光后會(huì)分解并消失,從而留下未受光區(qū)域的圖形,而后者在受光后會(huì)聚合并讓受光部分的圖形顯現(xiàn)出來(lái)。

曝光

在晶圓上覆蓋光刻膠薄膜后,就可以通過(guò)控制光線照射來(lái)完成電路印刷,這個(gè)過(guò)程被稱為“曝光”。我們可以通過(guò)曝光設(shè)備來(lái)選擇性地通過(guò)光線,當(dāng)光線穿過(guò)包含電路圖案的掩膜時(shí),就能將電路印制到下方涂有光刻膠薄膜的晶圓上。

在曝光過(guò)程中,印刷圖案越精細(xì),最終的芯片就能夠容納更多元件,這有助于提高生產(chǎn)效率并降低單個(gè)元件的成本。在這個(gè)領(lǐng)域,目前備受矚目的新技術(shù)是 EUV 光刻。泛林集團(tuán)與戰(zhàn)略合作伙伴 ASML 和 imec 共同研發(fā)出了一種全新的干膜光刻膠技術(shù)。該技術(shù)能通過(guò)提高分辨率(微調(diào)電路寬度的關(guān)鍵要素)大幅提升 EUV 光刻曝光工藝的生產(chǎn)率和良率。

顯影

曝光之后的步驟是在晶圓上噴涂顯影劑,目的是去除圖形未覆蓋區(qū)域的光刻膠,從而讓印刷好的電路圖案顯現(xiàn)出來(lái)。顯影完成后需要通過(guò)各種測(cè)量設(shè)備和光學(xué)顯微鏡進(jìn)行檢查,確保電路圖繪制的質(zhì)量。

第四步:刻蝕

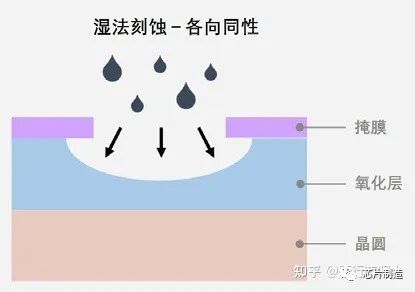

在晶圓上完成電路圖的光刻后, 就要用刻蝕工藝來(lái)去除任何多余的氧化膜且只留下半導(dǎo)體電路圖。要做到這一點(diǎn)需要利用液體、氣體或等離子體來(lái)去除選定的多余部分。刻蝕的方法主要分為兩種,取決于所使用的物質(zhì):使用特定的化學(xué)溶液進(jìn)行化學(xué)反應(yīng)來(lái)去除氧化膜的濕法刻蝕,以及使用氣體或等離子體的干法刻蝕。

濕法刻蝕

使用化學(xué)溶液去除氧化膜的濕法刻蝕具有成本低、刻蝕速度快和生產(chǎn)率高的優(yōu)勢(shì)。然而,濕法刻蝕具有各向同性的特點(diǎn),即其速度在任何方向上都是相同的。這會(huì)導(dǎo)致掩膜(或敏感膜)與刻蝕后的氧化膜不能完全對(duì)齊,因此很難處理非常精細(xì)的電路圖。

干法刻蝕

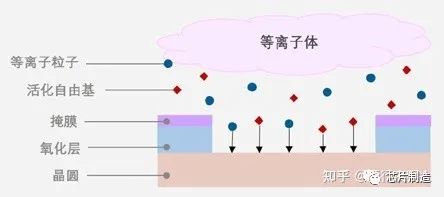

干法刻蝕可分為三種不同類型。第一種為化學(xué)刻蝕,其使用的是刻蝕氣體(主要是氟化氫)。和濕法刻蝕一樣,這種方法也是各向同性的,這意味著它也不適合用于精細(xì)的刻蝕。

第二種方法是物理濺射,即用等離子體中的離子來(lái)撞擊并去除多余的氧化層。作為一種各向異性的刻蝕方法,濺射刻蝕在水平和垂直方向的刻蝕速度是不同的,因此它的精細(xì)度也要超過(guò)化學(xué)刻蝕。但這種方法的缺點(diǎn)是刻蝕速度較慢,因?yàn)樗耆蕾囉陔x子碰撞引起的物理反應(yīng)。

最后的第三種方法就是反應(yīng)離子刻 蝕 (RIE)。RIE結(jié)合了前兩種方法,即在利用等離子體進(jìn)行電離物理刻蝕的同時(shí),借助等離子體活化后產(chǎn)生的自由基進(jìn)行化學(xué)刻蝕。除了刻蝕速度超過(guò)前兩種方法以外,RIE 可以利用離子各向異性的特性,實(shí)現(xiàn)高精細(xì)度圖案的刻蝕。

如今干法刻蝕已經(jīng)被廣泛使用,以提高精細(xì)半導(dǎo)體電路的良率。保持全晶圓刻蝕的均勻性并提高刻蝕速度至關(guān)重要,當(dāng)今最先進(jìn)的干法刻蝕設(shè)備正在以更高的性能,支持最為先進(jìn)的邏輯和存儲(chǔ)芯片的生產(chǎn)。

第五步:薄膜沉積

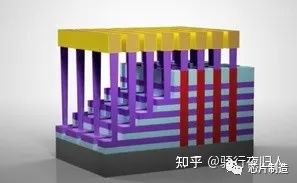

為了創(chuàng)建芯片內(nèi)部的微型器件,我們需要不斷地沉積一層層的薄膜并通過(guò)刻蝕去除掉其中多余的部分,另外還要添加一些材料將不同的器件分離開(kāi)來(lái)。每個(gè)晶體管或存儲(chǔ)單元就是通過(guò)上述過(guò)程一步步構(gòu)建起來(lái)的。我們這里所說(shuō)的“薄膜”是指厚度小于 1 微米(μm,百萬(wàn)分之一米)、無(wú)法通過(guò)普通機(jī)械加工方法制造出來(lái)的“膜”。將包含所需分子或原子單元的薄膜放到晶圓上的過(guò)程就是“沉積”。

要形成多層的半導(dǎo)體結(jié)構(gòu),我們需要先制造器件疊層, 即在晶圓表面交替堆疊多層薄金屬(導(dǎo)電)膜和介電(絕緣)膜,之后再通過(guò)重復(fù)刻蝕工藝去除多余部分并形成三維結(jié)構(gòu)。可用于沉積過(guò)程的技術(shù)包括化學(xué)氣相沉積 (CVD)、原子層沉積 (ALD) 和物理氣相沉積(PVD),采用這些技術(shù)的方法又可以分為干法和濕法沉積兩種。

化學(xué)氣相沉積

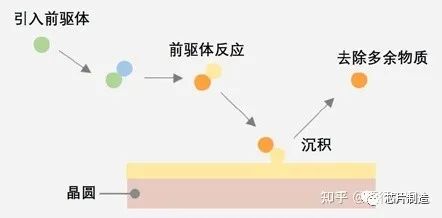

在化學(xué)氣相沉積中,前驅(qū)氣體會(huì)在反應(yīng)腔發(fā)生化學(xué)反應(yīng)并生成附著在晶圓表面的薄膜以及被抽出腔室的副產(chǎn)物。等離子體增強(qiáng)化學(xué)氣相沉積則需要借助等離子體產(chǎn)生反應(yīng)氣體。這種方法降低了反應(yīng)溫度,因此非常適合對(duì)溫度敏感的結(jié)構(gòu)。使用等離子體還可以減少沉積次數(shù),往往可以帶來(lái)更高質(zhì)量的薄膜。

原子層沉積

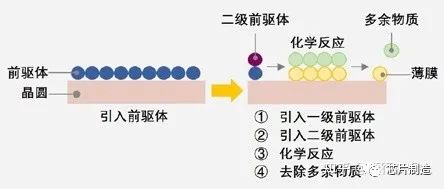

原子層沉積通過(guò)每次只沉積幾個(gè)原子層從而形成薄膜。該方法的關(guān)鍵在于循環(huán)按一定順序進(jìn)行的獨(dú)立步驟并保持良好的控制。在晶圓表面涂覆前驅(qū)體是第一步,之后引入不同的氣體與前驅(qū)體反應(yīng)即可在晶圓表面形成所需的物質(zhì)。

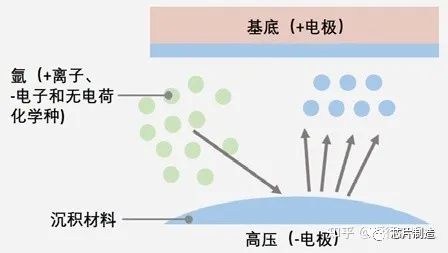

物理氣相沉積

顧名思義,物理氣相沉積是指通過(guò)物理手段形成薄膜。濺射就是一種物理氣相沉積方法,其原理是通過(guò)氬等離子體的轟擊讓靶材的原子濺射出來(lái)并沉積在晶圓表面形成薄膜。在某些情況下,可以通過(guò)紫外線熱處理(UVTP) 等技術(shù)對(duì)沉積膜進(jìn)行處理并改善其性能。

第六步 互連

半導(dǎo)體的導(dǎo)電性處于導(dǎo)體與非導(dǎo)體(即絕緣體)之間,這種特性使我們能完全掌控電流。通過(guò)基于晶圓的光刻、刻蝕和沉積工藝可以構(gòu)建出晶體管等元件,但還需要將它們連接起來(lái)才能實(shí)現(xiàn)電力與信號(hào)的發(fā)送與接收。

金屬因其具有導(dǎo)電性而被用于電路互連。用于半導(dǎo)體的金屬需要滿足以下條件:

· 低電阻率:由于金屬電路需要傳遞電流,因此其中的金屬應(yīng)具有較低的電阻。 · 熱化學(xué)穩(wěn)定性:金屬互連過(guò)程中金屬材料的屬性必須保持不變。

· 高可靠性:隨著集成電路技術(shù)的發(fā)展,即便是少量金屬互連材料也必須具備足夠的耐用性。

· 制造成本:即使已經(jīng)滿足前面三個(gè)條件,材料成本過(guò)高的話也無(wú)法滿足批量生產(chǎn)的需要。

互連工藝主要使用鋁和銅這兩種物質(zhì)。

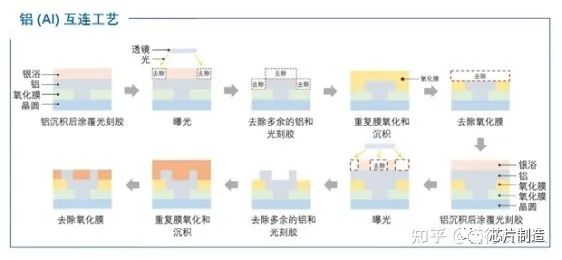

鋁互連工藝

鋁互連工藝始于鋁沉積、光刻膠應(yīng)用以及曝光與顯影,隨后通過(guò)刻蝕有選擇地去除任何多余的鋁和光刻膠,然后才能進(jìn)入氧化過(guò)程。前述步驟完成后再不斷重復(fù)光刻、刻蝕和沉積過(guò)程直至完成互連。

除了具有出色的導(dǎo)電性,鋁還具有容易光刻、刻蝕和沉積的特點(diǎn)。此外,它的成本較低,與氧化膜粘附的效果也比較好。其缺點(diǎn)是容易腐蝕且熔點(diǎn)較低。另外,為防止鋁與硅反應(yīng)導(dǎo)致連接問(wèn)題,還需要添加金屬沉積物將鋁與晶圓隔開(kāi),這種沉積物被稱為“阻擋金屬”。

鋁電路是通過(guò)沉積形成的。晶圓進(jìn)入真空腔后,鋁顆粒形成的薄膜會(huì)附著在晶圓上。這一過(guò)程被稱為“氣相沉積 (VD) ”,包括化學(xué)氣相沉積和物理氣相沉積。

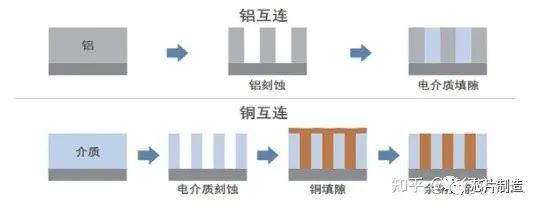

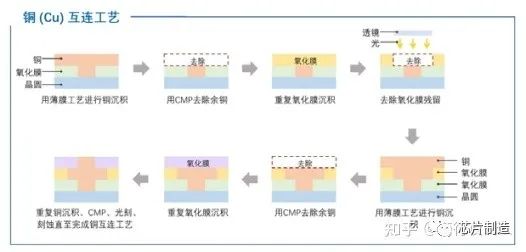

銅互連工藝

隨著半導(dǎo)體工藝精密度的提升以及器件尺寸的縮小,鋁電路的連接速度和電氣特性逐漸無(wú)法滿足要求,為此我們需要尋找滿足尺寸和成本兩方面要求的新導(dǎo)體。銅之所以能取代鋁的第一個(gè)原因就是其電阻更低,因此能實(shí)現(xiàn)更快的器件連接速度。其次銅的可靠性更高,因?yàn)樗蠕X更能抵抗電遷移,也就是電流流過(guò)金屬時(shí)發(fā)生的金屬離子運(yùn)動(dòng)。

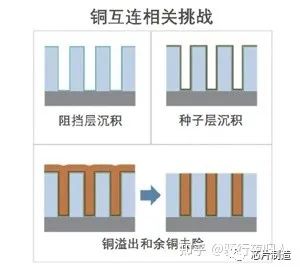

但是,銅不容易形成化合物,因此很難將其氣化并從晶圓表面去除。針對(duì)這個(gè)問(wèn)題,我們不再去刻蝕銅,而是沉積和刻蝕介電材料,這樣就可以在需要的地方形成由溝道和通路孔組成的金屬線路圖形,之后再將銅填入前述“圖形”即可實(shí)現(xiàn)互連,而最后的填入過(guò)程被稱為“鑲嵌工藝”。

隨著銅原子不斷擴(kuò)散至電介質(zhì),后者的絕緣性會(huì)降低并產(chǎn)生阻擋銅原子繼續(xù)擴(kuò)散的阻擋層。之后阻擋層上會(huì)形成很薄的銅種子層。到這一步之后就可以進(jìn)行電鍍,也就是用銅填充高深寬比的圖形。填充后多余的銅可以用金屬化學(xué)機(jī)械拋光 (CMP) 方法去除,完成后即可沉積氧化膜,多余的膜則用光刻和刻蝕工藝去除即可。前述整個(gè)過(guò)程需要不斷重復(fù)直至完成銅互連為止。

通過(guò)上述對(duì)比可以看出,銅互連和鋁互連的區(qū)別在于,多余的銅是通過(guò)金屬 CMP 而非刻蝕去除的。

第七步 測(cè)試

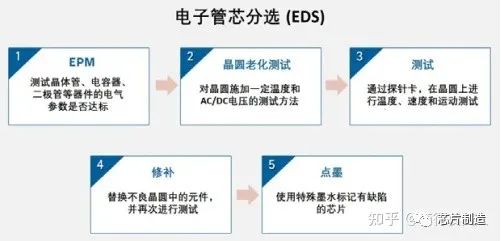

測(cè)試的主要目標(biāo)是檢驗(yàn)半導(dǎo)體芯片的質(zhì)量是否達(dá)到一定標(biāo)準(zhǔn),從而消除不良產(chǎn)品、并提高芯片的可靠性。另外,經(jīng)測(cè)試有缺陷的產(chǎn)品不會(huì)進(jìn)入封裝步驟,有助于節(jié)省成本和時(shí)間。電子管芯分選 (EDS) 就是一種針對(duì)晶圓的測(cè)試方法。

EDS 是一種檢驗(yàn)晶圓狀態(tài)中各芯片的電氣特性并由此提升半導(dǎo)體良率的工藝。EDS可分為五步,具體如下:

01 電氣參數(shù)監(jiān)控 (EPM)

EPM 是半導(dǎo)體芯片測(cè)試的第一步。該步驟將對(duì)半導(dǎo)體集成電路需要用到的每個(gè)器件(包括晶體管、電容器和二極管)進(jìn)行測(cè)試,確保其電氣參數(shù)達(dá)標(biāo)。EPM 的主要作用是提供測(cè)得的電氣特性數(shù)據(jù),這些數(shù)據(jù)將被用于提高半導(dǎo)體制造工藝的效率和產(chǎn)品性能(并非檢測(cè)不良產(chǎn)品)。

02 晶圓老化測(cè)試

半導(dǎo)體不良率來(lái)自兩個(gè)方面,即制造缺陷的比率(早期較高)和之后整個(gè)生命周期發(fā)生缺陷的比率。晶圓老化測(cè)試是指將晶圓置于一定的溫度和 AC/DC 電壓下進(jìn)行測(cè)試,由此找出其中可能在早期發(fā)生缺陷的產(chǎn)品,也就是說(shuō)通過(guò)發(fā)現(xiàn)潛在缺陷來(lái)提升最終產(chǎn)品的可靠性。

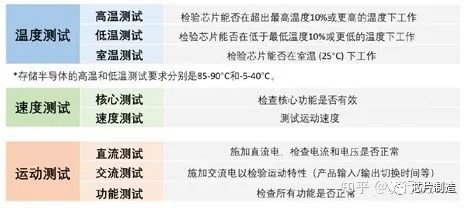

03 檢測(cè)

老化測(cè)試完成后就需要用探針卡將半導(dǎo)體芯片連接到測(cè)試裝置,之后就可以對(duì)晶圓進(jìn)行溫度、速度和運(yùn)動(dòng)測(cè)試以檢驗(yàn)相關(guān)半導(dǎo)體功能。具體測(cè)試步驟的說(shuō)明請(qǐng)見(jiàn)表格。

04 修補(bǔ)

修補(bǔ)是最重要的測(cè)試步驟,因?yàn)槟承┎涣夹酒强梢孕迯?fù)的,只需替換掉其中存在問(wèn)題的元件即可。

05 點(diǎn)墨

未能通過(guò)電氣測(cè)試的芯片已經(jīng)在之前幾個(gè)步驟中被分揀出來(lái),但還需要加上標(biāo)記才能區(qū)分它們。過(guò)去我們需要用特殊墨水標(biāo)記有缺陷的芯片,保證它們用肉眼即可識(shí)別,如今則是由系統(tǒng)根據(jù)測(cè)試數(shù)據(jù)值自動(dòng)進(jìn)行分揀。

第八步 封裝

經(jīng)過(guò)之前幾個(gè)工藝處理的晶圓上會(huì)形成大小相等的方形芯片(又稱“單個(gè)晶片”)。下面要做的就是通過(guò)切割獲得單獨(dú)的芯片。剛切割下來(lái)的芯片很脆弱且不能交換電信號(hào),需要單獨(dú)進(jìn)行處理。這一處理過(guò)程就是封裝,包括在半導(dǎo)體芯片外部形成保護(hù)殼和讓它們能夠與外部交換電信號(hào)。整個(gè)封裝制程分為五步,即晶圓鋸切、單個(gè)晶片附著、互連、成型和封裝測(cè)試。

01 晶圓鋸切

要想從晶圓上切出無(wú)數(shù)致密排列的芯片,我們首先要仔細(xì)“研磨”晶圓的背面直至其厚度能夠滿足封裝工藝的需要。研磨后,我們就可以沿著晶圓上的劃片線進(jìn)行切割,直至將半導(dǎo)體芯片分離出來(lái)。

晶圓鋸切技術(shù)有三種:刀片切割、激光切割和等離子切割。刀片切割是指用金剛石刀片切割晶圓,這種方法容易產(chǎn)生摩擦熱和碎屑并因此損壞晶圓。激光切割的精度更高,能輕松處理厚度較薄或劃片線間距很小的 晶 圓。等離子切割采用等離子刻蝕的原 理,因此即使劃片線間距非常小,這種技術(shù)同樣能適用。

02 單個(gè)晶片附著

所有芯片都從晶圓上分離后,我們需要將單獨(dú)的芯片(單個(gè)晶片)附著到基底(引線框架)上。基底的作用是保護(hù)半導(dǎo)體芯片并讓它們能與外部電路進(jìn)行電信號(hào)交換。附著芯片時(shí)可以使用液體或固體帶狀粘合劑。

03 互連

在將芯片附著到基底上之后,我們還需要連接二者的接觸點(diǎn)才能實(shí)現(xiàn)電信號(hào)交換。這一步可以使用的連接方法有兩種:使用細(xì)金屬線的引線鍵合和使用球形金塊或錫塊的倒裝芯片鍵合。引線鍵合屬于傳統(tǒng)方法,倒裝芯片鍵合技術(shù)可以加快半導(dǎo)體制造的速度。

04 成型

完成半導(dǎo)體芯片的連接后,需要利用成型工藝給芯片外部加一個(gè)包裝,以保護(hù)半導(dǎo)體集成電路不受溫度和濕度等外部條件影響。根據(jù)需要制成封裝模具后,我們要將半導(dǎo)體芯片和環(huán)氧模塑料 (EMC) 都放入模具中并進(jìn)行密封。密封之后的芯片就是最終形態(tài)了。

05 封裝測(cè)試

已經(jīng)具有最終形態(tài)的芯片還要通過(guò)最后的缺陷測(cè)試。進(jìn)入最終測(cè)試的全部是成品的半導(dǎo)體芯片。它們將被放入測(cè)試設(shè)備,設(shè)定不同的條件例如電壓、溫度和濕度等進(jìn)行電氣、功能和速度測(cè)試。這些測(cè)試的結(jié)果可以用來(lái)發(fā)現(xiàn)缺陷、提高產(chǎn)品質(zhì)量和生產(chǎn)效率。

封裝技術(shù)的演變

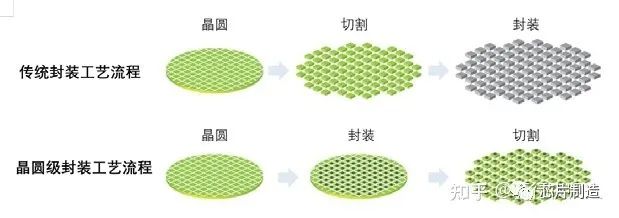

隨著芯片體積的減少和性能要求的提升,封裝在過(guò)去數(shù)年間已經(jīng)歷了多次技術(shù)革新。面向未來(lái)的一些封裝技術(shù)和方案包括將沉積用于傳統(tǒng)后道工藝,例如晶圓級(jí)封裝 (WLP)、 凸塊工藝和重布線層(RDL)技術(shù),以及用于前道晶圓制造的的刻蝕和清潔技術(shù)。

什么是先進(jìn)封裝?

傳統(tǒng)封裝需要將每個(gè)芯片都從晶圓中切割出來(lái)并放入模具中。晶圓級(jí)封裝 (WLP) 則是先進(jìn)封裝技術(shù)的一種 , 是指直接封裝仍在晶圓上的芯片。WLP 的流程是先封裝測(cè)試,然后一次性將所有已成型的芯片從晶圓上分離出來(lái)。與傳統(tǒng)封裝相比,WLP 的優(yōu)勢(shì)在于更低的生產(chǎn)成本。

先進(jìn)封裝可劃分為 2D 封裝、2.5D 封裝和 3D 封裝。

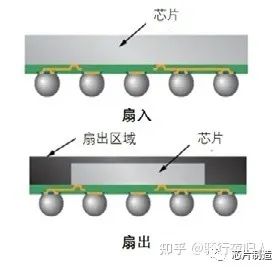

更小的 2D 封裝

如前所述,封裝工藝的主要用途包括將半導(dǎo)體芯片的信號(hào)發(fā)送到外部,而在晶圓上形成的凸塊就是發(fā)送輸入 / 輸出信號(hào)的接觸點(diǎn)。這些凸塊分為扇入型 (fan-in) 和扇出型 (fan-out) 兩種,前者的扇形在芯片內(nèi)部,后者的扇形則要超出芯片范圍。我們將輸入/輸出信號(hào)稱為 I/O( 輸入/輸 出), 輸入/輸出數(shù)量稱為 I/O 計(jì)數(shù)。I/O 計(jì)數(shù)是確定封裝方法的重要依據(jù)。如果I/O計(jì)數(shù)低就采用扇入封裝工藝。由于封裝后芯片尺寸變化不大,因此這種過(guò)程又被稱為芯片級(jí)封裝(CSP)或晶圓級(jí)芯片尺寸封裝(WLCSP)。如果 I/O 計(jì)數(shù)較高,則通常要采用扇出型封裝工藝,且除凸塊外還需要重布線層 (RDL) 才能實(shí)現(xiàn)信號(hào)發(fā)送。這就是“扇出型晶圓級(jí)封裝 (FOWLP)”。

2.5D 封裝

2.5D 封裝技術(shù)可以將兩種或更多類型的芯片放入單個(gè)封裝,同時(shí)讓信號(hào)橫向傳送,這樣可以提升封裝的尺寸和性能。最廣泛使用的 2.5D封裝方法是通過(guò)硅中介層將內(nèi)存和邏輯芯片放入單個(gè)封裝。2.5D 封裝需要硅通孔 (TSV)、微型凸塊和小間距 RDL 等核心技術(shù)。

3D 封裝

3D 封裝技術(shù)可以將兩種或更多類型的芯片放入單個(gè)封裝,同時(shí)讓 信 號(hào) 縱 向 傳 送。這 種 技 術(shù) 適 用于更小和 I/O 計(jì)數(shù)更高的半導(dǎo)體芯片。TSV 可用于 I/O 計(jì)數(shù)高的芯片,引線鍵合可用于 I/O 計(jì)數(shù)低的芯片,并最終形成芯片垂直排列的信號(hào)系統(tǒng)。3D 封裝需要的核心技術(shù)包括 TSV 和微型凸塊技術(shù)。

至此,半導(dǎo)體產(chǎn)品制造的八個(gè)步驟“晶圓加工 - 氧化 - 光刻 - 刻蝕 -薄膜沉積 - 互連 - 測(cè)試 - 封裝”已全部介紹完畢,從“沙粒”蛻變到“芯片”,半導(dǎo)體科技正在上演現(xiàn)實(shí)版“點(diǎn)石成金”。

審核編輯 :李倩

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27711瀏覽量

222651 -

晶圓

+關(guān)注

關(guān)注

52文章

4975瀏覽量

128315 -

封裝技術(shù)

+關(guān)注

關(guān)注

12文章

553瀏覽量

68039

原文標(biāo)題:半導(dǎo)體制造全流程

文章出處:【微信號(hào):半導(dǎo)體封裝工程師之家,微信公眾號(hào):半導(dǎo)體封裝工程師之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

半導(dǎo)體制造里的ALD工藝:比“精”更“精”!

日本半導(dǎo)體制造設(shè)備銷售額預(yù)期上調(diào),創(chuàng)歷史新高!

鎵在半導(dǎo)體制造中的作用

無(wú)塵車間半導(dǎo)體制造設(shè)備的振動(dòng)標(biāo)準(zhǔn)

【「大話芯片制造」閱讀體驗(yàn)】+ 半導(dǎo)體工廠建設(shè)要求

半導(dǎo)體晶圓制造工藝流程

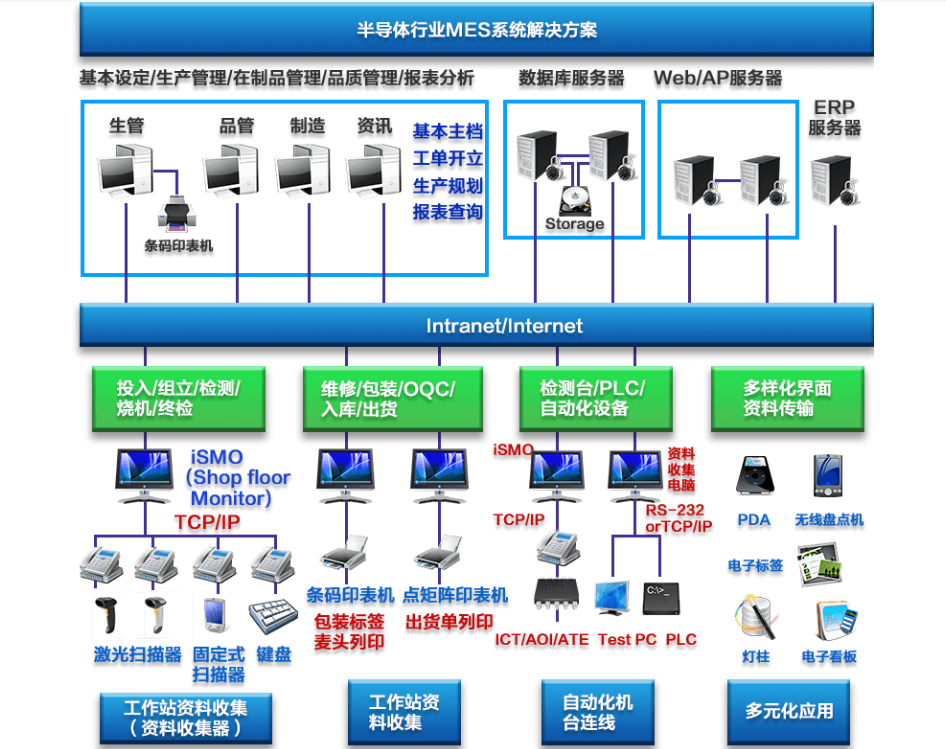

半導(dǎo)體制造行業(yè)MES系統(tǒng)解決方案

半導(dǎo)體制造三要素:晶圓、晶粒、芯片的傳奇故事

ESD靜電對(duì)半導(dǎo)體制造的影響

準(zhǔn)確測(cè)量半導(dǎo)體制造過(guò)程中的水分、濕度和溫度

半導(dǎo)體制造過(guò)程解析

半導(dǎo)體制造設(shè)備革新:機(jī)床需求全面剖析

半導(dǎo)體制造設(shè)備對(duì)機(jī)床的苛刻要求與未來(lái)展望

半導(dǎo)體制造技術(shù)節(jié)點(diǎn):電子科技飛速發(fā)展的幕后英雄

半導(dǎo)體制造全流程

半導(dǎo)體制造全流程

評(píng)論