電源上的高 dV/dt 上升時間會導致下游組件出現(xiàn)問題。在具有大電流輸出驅動器的24V供電工業(yè)和汽車系統(tǒng)中尤其如此。該設計思想描述了如何控制上升時間,同時限制通過控制FET的功率損耗。

限制上升時間

對于許多系統(tǒng)而言,一個簡單的pFET電路和相關元件就足以限制電源的上升時間。但是,當電流達到8A及以上時,R德森的pFET會導致系統(tǒng)中的熱量上升。具有較低 R 的 nFET德森是一個不錯的選擇。

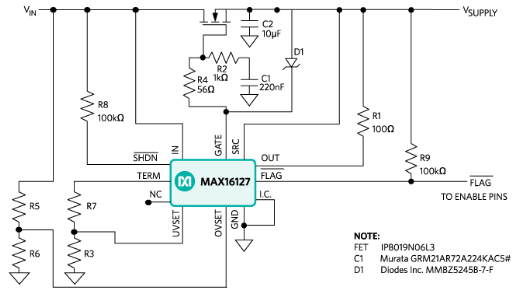

MAX16127為3mm × 3mm nFET控制器,設計用于過壓保護。它還可用于控制電源電壓的斜坡。該保護電路上的電源良好/FLAG輸出使其能夠在受控電壓為輸入電壓的90%時使能下游器件,而與輸入電壓無關。與設置固定導通電壓或延遲時間相比,此功能是一個很好的改進,特別是在輸入電壓可以在很寬范圍內變化的工業(yè)和汽車系統(tǒng)中。

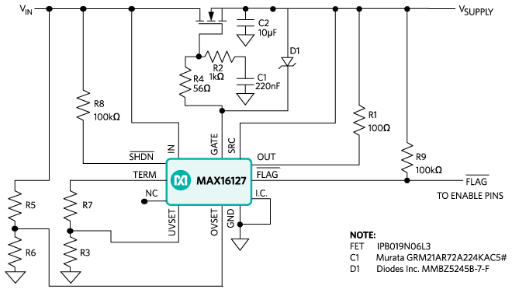

圖1中的電路顯示了用于VIN的基本配置在.MAX16127的GATE引腳為電流輸出電路,來自內部電荷泵。它將 nFET 晶體管的柵極驅動至比 nFET 源極高約 10V 的電壓。GATE上的附加電容可用于控制nFET柵極電壓的上升時間,并且電容的值可以根據(jù)所需的壓擺率進行調整。在本例C1中,顯示的是220nF電容。電阻R2 (1kΩ)與C1串聯(lián)。R2隔離C1,因此當MAX16127在過壓或故障情況下關斷時,關斷時間很快。

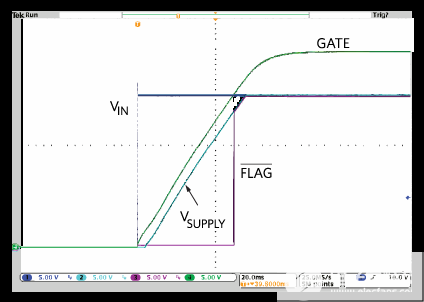

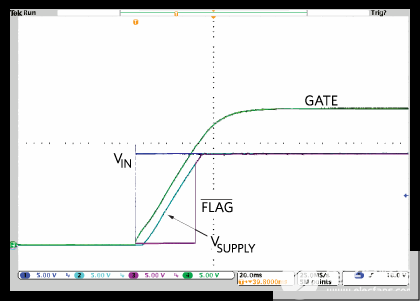

當柵極斜坡時,nFET將處于其線性區(qū)域。因此,如果所有下游電路在斜坡上升時開始工作,則可以看到大量的功耗。MAX16127的/FLAG引腳用作下游驅動器和電源的使能引腳。圖2和圖3顯示了/FLAG使能信號如何及時移出V。在更改,始終啟用當 V供應處于 V 的 90%在.使用/FLAG作為使能時,您只需擔心在一切正常時調整最后10%的nFET大小。

MAX16127的GATE引腳標稱電流為180μA,使用公式計算柵極驅動上升時間:I = C dV/dT。使用所示的220nF電容可獲得約0.82V/ms的dV/dT。圖 2 顯示 V供應在大約40ms內斜坡上升至30V,這接近我們的預期,因為柵極驅動呈線性斜坡上升。

該電路還使用電阻R5和R6提供標準過壓保護,并使用電阻R3和R7提供欠壓鎖定。

圖1.上升時間控制電路原理圖

圖2.30V V 的波形和/FLAG行為在.

圖3.18V V 的波形和/FLAG行為在.

確定場效應管的尺寸

在本例中,我們使用 90% /FLAG 來實現(xiàn) 10A 的下游負載。假設 V 上最大為 30V在,我們需要調整 FET 的大小,以便它可以處理平均功率為 VSUPPLY在大約 4ms 內從 27V 斜坡上升到 30V。平均功率將為 1/2 (VIN - VOUT) × I 或 1.5V × 10A = 15W,但持續(xù)時間很短。大多數(shù)功率 FET 數(shù)據(jù)手冊都有一個安全工作區(qū) (SOA) 圖,其中顯示 VDS與時間疊加的當前相比。檢查 SOA 以調整 FET 的大小。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17836瀏覽量

251783 -

驅動器

+關注

關注

53文章

8271瀏覽量

147056 -

控制器

+關注

關注

112文章

16445瀏覽量

179439

發(fā)布評論請先 登錄

相關推薦

限制穩(wěn)壓器啟動時dV/dt和電容的電路

激光二極管驅動器上升時間控制

功率MOSFET的開關損耗:開通損耗

2線總線上升時間加速電路

淺談振蕩上升時間及影響

高速功率器件的dv/dt和di/dt到底有多大?

擺脫高dV/dt電源的優(yōu)勢

運放輸出電壓上升時間的計算指南

納米軟件電源模塊測試用例分享:如何測試電源上升時間?

信號頻率和上升時間的關系

電源模塊電壓上升時間測試方法

請問示波器怎么測量波形上升時間?

信號上升時間與帶寬的關系 一文看懂!!!

如何控制電源dV/dt上升時間同時限制通過控制FET的功率損耗

如何控制電源dV/dt上升時間同時限制通過控制FET的功率損耗

評論