高K介質(zhì) (High-k Dielectric)和替代金屬柵 (RMG)工藝

2007年,Intel 公司宣布在 45nm CMOS 工藝節(jié)點(diǎn)上成功地使用高k氧化鉿基(Hf-oxide Based)介質(zhì)和金屬柵工藝,可以顯著減少柵介質(zhì)泄漏電流和增加?xùn)艑?dǎo)電能力。

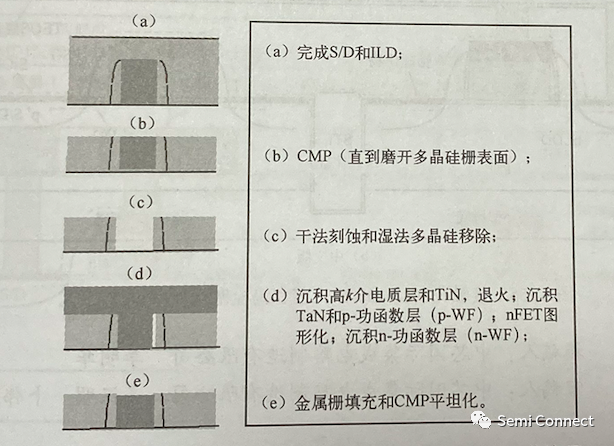

但高k氧化鉿基柵介質(zhì)較易被源漏退火步驟的熱過程引起結(jié)晶化,導(dǎo)致較大的泄漏電流,因此高k介質(zhì)金屬柵模塊工藝需要在源漏之后再形成,這被稱為后柵(Gate Last)工藝或替代金屬柵 ( Replacement Metal Gate, RMG)工藝,如圖所示。

因此,高k介質(zhì)(如 HfO2、HfSiOx、HfSiON)和金屬柵(如TiN、TiAl、Al 或W等)模塊便成為 32nm/28nmn 和更先進(jìn)節(jié)點(diǎn)上的標(biāo)準(zhǔn)配備;后柵工藝或替代金屬柵工藝也成為產(chǎn)業(yè)界先進(jìn) CMOS 工藝節(jié)點(diǎn)(28nm 節(jié)點(diǎn)之后)采用的主流工藝方案。

審核編輯:劉清

-

CMOS

+關(guān)注

關(guān)注

58文章

5735瀏覽量

236092 -

AMOL

+關(guān)注

關(guān)注

0文章

2瀏覽量

8622 -

RMGI

+關(guān)注

關(guān)注

0文章

2瀏覽量

5401

原文標(biāo)題:中段集成工藝(MOL Integration Flow)- 2

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

高k金屬柵(HKMG)工藝詳解

什么是本體偏壓/次臨界漏電 (ISUBTH)/High-k

HKMG實(shí)現(xiàn)工藝的兩大流派及其詳解

高介電常數(shù)柵電介質(zhì)/金屬柵極的FA CMP技術(shù)

IMEC發(fā)布后柵極HKMG制式細(xì)節(jié),英特爾、三星受益

現(xiàn)代集成電路芯片14nm節(jié)點(diǎn)FinFET的制造工藝流程詳細(xì)資料說明

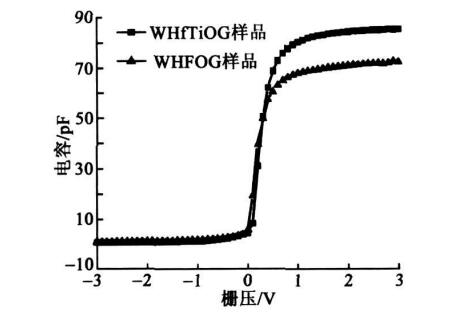

一文讀懂HfTiO高柵介質(zhì)GeMOS電容

集成電路制造工藝的演進(jìn)

海力士:引領(lǐng)High-k/Metal Gate工藝變革

高K金屬柵工藝(HKMG)

高k柵介質(zhì)NMOSFET遠(yuǎn)程聲子散射對溝道遷移率的影響

高K金屬柵極的結(jié)構(gòu)、材料、優(yōu)勢以及工藝流程

High-k柵極堆疊技術(shù)的介紹

集成電路新突破:HKMG工藝引領(lǐng)性能革命

高K介質(zhì)(High-k Dielectric)和替代金屬柵(RMG)工藝介紹

高K介質(zhì)(High-k Dielectric)和替代金屬柵(RMG)工藝介紹

評論