01

FPGA基礎(chǔ)知識

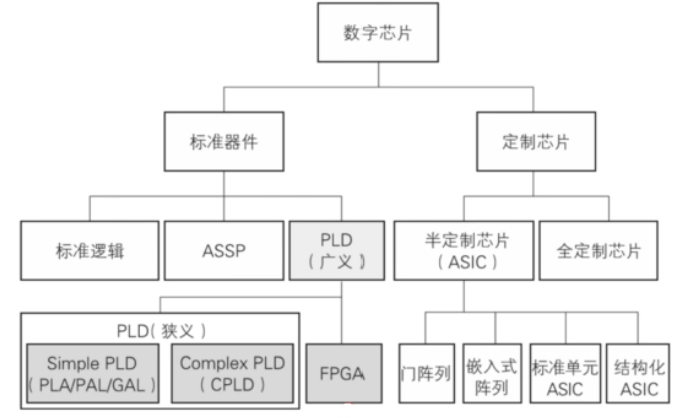

FPGA(Field Programmable Gate Array, 現(xiàn)場可編程邏輯陣列) 是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。

1.1 FPGA與其他相關(guān)可編程器件

1.1.1****FPGA, ASIC和ASSP

ASIC以及ASSP的功能相對固定,是為了專一功能或?qū)R活I(lǐng)域而生,希望對它進(jìn)行任何功能和性能的改善往往是無濟(jì)于事,而FPGA則在產(chǎn)品發(fā)布后仍然可以對產(chǎn)品設(shè)計做出修改,大大方便了產(chǎn)品的更新和針對新的協(xié)議標(biāo)準(zhǔn)做出相應(yīng)改進(jìn),從而加速產(chǎn)品上市時間,并降低產(chǎn)品失敗的風(fēng)險和維護(hù)成本。隨著電子技術(shù)領(lǐng)域的發(fā)展,F(xiàn)PGA也正在向高集成,高性能,低功耗和低價格方向發(fā)展,并逐漸具備了與ASIC,ASSP相當(dāng)?shù)男阅堋?/p>

ASIC: 專用集成電路(Application Specific Integrated Circuit)

ASSP: 專用標(biāo)準(zhǔn)產(chǎn)品(Application Specific Standard Parts)

在嵌入式系統(tǒng)設(shè)計領(lǐng)域,雖然ARM有很多外設(shè),DSP具備強(qiáng)大的信號運算能力,但是這些功能FPGA都可以做到,所以在很多原型產(chǎn)品設(shè)計過程中(靈活性要求高、定制化程度高、性能要求高),會經(jīng)常提出基于FPGA的方案,但是客觀來說,F(xiàn)PGA的成本功耗和開發(fā)復(fù)雜性往往會讓很多用戶望而卻步。

ARM: Advanced RISC Machines,ARM通常包含一顆強(qiáng)大的處理器內(nèi)核,并且為這顆處理器量身配套了很多成熟的軟件工具以及高級編程語言,同時在ARM內(nèi)核處理器周邊,各種各樣精于控制的外設(shè)很多,如GPIO,PWM,AD/DA,UART,SPI,I2C等,使得ARM在控制和管理上有很大優(yōu)勢。

DSP: Digital Signal Processor, 即數(shù)字信號處理器,是一種獨特的微處理器,有自己完整的指令系統(tǒng),能夠進(jìn)行高速高吞吐量的數(shù)字信號處理,因此適合對各種語音,數(shù)據(jù)和視頻做運算處理。

**1.1.3 **FPGA和PLD

PLD重構(gòu)基于門級陣列(Gate Array),屬于門級,即邏輯門是固定的,只有布線是可重構(gòu)編程的,因此布線冗余較多;而FPGA重構(gòu)基于查找表(LUT),屬于邏輯簇級,即布線是固定的,而邏輯是可重構(gòu)編程的,因此相對與PLD而言布線冗余較少,更適合構(gòu)建大規(guī)模邏輯電路。

1.2 FPGA主流開發(fā)語言

**1.2.1 **VHDL

VHDL(VHSIC hardware description language)語言誕生于1983年,1987年被美國國防部和IEEE確定為標(biāo)準(zhǔn)的硬件描述語言。自從IEEE發(fā)布了VHDL的第一個標(biāo)準(zhǔn)版本IEEE 1076-1987后,各大EDA公司都先后推出了自己支援 VHDL 的 EDA 工具。VHDL 在電子設(shè)計行業(yè)得到了廣泛的認(rèn)同。此后IEEE又先后發(fā)布了IEEE 1076-1993和IEEE 1076-2000版本。

VHDL優(yōu)點:語法嚴(yán)謹(jǐn),層次結(jié)構(gòu)清晰。

VHDL缺點:不夠靈活,熟悉時間長。

**1.2.2 **Verilog HDL

Verilog HDL誕生于1983年,由Gateway設(shè)計自動化公司的工程師創(chuàng)立,菲爾·莫比(PhilMoorby)完成了Verilog的主要設(shè)計工作。1990年代初,開放Verilog國際(Open Verilog International, OVI)組織(即現(xiàn)在的Accellera)成立,Verilog面向公有領(lǐng)域開放。

1992年該組織尋求將Verilog納入電氣電子工程師學(xué)會標(biāo)準(zhǔn) ,于是Verilog最終成為了電氣電子工程師學(xué)會1364-1995標(biāo)準(zhǔn)(即Verilog-95)。后來Verilog經(jīng)過多次版本更新,具備了一些新的實用功能,目前,Verilog-2001是Verilog的最主流版本,被大多數(shù)商業(yè)電子設(shè)計自動化軟件包支持。2009年IEEE 1364-2005和IEEE 1800-2005兩個部分合并為IEEE 1800-2009,成為了一個新的、統(tǒng)一的SystemVerilog硬件描述驗證語言(hardware description and verification language, HDVL)。

Verilog 優(yōu)點:類C語言,上手快速,易于使用。

Verilog 缺點:存在不能通過編譯識別的錯誤。

1.3 FPGA器件主流企業(yè)

目前Altera(已被Intel公司收購)和Xilinx公司(已被AMD收購)是FPGA器件主流廠商,兩家公司的可編程邏輯器件占到全球市場的近80%,其中Xilinx FPGA占近50%,而Altera占近30%。除這兩家龍頭企業(yè)外,偶爾也會有一些后來者,例如Lattice,京微雅格等。盡管不同公司的FPGA器件內(nèi)部結(jié)構(gòu)有所差異,但在開發(fā)流程、開發(fā)工具乃至原廠提供的各種支持上都大同小異,因此只要掌握FPGA的開發(fā)流程,任何廠商的器件都可以輕松上手。

02

FPGA基本架構(gòu)

2.1 Xilinx FPGA基本架構(gòu)

Xilinx的FPGA主要由可配置邏輯塊(CLB)、時鐘管理模塊(CMT)、存儲器(RAM/FIFO)、數(shù)字信號處理模塊(DSP)和一些專用模塊組成。

**2.1.1 **可配置邏輯塊(CLB)

Xilinx FPGA邏輯是由陣列排布的CLB實現(xiàn)的,每一個CLB單元都和一個開關(guān)陣列相連,并受其控制從而實現(xiàn)邏輯功能。

CLB由基本結(jié)構(gòu)Slice構(gòu)成,而基本結(jié)構(gòu)中又包含有查找表(LUT),存儲單元,廣函數(shù)多路器(Wide function Multiplexer)和進(jìn)位邏輯,這種基本結(jié)構(gòu)成為SLICEL。有些基本結(jié)構(gòu)中還包含舒勇RAM存儲數(shù)據(jù)的功能和使用32位寄存器移位功能,這種基本結(jié)構(gòu)成為SLICEM。

2.1.2 時鐘管理模塊(CMT)

時鐘管理模塊(CMT)用于產(chǎn)生高質(zhì)量的時鐘,通常CMT會包含數(shù)字時鐘管理模塊(DCM)和鎖相環(huán)電路(PLL),從而實現(xiàn)時鐘的倍頻與分頻。

2.1.3 存儲器(RAM/FIFO)

Xilinx FPGA都有內(nèi)部的存儲器塊,例如Virtex-5內(nèi)部包含若干塊36KB大小可以靈活配置的同步雙口RAM,這些RAM可以配置為多速率的FIFO存儲器,極大地提高了設(shè)計的靈活性。

2.1.4 數(shù)字信號處理模塊(DSP)

Xilinx FPGA中大多包含DSP資源模塊,對于需要大量算法運算的應(yīng)用,F(xiàn)PGA內(nèi)部這類乘法運算單元就顯得十分實用。例如7系列中最小的計算單元DSP48E1:

2.1.5 其他專用模塊

除了上述模塊外,在現(xiàn)代的Xilinx的FPGA產(chǎn)品中還有一些其他專用模塊,例如:Rocket IO千兆位級收發(fā)器、PCI Express端點模塊和三態(tài)以太網(wǎng)MAC模塊等。

2.2 Altera FPGA基本架構(gòu)

Altera的FPGA一般由邏輯陣列模塊(LAB)、TriMatrix存儲器模塊(RAM)、數(shù)字信號處理模塊(DSP)和鎖相環(huán)模塊(PLL)組成。

2.2.1 邏輯陣列模塊(LAB)

邏輯陣列模塊(LAB)的主要結(jié)構(gòu)是適應(yīng)邏輯模塊(ALM),還包括一些進(jìn)位鏈和控制邏輯等結(jié)構(gòu)。

ALM中包含查找表(LUT),可編程寄存器,專用全加器,進(jìn)位鏈,共享算術(shù)鏈和寄存器鏈。

**2.2.2 **FPGA, ARM和DSP

類似于Xilinx FPGA器件,Altera FPGA中同樣包括不同大小的嵌入式RAM存儲器資源,可以支持配置各種特性。

2.2.3 數(shù)字信號處理模塊(DSP)

類似于Xilinx FPGA器件,Altera FPGA中同樣含有DSP資源,從而實現(xiàn)多種最大性能和最小邏輯資源利用率的DSP功能。

2.2.4 鎖相環(huán)(PLL)

類似于Xilinx FPGA器件內(nèi)部的時鐘管理模塊,Altera FPGA中同樣具備PLL鎖相環(huán)資源,從而實現(xiàn)高質(zhì)量的時鐘生成。

2.3 LUT實現(xiàn)原理

PLD重構(gòu)基于門級陣列(Gate Array),屬于門級,即邏輯門是固定的,只有布線是可重構(gòu)編程的,因此布線冗余較多;而FPGA重構(gòu)基于查找表(LUT),屬于邏輯簇級,即布線是固定的,而邏輯是可重構(gòu)編程的,因此相對與PLD而言布線冗余較少,更適合構(gòu)建大規(guī)模邏輯電路。

A,B,C有FPGA芯片的管腳輸入后進(jìn)入可編程連線,然后作為地址線連接到LUT,LUT中已經(jīng)事先寫入了所有可能的邏輯結(jié)果,通過地址查找到相應(yīng)的數(shù)據(jù)后輸出,從而實現(xiàn)組合邏輯,而FPGA中的時序邏輯由觸發(fā)器協(xié)助實現(xiàn)。

03

FPGA應(yīng)用領(lǐng)域與優(yōu)勢

3.1 信號采集處理

FPGA的并行處理特性在信號采集與處理方面具有很大的優(yōu)勢,例如一些高速ADC或圖像傳感器的數(shù)據(jù)采集與實時處理。盡管一些高端的嵌入式處理器也可實現(xiàn)信號采集與處理功能,但嵌入式軟件程序的編譯需要耗費更多的時間,在實時性要求較高的數(shù)據(jù)采集處理系統(tǒng)中將難以勝任。相比之下,F(xiàn)PGA的并行處理和可靈活配置的位寬等諸多優(yōu)勢得以顯現(xiàn)。

3.2 通信協(xié)議實現(xiàn)

FPGA在通信協(xié)議的實現(xiàn)上具有更高的靈活性。盡管ARM等嵌入式芯片也可通過一定的協(xié)議進(jìn)行數(shù)據(jù)交互,但這些通信協(xié)議接口大多是固定的,功能也相對有限。FPGA擁有更加豐富的電平接口,易于實現(xiàn)各種各樣不同的協(xié)議,更適合于用戶定制化較高的場景。同時相比于定制化芯片的設(shè)計生產(chǎn),F(xiàn)PGA在成本和周期等各方面都具有一定的優(yōu)勢。

3.3 芯片原型驗證

隨著芯片制造工藝的提升,以及芯片復(fù)雜程度的增加,流片的成本也在不斷攀升。利用FPGA在流片前期進(jìn)行驗證,可以極大的降低流片后芯片出現(xiàn)問題故障的概率,進(jìn)一步節(jié)約芯片制造的成本。

3.4 系統(tǒng)實時控制

FPGA的并行特性在需要實時控制的系統(tǒng)中也發(fā)揮著很大的作用。盡管利用單片機(jī)可以實現(xiàn)對電機(jī)、顯示器等不同執(zhí)行終端的控制,但是單片機(jī)程序所需要的響應(yīng)時間較長。在實時性要求很高的系統(tǒng)中,單片機(jī)的響應(yīng)時間可能會導(dǎo)致系統(tǒng)無法達(dá)到需求標(biāo)準(zhǔn),例如航天圖像系統(tǒng)需要對航天器的工作情況進(jìn)行實時監(jiān)控與評估,F(xiàn)PGA便是很好的選擇。

04

FPGA開發(fā)流程

4.1 需求分析—>模塊劃分

設(shè)計者根據(jù)項目需求,確定所需資源并選定FPGA型號,進(jìn)而根據(jù)目標(biāo)實現(xiàn)功能進(jìn)行模塊劃分。由于FPGA的實現(xiàn)是并行的,對于一個項目的需求往往需要通過多次處理才能實現(xiàn),因此要考慮分成多個模塊以利于后期的代碼升級,維護(hù)以及設(shè)計的綜合優(yōu)化。

4.2 設(shè)計輸入—>綜合優(yōu)化

模塊劃分完成后,需要考慮不同模塊的輸入輸出接口,此時根據(jù)原理圖和相關(guān)硬件手冊,進(jìn)行底層設(shè)計輸入工作。代碼設(shè)計完成后,檢查語法是否無誤,進(jìn)而進(jìn)行代碼的綜合。

綜合是將較高層次的電路描述轉(zhuǎn)化為較低層次的電路描述,即將設(shè)計代碼轉(zhuǎn)化為底層的與門,非門,RAM,觸發(fā)器等基本邏輯單元相互連接而成的網(wǎng)表。

綜合完成后需要進(jìn)行功能仿真。功能仿真不涉及任何時序上的延時,只是單純驗證代碼所實現(xiàn)的功能是否符合要求。

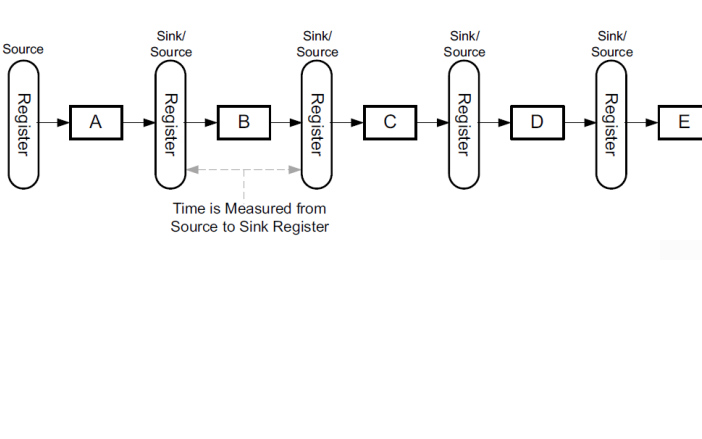

4.3 實現(xiàn)—>時序收斂

功能仿真過后一般會進(jìn)行一次全編譯,然后對工程進(jìn)行約束:包括全局約束(I/O接口約束)和時序約束。添加完時序約束后,需要進(jìn)行實現(xiàn)(翻譯、映射和布局布線),然后查看時序報告。在添加時序約束前后,變化最大的應(yīng)該是布局布線。

一般對于較大的工程,編譯往往耗費很多時間,因此可以查看映射后的時序報告進(jìn)行前期的分析。這個報告的邏輯延時是完全準(zhǔn)確的,布線延時卻是通過一定比例推導(dǎo)得出的估計值,所以由此得到的時序報告并不完全準(zhǔn)確。但是如果得到的估計延時偏大,時序明顯達(dá)不到要求,那么設(shè)計者就應(yīng)該先回頭查找問題,想辦法達(dá)到時序收斂。如果達(dá)到了時序收斂,并且設(shè)計者進(jìn)行了充分的前期功能仿真,那么往下的時序仿真就可以不做,從而節(jié)省了時間。

4.4 仿真測試—>板級調(diào)試

仿真和板級調(diào)試是FPGA設(shè)計的主要驗證手段。盡管板級調(diào)試能夠直觀真實的反映信號狀態(tài),也便于問題的尋找和定位,但是板級調(diào)試同步觀察接口信號數(shù)量受限,而且很難觀測到FPGA內(nèi)部信號節(jié)點的狀態(tài)。因此,仿真在FPGA開發(fā)驗證中有著更重要的作用。

整個設(shè)計的驗證過程如上圖所示:

- 行為仿真的代碼可以是不可綜合的代碼;

- 功能仿真是對成為硬件的門級網(wǎng)表進(jìn)行驗證,但不包含任何布局布線延時信息;

- 時序仿真是在功能仿真的基礎(chǔ)上包含電路的延時信息;

- 板級調(diào)試驗證最終功能是否實現(xiàn)。

前仿真:綜合前仿真,行為仿真

審核編輯 黃昊宇

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

606010 -

pal

+關(guān)注

關(guān)注

1文章

43瀏覽量

27323

發(fā)布評論請先 登錄

相關(guān)推薦

FPGA架構(gòu)及相關(guān)基本概念

天線分集技術(shù)的基本概念介紹

AGV的基本概念及基本結(jié)構(gòu)組成

單片機(jī)中斷的基本概念

STM32的中斷系統(tǒng)基本概念

ARM的體系架構(gòu)基本概念

PCIE基本概念與拓?fù)?b class='flag-5'>架構(gòu)圖

FPGA高級班前言基本原理基本概念

FPGA學(xué)習(xí)教程之硬件設(shè)計基本概念

淺析FPGA架構(gòu)及相關(guān)的基本概念

淺析FPGA架構(gòu)及相關(guān)的基本概念

評論