作者:Vicky Wong and Yoshinori Kusuda

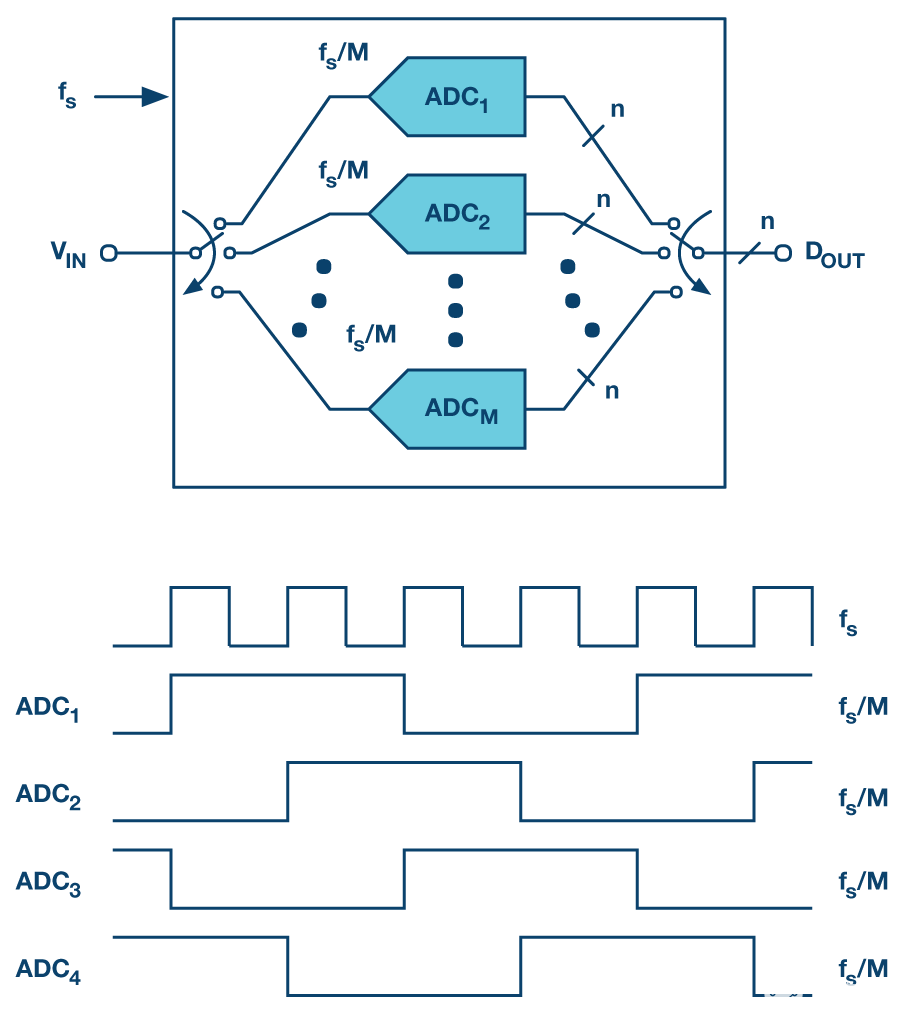

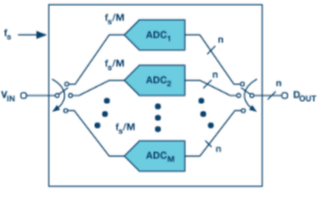

時間交錯是一種允許使用多個相同的模數轉換器的技術[1](ADC)以比每個單獨數據轉換器的工作采樣速率更快的速率處理常規采樣數據系列。簡單來說,時間交錯(IL)包括對M個相同ADC的并行陣列進行時間多路復用,如圖1所示,以實現更高的凈采樣速率。fs(帶采樣周期Ts = 1/fs),即使陣列中的每個 ADC 實際上都以較低的速率采樣(和轉換)fs/米.因此,例如,通過交錯四個10位/100 MSPS ADC,原則上可以實現一個10位/400 MSPS ADC。

為了更好地理解IL的原理,圖1中模擬輸入V。在(t) 由 M ADC 采樣,并得出組合的數字輸出數據序列D外.模數轉換器1將采樣 VIN(t0) 首先開始將其轉換為 n 位數字表示。Ts幾秒鐘后,ADC2將樣本五在(t0+ Ts) 并開始將其轉換為 n 位數字表示形式。然后Ts幾秒鐘后,ADC3將樣本五在(t0+ 2噸s)等等。在 ADCM 對 V 進行采樣后在(t0 + (M – 1) × Ts),下一個采樣周期從ADC1采樣V開始在(t0+ 米 × Ts),這個旋轉木馬繼續。

當ADC的n位輸出按與采樣操作相同的順序提供時,這些數字n位字由同一圖右側所示的解復用器收集。這里重新組合的數據輸出序列D外(t0+ 升),D外(t0+ 升 + 噸s),D外(t0+ L + 2Ts), ...獲得。L代表每個ADC的固定轉換時間,此重新組合的數據序列是具有采樣速率的n位數據系列fs.因此,雖然單個ADC(通常稱為“通道”)是n位ADC,采樣速率為:fs/米,盒子中包含的融合相當于單個n位ADC采樣fs,我們將其稱為時間交錯ADC(將其與通道區分開來)。基本上,輸入由陣列中的ADC進行切片和單獨處理,然后在輸出端一致地重新組裝以形成高數據速率表示D外的輸入V在.

圖1.M時間交錯n位ADC陣列。每個的采樣率為fs/米,得到的時間交錯型ADC的采樣速率為fs.該圖的下半部分描述了M = 4情況下的時鐘方案示例。

這種強大的技術并非沒有實際挑戰。當來自通道的M數據流以數字方式組合在一起以重建原始輸入信號時,關鍵問題就顯現出來了V在.如果我們看一下光譜D外,除了看到數字表示V在 以及模數轉換引入的失真,我們還將看到額外的大量雜散內容,稱為“交錯雜散”(或簡稱IL雜散),IL雜散既不像高階信號諧波那樣具有多項式型失真的特征(2德·, 3RD等),也不是量化或 DNL 錯誤的簽名。IL偽像可以看作是時域固定碼型噪聲的一種形式,是由通道中的模擬損傷引入的,由于交錯過程,這些損傷與切片轉換信號調制,最終出現在最終的數字化輸出中D外.

讓我們通過分析一個簡單的例子來了解可能發生的事情。考慮具有正弦輸入的雙向交錯ADC的情況V在 在頻率f在.假設 ADC1有增益,G1和那個 ADC2有一個不同的增益,G2。在這種雙向IL ADC中,ADC1和 ADC2將在采樣中交替V在.所以如果 ADC1轉換偶數樣本和ADC2轉換奇數樣本,然后轉換所有偶數數據D外振幅由 G 設定1,而所有奇數數據D外 振幅由 G 設定2.然后D外不僅包含V在 以及一些多項式失真,但它一直受到G的交替放大倍率的影響1和 G2就像我們在調幅一樣V在 頻率為方波fs/2.這將引入額外的虛假內容。具體說來D外將包括頻率的“增益雜散”fs/2 –f在不幸的是,該雜散的頻率跟蹤輸入f在 并且它位于交錯 ADC 的第一奈奎斯特帶內(即在fs/2)并且在所有其他奈奎斯特帶上也有它的別名。這種交錯雜散的功率/幅度取決于兩個增益G之間的凈差 1和 G2.換句話說,這取決于增益誤差失配。[2]最后,這取決于輸入的大小V在 本身。

如果輸入不是簡單的正弦波,而是像在實際應用案例中一樣,它是一個全頻段限制信號,那么“增益雜散”不僅僅是一個不需要的音調,而是出現在奈奎斯特頻段內的帶限制輸入信號本身的完整縮放圖像。這在某種程度上抵消了交錯提供的帶寬增加的好處。

雖然在上面的例子中,我們只考慮了通道之間的增益誤差失配,但其他損傷也會引入交錯雜散。失調失配(通道失調之間的差異)在固定頻率下引入音調(“失調雜散”),功率與失調失配成正比。[3]當某些通道的采樣時間比預期順序早于或晚一點時,就會發生采樣時間偏差。這引入了與增益雜散位于相同頻率(并且加起來具有相同幅度)的“定時雜散”。[4]但隨著權力越來越強大f在 隨著輸入幅度的增長而增長。各個通道之間的帶寬不匹配會在頻率上引入更多的雜散內容,具體取決于f在而且,就像時序雜散一樣,雜散功率會隨著f在本身,而不僅僅是輸入幅度。同樣,在所有情況下,輸出頻譜退化的嚴重程度不取決于通道損傷的絕對值(偏移、增益、時序、頻段),而是取決于它們之間的相對不匹配/差異。

雖然時間交錯的一般技術已經存在了幾十年,但IL雜散可以保持在最低限度的程度限制了其過去對低分辨率轉換器的適用性。然而,在通道失配校準和抑制殘余IL雜散成分方面的最新進展,如今可以實現完全集成的超高速12位、14位和16位IL ADC。

此時,我們需要區分某些交錯類。我們一般在兩個交錯通道的情況下稱為“乒乓”操作。然后,我們可以區分“輕度交錯”和“高度交錯”,因為我們指的是通道數量減少的情況(例如,三個通道到四個通道)或大量通道的情況,例如分別說四個以上,通常為八個以上。

乒乓球(雙向)交錯

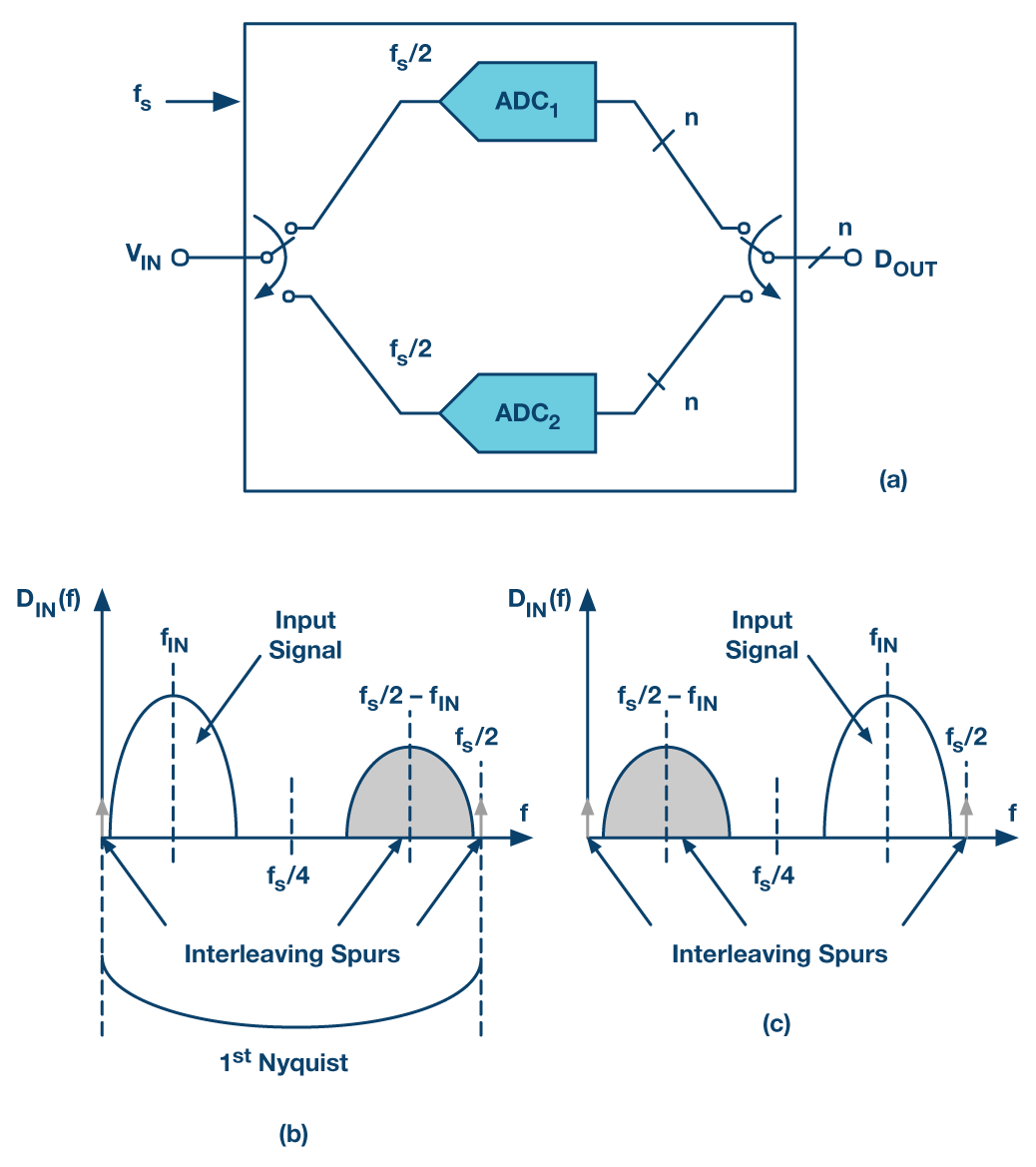

如圖2(a)框圖所示,當我們只交錯兩個通道以使凈采樣率加倍時,我們稱之為“乒乓球”。這是一個特別簡單的案例,具有一些有趣且有用的功能。在這種情況下,在 1圣交錯ADC的奈奎斯特帶,交錯雜散位于直流,在fs/2和在fs/2 –f在.所以,如果輸入信號V在 是窄帶信號,中心在f在,如圖2(b)的第一個奈奎斯特輸出頻譜所示,交錯雜散將包括直流處的偏移雜散,另一個偏移失配雜散位于直流處fs/2,增益和時序雜散鏡像居中fs/2 –f在 這看起來像輸入本身的縮放副本。

如果輸入信號V在(f) 完全綁定在 0 和fs/4,如圖2(b)所示,交錯雜散與數字化輸入的頻率不重疊。在這種情況下,壞消息是我們只能在奈奎斯特波段的一半進行數字化,即就像我們有一個單通道時鐘一樣fs/2,盡管我們仍然消耗至少兩倍于這種單個通道的功率。奈奎斯特波段上端的交錯雜散鏡像可以在數字化后通過數字濾波抑制,并且不需要校正模擬損傷。

然而,好消息是,由于乒乓球ADC的時鐘頻率為:fs,數字化輸出受益于動態范圍內3 dB的處理增益。此外,與使用時鐘頻率為fs/2,乒乓球ADC的抗混疊濾波器設計有所放松。

圖2.(a) 乒乓球方案,(b) 窄帶輸入信號低于時的輸出頻譜fs/4 和 (c) 當輸入信號位于fs/4和奈奎斯特頻率fs/2.

如果窄帶信號位于第一奈奎斯特頻段的上半部分,則可以重復所有相同的考慮因素,如圖2(c)所示,因為交錯圖像雜散移動到奈奎斯特頻段的下半部分。同樣,增益和時序雜散可以在數字化后通過濾波進行數字抑制。

最后,一旦輸入信號頻率位置越過fs/4行。在這種情況下,無法恢復所需的輸入信號,并且乒乓球方案不可用。當然,除非通道間匹配足夠接近,使交錯雜散成分對于應用來說是可接受的低水平,或者采用校準來減少導致IL圖像的原因。

總之,頻率規劃和一些數字濾波允許在乒乓方案中恢復窄帶數字化輸入,即使在存在信道不匹配的情況下也是如此。而與使用時鐘頻率為fs/2,乒乓方案提供3 dB處理增益,放寬抗混疊要求。

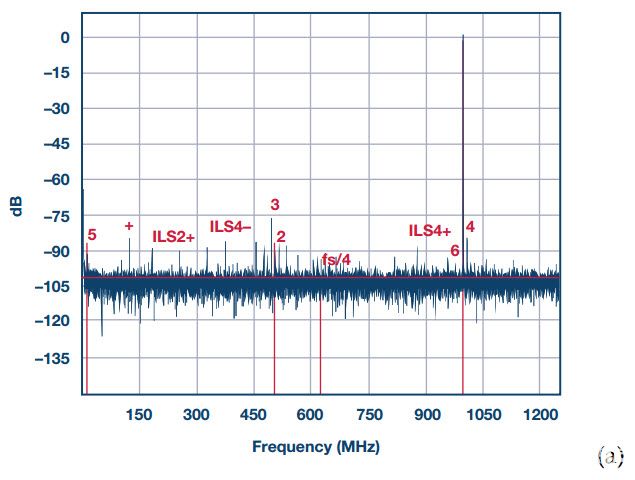

圖3顯示了未對通道失配及其產生的交錯雜散進行任何校正的乒乓球示例。在這種情況下,雙通道14位/1 GSPS ADC AD9680的兩個ADC交替采樣單個正弦波,因此以2 GSPS返回單個組合輸出數據流。當我們看 1圣此乒乓方案輸出頻譜的奈奎斯特頻段(介于直流和 1 GHz 之間)我們可以看到輸入音調,這是左側的強音調f在= 400 MHz,我們還可以看到強烈的增益/時序失配雜散fs/2 –f在= 2G/2 – 400 M = 600 MHz。由于兩個通道自身的失真以及其他損傷,我們還看到了許多其他音調,但這些音調都低于–90 dB線。

圖3.乒乓球方案的2 GSPS組合輸出數據頻譜,方法是用1 GSPS時鐘對AD9680的兩個ADC進行時鐘,但采樣相移為180°。

高階交錯

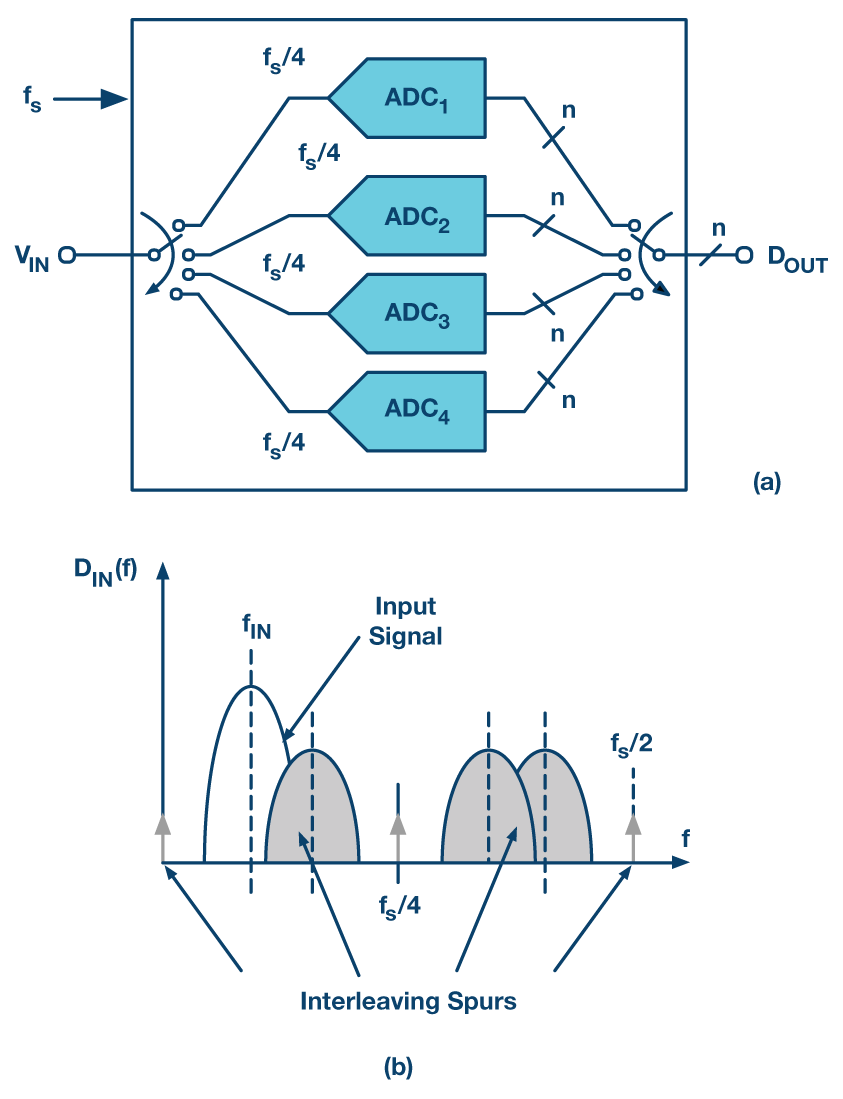

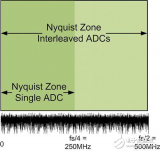

當我們有兩個以上的頻道時,如上所述的頻率規劃不是很實用或有吸引力。交錯雜散的位置不能局限于奈奎斯特帶的一小部分。例如,考慮四路交錯式ADC的情況,如圖4(a)所示。在這種情況下,偏移失配會在直流時產生音調,fs/4和fs/2.而增益和時序交錯圖像位于fs/4 –f在,fs/4 +f在 和fs/2 –f在.交錯式ADC輸出頻譜示例如圖4(b)所示。可以清楚地看到,除非輸入在小于fs/8,無論我們放在哪里f在,輸入將與一些交錯雜散重疊,如果輸入是非常窄帶的信號,我們不應該嘗試使用寬帶交錯ADC對其進行數字化。

在這種情況下,我們需要最小化IL雜散功率,以獲得完整的奈奎斯特和更干凈的頻譜。為此,使用校準技術來補償通道之間的不匹配。隨著失配的影響得到糾正,產生的IL雜散的功率降低。SFDR和SNR都受益于這種雜散功率的降低。

補償方法受到測量和最終糾正不匹配的準確性的限制。為了進一步抑制殘余雜散,使其超出通過校準達到的水平,可以間歇性和隨機地打亂通道對輸入進行采樣的順序。這樣,前面討論的轉換輸入信號由于未校準的失配而產生的調制效應從固定模式噪聲變為偽隨機噪聲。結果,IL音調和不需要的周期性模式變成偽隨機噪聲樣內容,隨著轉換器量化本底噪聲的增加,并導致不需要的雜散圖像和音調消失或至少傳播。在這種情況下,與IL雜散成分相關的功率會增加本底噪聲的功率。因此,雖然失真得到改善,但SNR會因增加噪聲的IL雜散功率而降低。SNDR(SINAD)基本上沒有變化,因為它結合了失真和噪聲以及隨機化;它只是將IL貢獻從一個分量(失真)移動到另一個分量(噪聲)。

圖4.(a) 四路交錯式 ADC 和 (b) 相應的 1圣奈奎斯特輸出頻譜顯示交錯雜散。

我們來考慮一些交錯ADC的例子。AD9625是一款12位/2.5 GSPS三路交錯ADC。校準三個通道之間的失配,以盡量減少交錯雜散。其輸入接近1 GHz時的輸出頻譜示例如圖5(a)所示。在此頻譜中,除了 ~1 GHz 輸入音調外,還可以看到通道的 2德·和 3RD500 MHz 附近的諧波失真和 4千基波附近的諧波失真。交錯失配校準大大降低了交錯雜散的功率,并且在整個頻譜中可以看到大量額外的殘余小雜散音。

為了進一步減少這種殘留雜散成分,引入了信道隨機化。添加第四個校準通道,然后通過間歇性地將其中一個交錯通道與第四個通道交換,以隨機變化的順序對四個通道進行三路交錯。人們可以把它比作一個雜耍演員在空中玩三個 Skittles,而第四個 Skittles 每隔一段時間就會換一次。這樣,殘余交錯雜散功率被隨機化并分布在本底噪聲上。如圖5(b)所示,通道隨機化后,交錯雜散幾乎消失,而噪聲功率略有增加,從而使SNR降低2 dB。當然,請注意,雖然圖5(b)所示的第二個頻譜的失真音調要干凈得多,但洗牌不會影響2德·, 3RD和 4千諧波,因為這些不是交錯雜散。

圖5.AD9625的輸出頻譜,時鐘頻率為2.5 GSPS,輸入音接近1 GHz。 (a) 順序三路交錯;SNR = 60 dBFS,SFDR = 72 dBc 受三次諧波的限制,接近 500 MHz;然而,在整個光譜中可以看到許多交錯雜散。(b) 三向交錯與隨機通道洗牌;SNR = 58 dBFS,而SFDR = 72 dBc仍由三次諧波設定,所有交錯雜散都已通過將其功率分散到本底噪聲中而消除。

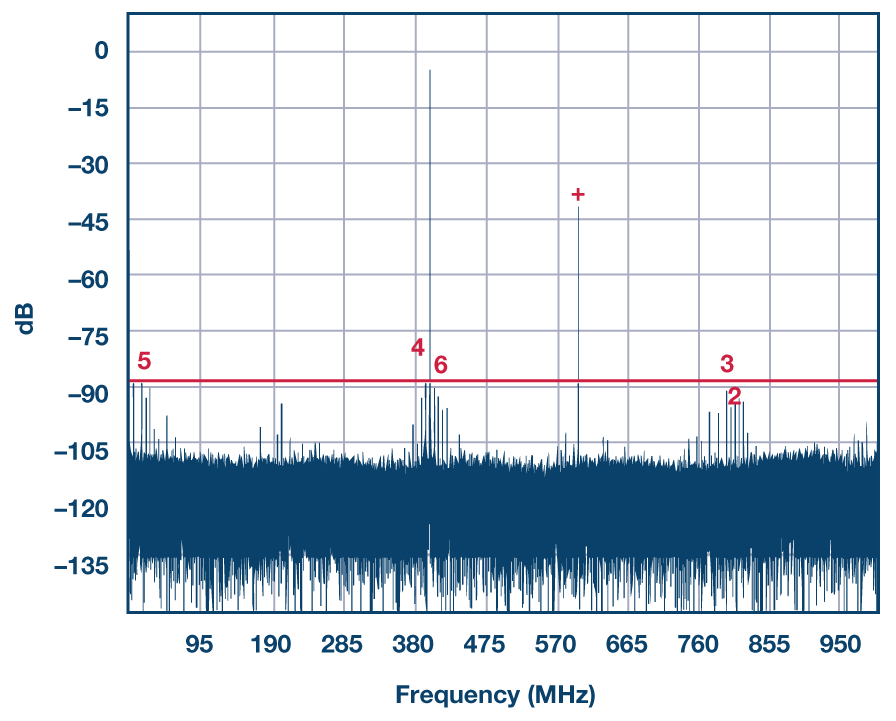

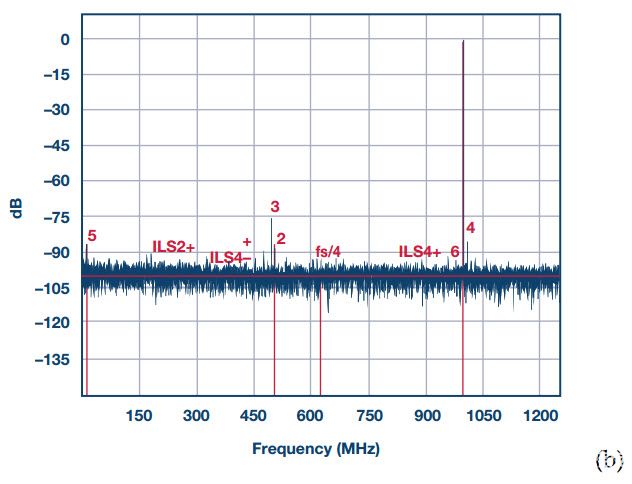

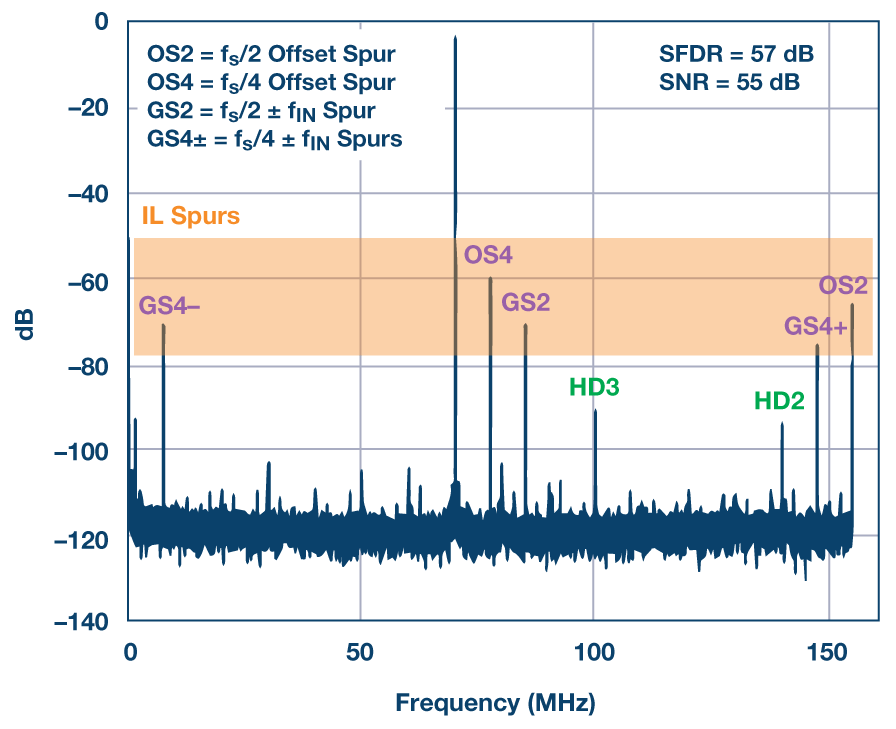

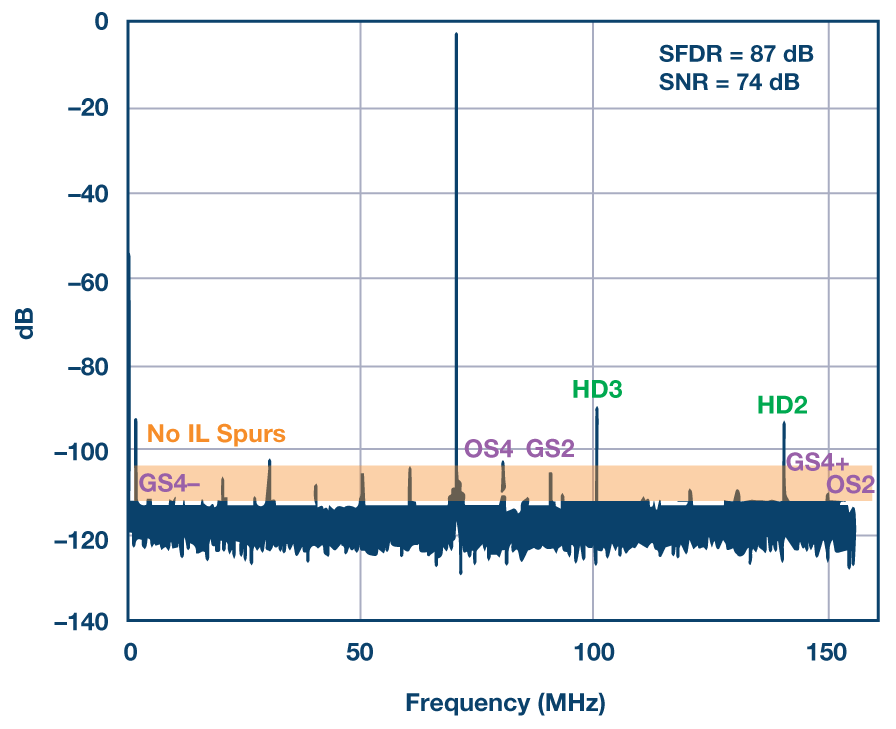

使用通道隨機化的交錯ADC的另一個示例是圖6頻譜所示。四路交錯式16位/310 MSPS ADC AD9652就是這種情況。在圖6所示的情況下,四個通道以固定順序順序交錯,無需努力校準它們以減少通道失配。頻譜清楚地顯示了預測頻率位置處的交錯雜散,其大功率遠大于2德·和 3RD諧波,并將無雜散動態范圍限制在僅57 dBc。

但是,如果對同一ADC進行前臺校準以減少通道失配,則交錯雜散的功率會大大降低,如圖7所示。與前面的例子類似,通道諧波失真不受影響,但是通過通道失配校準,交錯雜散的功率大大降低。

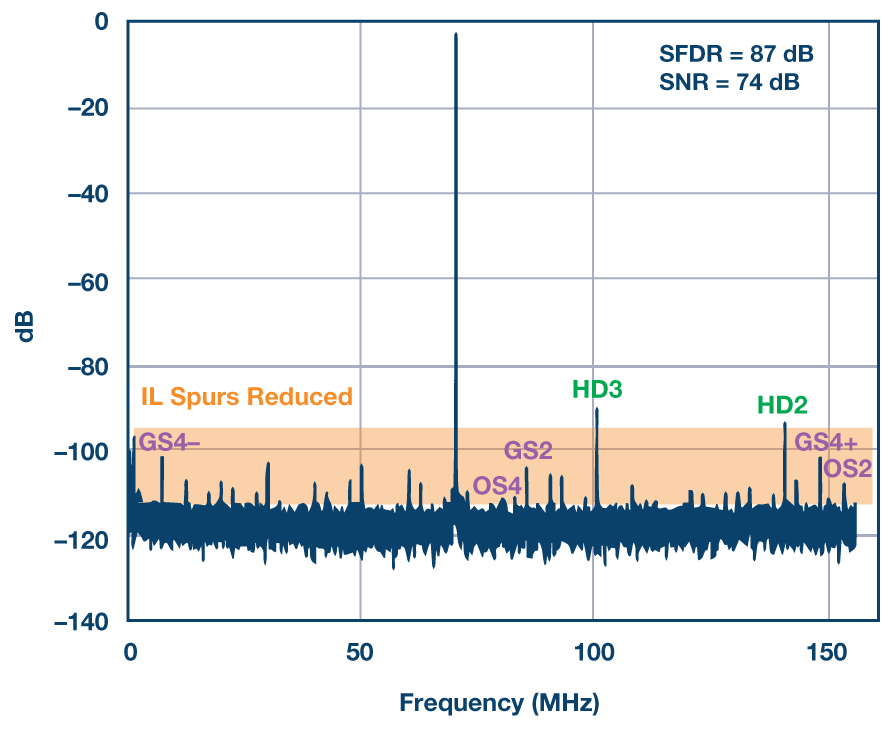

最后,圖7中的頻譜純度可以通過隨機化通道順序進一步提高,如圖8所示。在這種情況下,隨機化使用了一種專有技術,雖然間歇性地擾亂了四個通道的順序,但不需要備用(5千) 通道,從而節省其相關功率。從圖8可以看出,隨機化后,所得頻譜上只剩下常規諧波失真。

圖6.AD9652的輸出頻譜,時鐘為fs= 310 MHz,正弦輸入f在~ 70 兆赫。在這種情況下,不應用通道校準和隨機化。2德·(HD2) 和別名 3RD(HD3)諧波分別在~140 MHz和~100MHz處可見。交錯 (IL) 雜散也可見。這些是直流時的偏移音,fs/2(圖中的 OS2)和fs/4(圖中的OS4)。此外,增益(/時序)雜散可以在fs/2 –f在(圖中GS2),fs/4 +f在(圖中的GS4+)和fs/4 –f在(圖中的GS4)。此圖中的SNR報價人為地較差,因為某些雜散成分與噪聲功率混為一談。

圖7.相同AD9652的輸出頻譜,輸入相同,但經過校準后,四個通道以減少其失配。與圖6相比,而2德·和 3RD諧波不受影響,交錯雜散的功率大幅降低,SFDR從57 dBc提高到87 dBc,提高了30 dB。

圖8.打開交錯順序隨機化后前一種情況的輸出頻譜。對殘余交錯雜散進行隨機化,將其功率分布到本底噪聲上,相應的峰值消失。只剩下常規的諧波失真。SNR幾乎不受影響,因為在失配校準后,交錯音的分布式雜散功率可以忽略不計。

結論

時間交錯是增加數據轉換器帶寬的強大技術。失配補償以及通過隨機化技術消除殘余雜散成分的最新進展使得超高速12位、14位和16位交錯ADC得以完全集成。

在輸入信號受頻帶限制的情況下,例如在許多通信應用中,乒乓(雙向)交錯方法允許通過頻率規劃將不需要的交錯雜散從目標輸入頻帶中分配出來。然后可以對虛假內容進行數字過濾。與非交錯式ADC相比,這種方法消耗的功耗大約是捕獲相同無雜散輸入帶寬所需的IL采樣速率的兩倍,但另一方面,由于IL采樣速率較高,該方法既通過處理增益將動態范圍增加了3 dB,又放寬了ADC之前的抗混疊和屋頂濾波器的滾降。

當需要IL轉換器的全輸入頻段來捕獲寬帶輸入信號時,適合使用高階交錯轉換器。在這種情況下,校準和隨機洗牌允許交錯失真和雜散內容補償和消除。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8743瀏覽量

148037 -

數據轉換器

+關注

關注

1文章

366瀏覽量

28113

發布評論請先 登錄

相關推薦

交錯式ADC的基礎知識

基于時間交錯技術實現10位/400 MSPS ADC的設計

一文了解交錯式ADC(數據轉換器)

詳解時間交錯技術

交錯ADC之間的增益不匹配

拓展一些關于交錯ADC的觀點

天文學家揭開快速射電暴的謎團

一文詳細了解ADC時間交錯技術

交錯式ADC:基礎知識

交錯ADC:揭開謎團

交錯ADC:揭開謎團

評論