通常情況下,一旦創建好Vivado工程,添加了相應的RTL文件,Vivado會自動找到設計的頂層文件,正確地顯示設計層次。在這個過程中,Vivado會自動分析文件的編譯順序。那么是否可以手動調整文件的編譯順序呢?答案是肯定的。

這里我們以調整仿真文件編譯順序為例進行說明。

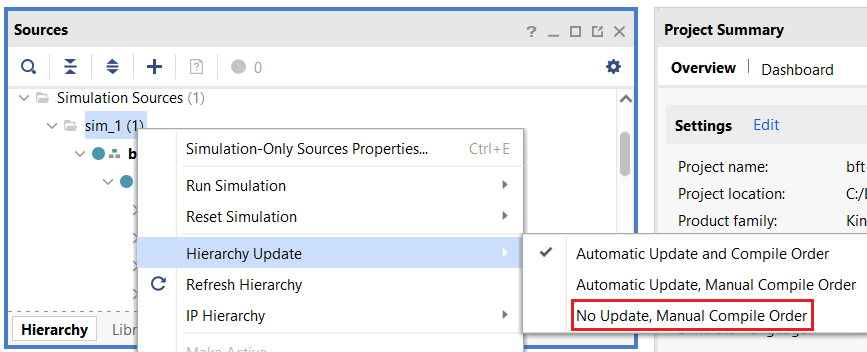

第一步:在Sources窗口中,選擇sim_1文件夾,點鼠標右鍵,在彈出窗口中依次按如下方式選擇。

No Update, Manual Compile Order。

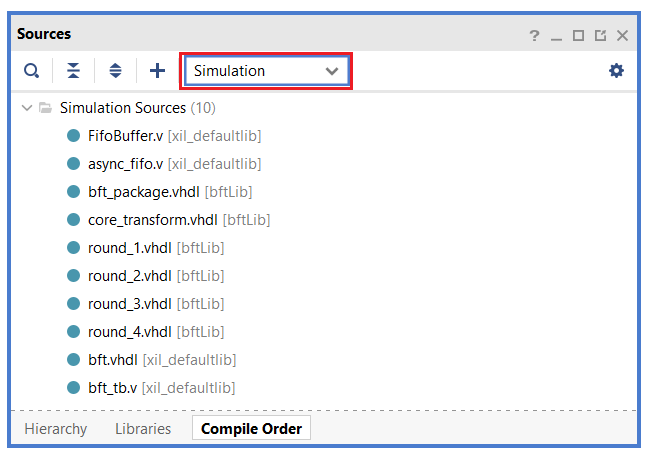

第二步:切換到Compile Order菜單下,并將下圖紅色方框中的內容切換為Simulation。

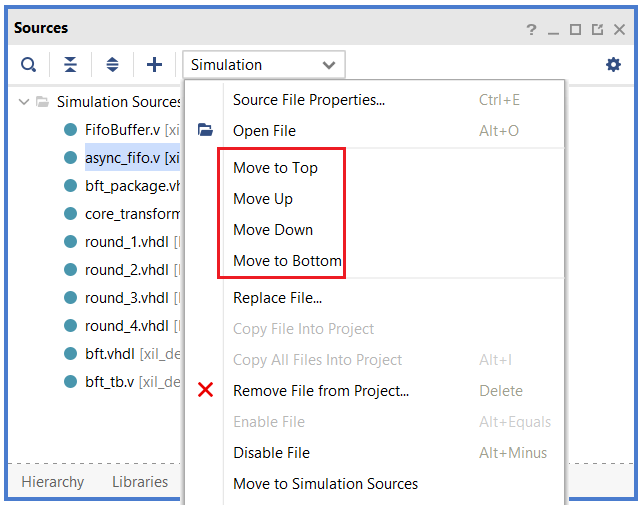

第三步:選中需要調整的文件,點擊鼠標右鍵,在彈出窗口中根據需要選擇相應的紅色方框內的選項。位于最頂層的,將是第一個被編譯的。至此,編譯順序調整完畢。

實際上,Vivado還提供了命令report_compile_order用于查看編譯順序。通過選項-used_in(該選項有3個可選值:synthesis、simulation和implementation)可查看綜合、仿真或布局布線階段的文件編譯順序,通過選項-constraints可查看約束文件的編譯順序。

審核編輯:湯梓紅

-

文件

+關注

關注

1文章

570瀏覽量

24820 -

RTL

+關注

關注

1文章

385瀏覽量

59947 -

編譯

+關注

關注

0文章

661瀏覽量

33040 -

Vivado

+關注

關注

19文章

815瀏覽量

66883

原文標題:Vivado里如何手動調整編譯順序

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

怎么改變模擬編譯順序?

使用scons編譯時,需要怎么做才能輸出gcc的完整編譯信息呢?

使用scons編譯時,我需要怎么做才能輸出gcc的完整編譯信息呢?

Vivado中的Incremental Compile增量編譯技術詳解

Vivado Design Suite 2015.3新增量編譯功能介紹

講述增量編譯方法,提高Vivado編譯效率

賽靈思軟件通過調整編譯參數以及運行并行編譯來優化FPGA時序性能

Vivado中XDC文件的約束順序

在Artix 7 FPGA上使用Vivado的組合邏輯與順序邏輯

Vivado編譯常見錯誤與關鍵警告梳理與解析

淺談Vivado編譯時間

每次Vivado編譯的結果都一樣嗎

Vivado里如何手動調整編譯順序

Vivado里如何手動調整編譯順序

評論