在為高速ADC設(shè)計時鐘網(wǎng)絡(luò)時,抖動是最關(guān)鍵的參數(shù)之一。時鐘抖動量將設(shè)置給定輸入頻率下可以達到的最大SNR。大多數(shù)現(xiàn)代高速ADC都有大約80fs的抖動,ADC的編碼時鐘應(yīng)該在這個范圍內(nèi)。它當然應(yīng)該小于1ps,以實現(xiàn)ADC的最大性能。

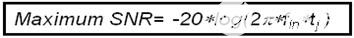

SNR和抖動之間的關(guān)系由以下公式給出:

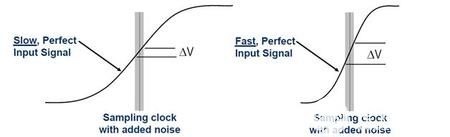

其中fin是輸入信號的頻率,tj是時鐘的抖動。該公式表明,對于高頻輸入信號和固定量的抖動,最大SNR將降低。這是因為在給定的抖動量下,更快的壓擺信號將具有更多的電壓誤差:

圖1.ADC 噪聲與時鐘抖動的關(guān)系

對于頻率成分相對較低的輸入信號,例如在1MHz以下,時鐘抖動變得不那么重要,但是當輸入信號的頻率為幾百兆赫茲時,時鐘上的抖動將成為誤差的主要來源,并且將成為SNR的限制因素。

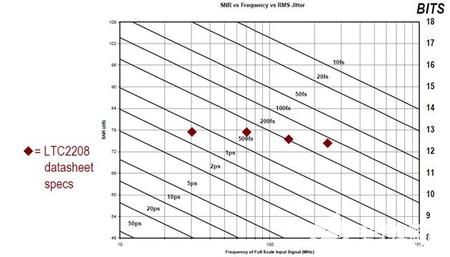

下面是一個簡單的圖表,顯示了SNR如何隨著輸入頻率和時鐘抖動而降低:

圖2.LTC2208 SNR 與頻率 vs. 有效值抖動的關(guān)系

只需在X軸上找到您使用的輸入頻率,在Y軸上找到所需的SNR,您就可以準確地看到時鐘上需要多小的抖動才能達到所需的SNR。為了將時鐘的抖動與ADC的抖動相結(jié)合,您需要用功率將這兩個項相加。

例如,如果你有一個100MHz的輸入信號,并且你想要78dB的SNR,你將需要一個抖動小于200fs的時鐘源。典型的FPGA將具有高達50ps的加性抖動,不應(yīng)使用ADC時鐘。通常,VCXO和低抖動PLL是最佳的ADC時鐘源。

需要注意的是,這些方程源自標準采樣理論,適用于任何制造商的所有ADC。

在設(shè)計具有高速ADC的系統(tǒng)時,考慮時鐘抖動非常重要。它會嚴重限制您在系統(tǒng)中可以實現(xiàn)的SNR,并且可能會在系統(tǒng)設(shè)計中停止顯示。保持盡可能低的時鐘抖動與前端電路的設(shè)計同樣重要。它不應(yīng)該是事后的想法,而應(yīng)該在設(shè)計的第一階段考慮。

審核編輯:郭婷

-

adc

+關(guān)注

關(guān)注

99文章

6533瀏覽量

545752 -

SNR

+關(guān)注

關(guān)注

3文章

196瀏覽量

24521

發(fā)布評論請先 登錄

相關(guān)推薦

TIE抖動和相噪抖動之間的關(guān)系是什么?

時鐘抖動(CLK)和相位噪聲之間的轉(zhuǎn)換

基于DDS的時鐘抖動性能與DAC重構(gòu)濾波器性能的關(guān)系

時鐘抖動時域分析

振蕩器相位噪聲到時間抖動的轉(zhuǎn)換

如何去正確理解采樣時鐘抖動(Jitter)對ADC信噪比SNR的影響

超低抖動時鐘發(fā)生器和分配器最大限度地提高數(shù)據(jù)轉(zhuǎn)換器的信噪比

最大信噪比與時鐘抖動的關(guān)系

最大信噪比與時鐘抖動的關(guān)系

評論