JESD204A/JESD204B串行接口行業標準旨在解決以高效和節省成本的方式將最新的寬帶數據轉換器與其他系統IC互連的問題。其動機是標準化接口,通過使用可擴展的高速串行接口,減少數據轉換器與其他設備(如現場可編程門陣列(FGPA)和片上系統(SoC))設備)之間的數字輸入/輸出數量。

趨勢表明,新應用以及現有應用的進步正在推動對采樣頻率和數據分辨率越來越高的寬帶數據轉換器的需求。與這些寬帶轉換器之間傳輸數據會帶來重大的設計問題,因為現有I/O技術的帶寬限制迫使轉換器產品需要更高的引腳數。因此,系統的PCB設計在互連密度方面變得越來越復雜。挑戰在于路由大量高速數字信號,同時管理電噪聲。提供具有GSPS采樣頻率的寬帶數據轉換器的能力,使用更少的互連,簡化了PCB布局挑戰,并允許在不影響整體系統性能的情況下實現更小的外形尺寸。

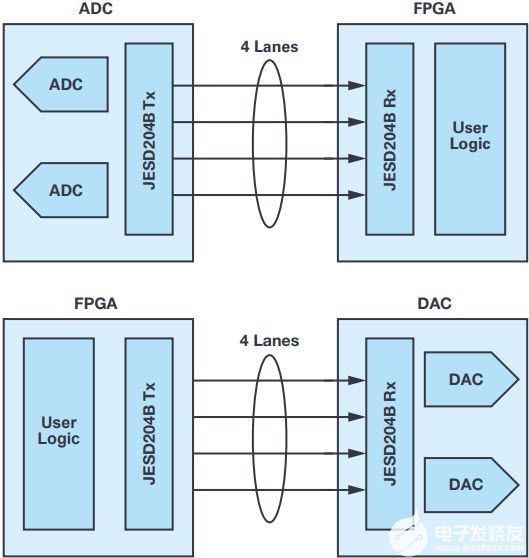

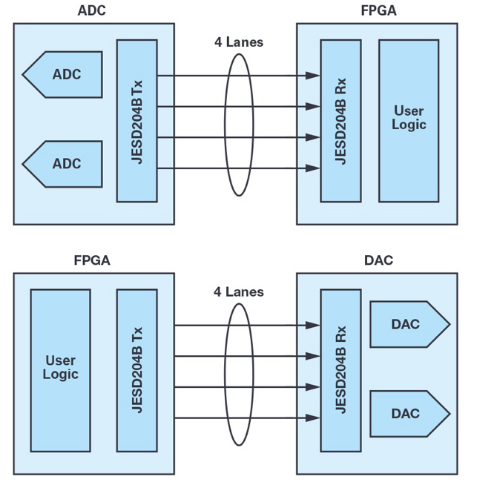

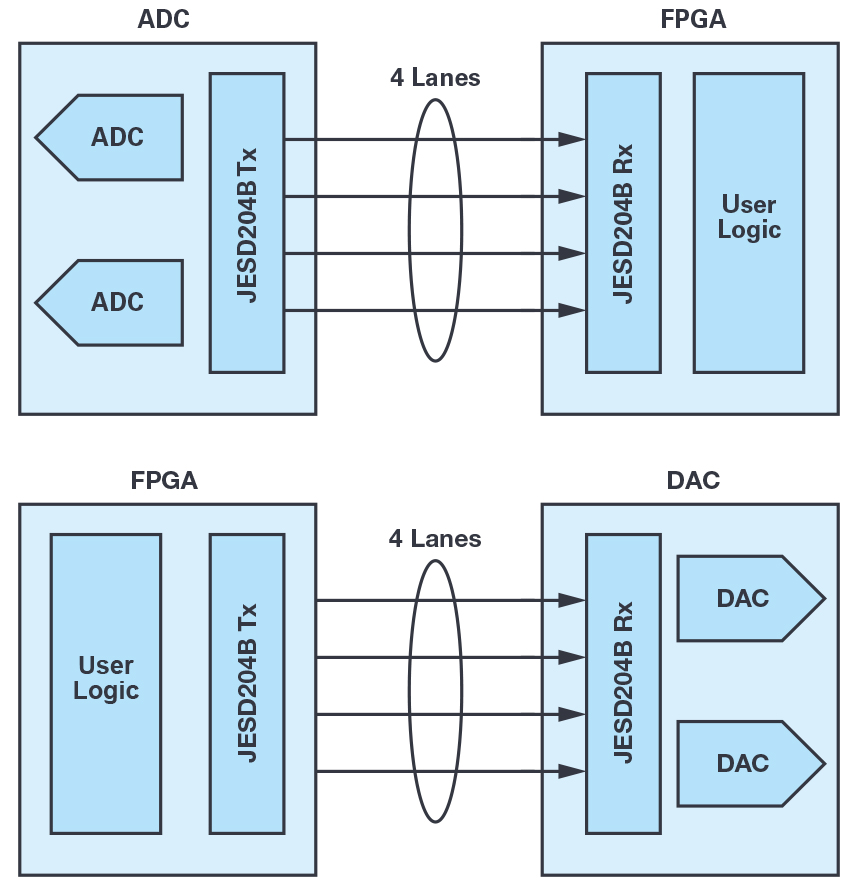

市場力量繼續要求在給定系統中提供更多特性、功能和性能,從而推動了對更高數據處理能力的需求。高速模數轉換器和數模轉換器-FPGA接口已成為一些系統OEM滿足其下一代數據密集型需求的限制因素。JESD204B串行接口規范專門用于通過尋址這一關鍵數據鏈路來幫助解決此問題。圖1顯示了使用JESD204A/JESD204B的典型高速轉換器-FPGA互連配置。

圖1.采用 JESD204A/JESD204B 接口的典型高速轉換器至 FGPA 互連配置(來源:Xilinx)。?

推動該規范部署的一些關鍵終端系統應用,以及串行低壓差分信號(LVDS)和JESD204B之間的對比,是本文其余部分的主題。

推動對JESD204B需求的應用

無線基礎設施收發器

當今無線基礎設施收發器中使用的基于 OFDM 的技術(如 LTE)使用在 FPGA 或 SoC 設備上實現的 DSP 模塊驅動天線陣列元件,為每個用戶的手機生成波束。每個陣列元件都需要在發送或接收模式下每秒在FPGA和數據轉換器之間移動數百兆字節的數據。

軟件定義無線電

當今的軟件定義無線電利用先進的調制方案(可動態重新配置)和快速增加的信道帶寬,以提供前所未有的無線數據速率。天線路徑中的高效、低功耗、低引腳數FPGA至數據轉換器接口對其性能起著關鍵作用。軟件定義無線電架構是多載波、多模無線網絡收發器基礎設施不可或缺的一部分,支持 GSM、EDGE、W-CDMA、LTE、CDMA2000、WiMAX 和 TD-SCDMA。

醫療成像系統

包括超聲、計算斷層掃描 (CT) 掃描儀、磁共振成像 (MRI) 在內的醫學成像系統可生成許多數據通道,這些數據通道通過數據轉換器流向 FPGA 或 DSP。 不斷增加的 I/O 數量要求使用中介層來匹配 FPGA 和轉換器引腳排列,從而增加了 PCB 的復雜性,從而推動了組件數量。這為客戶的系統增加了額外的成本和復雜性,而更高效的JESD204B接口可以解決這一問題。

雷達和安全通信

當今先進的雷達接收機上日益復雜的脈沖結構正在將信號帶寬推向1 GHz或更高。最新一代有源電子縮放陣列(AESA)雷達系統可能有數千個元件。需要基于SERDES的高帶寬串行接口將陣列元件數據轉換器連接到處理傳入和生成傳出數據流的FPGA或DSP。

串行LVDS與JESD204B的比較

在LVDS系列和JESD204B接口之間進行選擇

為了在使用LVDS或各種版本的JESD204串行接口規格的轉換器產品之間進行最佳選擇,比較每個接口的特性和功能是有用的。表 1 中提供了簡短的表格比較。在SERDES級別,LVDS和JESD204之間的顯著區別是通道數據速率,與LVDS相比,JESD204支持每通道串行鏈路速度的三倍以上。在比較多器件同步、確定性延遲和諧波時鐘等高級特性時,JESD204B是唯一提供此功能的接口。需要寬帶寬多通道轉換器且對所有通道和通道的確定性延遲敏感的系統將無法有效使用 LVDS 或并行 CMOS。

| 功能 | 串行低密度驅動器 | JESD204 | JESD204A | JESD204B |

| 規范發布 | 2001 | 2006 | 2008 | 2011 |

| 最大通道速率 (Gbps) | 1.0 | 3.125 | 3.125 | 12.5 |

| 多車道 | 不 | 不 | 是的 | 是的 |

| 車道同步 | 不 | 不 | 是的 | 是的 |

| 多設備同步 | 不 | 是的 | 是的 | 是的 |

| 確定性延遲 | 不 | 不 | 不 | 是的 |

| 諧波時鐘 | 不 | 不 | 不 | 是的 |

LVDS 概述

LVDS是將數據轉換器與FPGA或DSP接口的傳統方法,LVDS于1994年推出,旨在提供比現有RS-422和RS-485差分傳輸標準更高的帶寬和更低的功耗。隨著1995年TIA/EIA-644的發布,LVDS實現了標準化。LVDS的使用在1990年代后期有所增加,隨著2001年TIA/EIA-644-A的發布,該標準進行了修訂。

LVDS使用具有低電壓擺幅的差分信號進行高速數據傳輸。發射器通常驅動±3.5 mA電流,極性與邏輯電平相匹配,通過100 Ω電阻發送,在接收器處產生±350 mV電壓擺幅。始終導通的電流沿不同方向布線,以產生邏輯 1 和 0。LVDS的始終開啟特性有助于消除在單端技術中晶體管打開和關閉時有時會發生的同步開關噪聲尖峰和潛在電磁干擾。LVDS的差分特性也提供了對共模噪聲源的相當大的抗擾度。TIA/EIA-644-A 標準建議最大數據速率為 655 Mbps,盡管它預測理想傳輸介質的速度可能超過 1.9 Gbps。

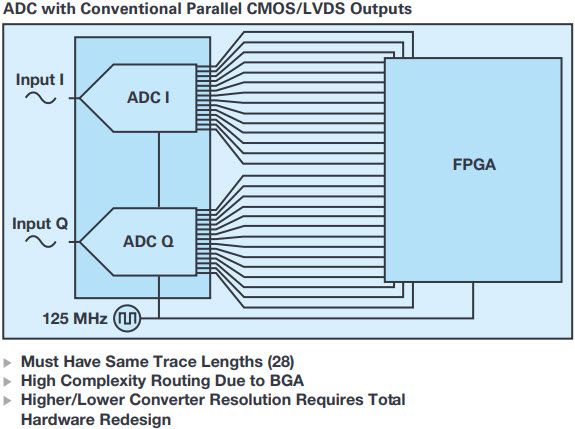

FPGA或DSP與數據轉換器之間數據通道數量和速度的大幅增加,特別是在前面描述的應用中,給LVDS接口帶來了一些問題(見圖2)。在現實世界中,差分LVDS線的帶寬限制在約1.0 Gbps。在許多當前應用中,這就產生了對大量高帶寬PCB互連的需求,每個互連都是潛在的故障點。大量的走線也增加了PCB的復雜性或整體外形尺寸,從而提高了設計和制造成本。在某些應用中,數據轉換器接口成為在帶寬密集型應用中實現所需系統性能的限制因素。

圖2.使用并行CMOS或LVDS的系統設計和互連方面的挑戰。

JESD204B 概述

JESD204數據轉換器串行接口標準由JEDEC固態技術協會JC-16接口技術委員會創建,旨在為數據轉換器提供更高速的串行接口,以增加帶寬并減少高速數據轉換器與其他設備之間的數字輸入和輸出數量。該標準基于IBM開發的8b/10b編碼技術,該技術消除了對幀時鐘和數據時鐘的需求,能夠以更高的速度實現單線對通信。

2006年,JEDEC發布了針對單個3.125 Gbps數據通道的JESD204規范。JESD204接口是自同步的,因此無需校準PCB走線的長度以避免時鐘偏差。JESD204利用許多FPGA上提供的SERDES端口來釋放通用I/O。

JESD204A于2008年發布,增加了對多個時間對齊數據通道和通道同步的支持。這種增強功能使得使用更高帶寬的數據轉換器和多個同步數據轉換器通道成為可能,對于蜂窩基站中使用的無線基礎設施收發器尤其重要。JESD204A還提供多器件同步支持,這對于使用大量ADC的器件(如醫療成像系統)非常有用。

JESD204B是該規范的第三個修訂版,將最大通道速率提高到12.5 Gbps。 JESD204B還增加了確定性延遲,可在接收器和發射器之間傳達同步狀態。JESD204B中也引入了諧波時鐘,使得從具有確定性相位的低速輸入時鐘獲得高速數據轉換器時鐘成為可能。

結論

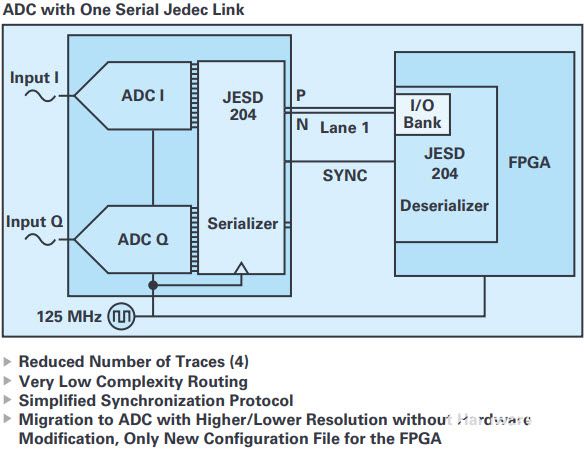

JESD204B工業串行接口標準減少了高速數據轉換器與FPGA和其他器件之間的數字輸入和輸出數量。更少的互連簡化了布局,并有可能實現更小的外形尺寸(參見圖 3)。這些優勢對于各種高速數據轉換器應用非常重要,例如無線基礎設施收發器、軟件定義無線電、醫療成像系統以及雷達和安全通信。ADI公司是JESD204標準委員會的原始參與成員,我們同時開發了兼容的數據轉換器技術和工具以及全面的產品路線圖。通過為客戶提供將我們的尖端數據轉換器技術與JESD204A/JESD204B接口相結合的產品,我們希望使客戶能夠解決他們的系統設計問題,同時利用這一重大的接口突破。

圖3.JESD204具有高速串行I/O功能,解決了系統PCB復雜性挑戰。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8743瀏覽量

148035 -

soc

+關注

關注

38文章

4204瀏覽量

219091 -

lvds

+關注

關注

2文章

1045瀏覽量

66009

發布評論請先 登錄

相關推薦

寬帶數據轉換器應用的JESD204B與串行LVDS接口考量

FPGA高速數據采集設計之JESD204B接口應用場景

如何讓JESD204B在FPGA上工作?FPGA對于JESD204B需要多少速度?

JESD204B協議有什么特點?

JESD204B中的確定延遲到底是什么? 它是否就是轉換器的總延遲?

寬帶數據轉換器應用的JESD204B與串行LVDS接口考量

針對高速數據轉換器的最新高速JESD204B標準帶來了驗證挑戰

JESD204B與串行LVDS接口在寬帶數據轉換器應用中的考慮因素

JESD204B與串行LVDS接口在寬帶數據轉換器應用中的考慮因素

評論