鎖相環(PLL)電路是一種反饋系統,它結合了壓控振蕩器(VCO)和鑒相器,使振蕩器信號以正確的頻率和相位跟蹤施加的頻率或相位調制信號。當需要從固定的低頻信號產生穩定、更高的輸出頻率或需要快速頻率變化時,可以使用PLL。典型用例是高頻、電信和測量技術,用于實現濾波器、調制和解調以及頻率合成。

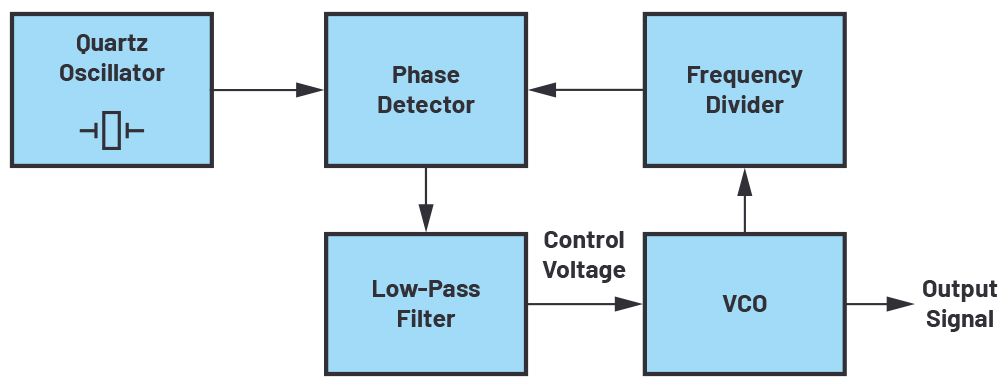

圖1所示為基于PLL的頻率合成器的框圖。VCO 生成輸出信號。PLL將其保持在設定點頻率,并鎖定至參考頻率。參考頻率通常由非常精確的石英振蕩器提供。在鑒相器前面的鎖相環電路的反饋路徑中設置了一個分頻器,以通過可調系數降低VCO頻率。

圖1.鎖相環框圖。

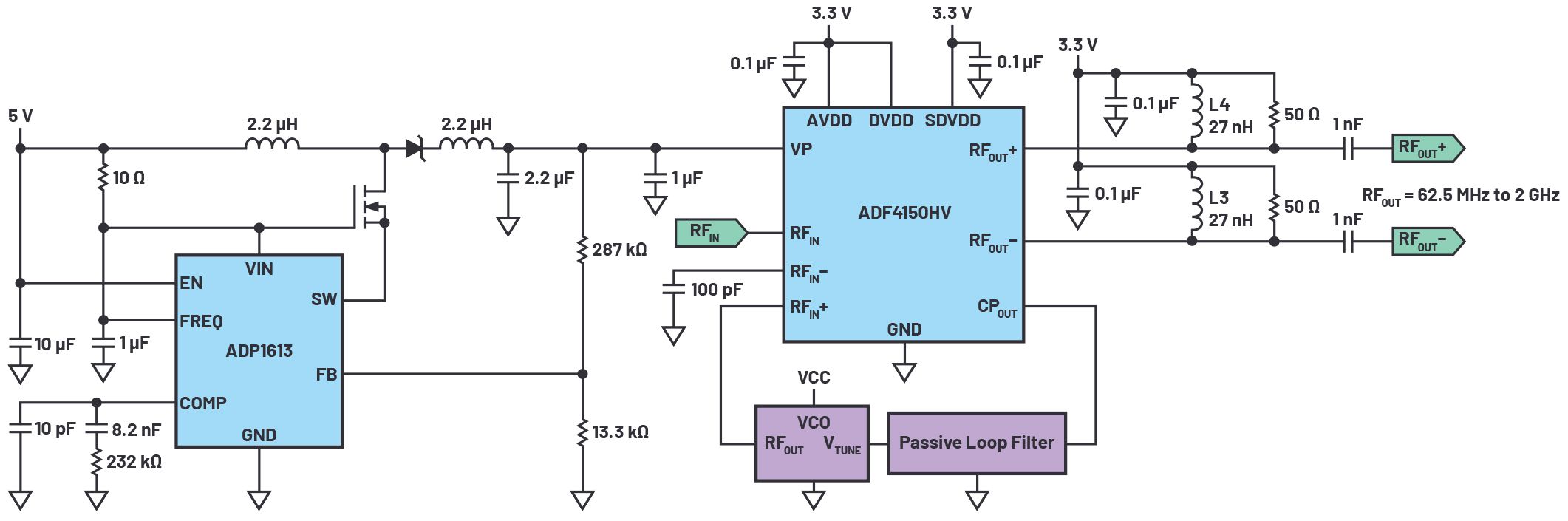

VCO包含一個可調調諧元件,例如變容二極管,其電容隨輸入電壓而變化。因此,PLL電路是VCO的一種反饋控制系統。VCO所需的輸入或控制電壓通常高于PLL電路可用的電源電壓。電源電壓通常為3.3 V或5 V,而VCO可能需要超過20 V的電壓,具體取決于所需頻率。為了產生更寬的頻率范圍,可以使用具有更寬調諧范圍的VCO。支持千兆赫茲范圍內VCO的簡化電路示例如圖2所示。

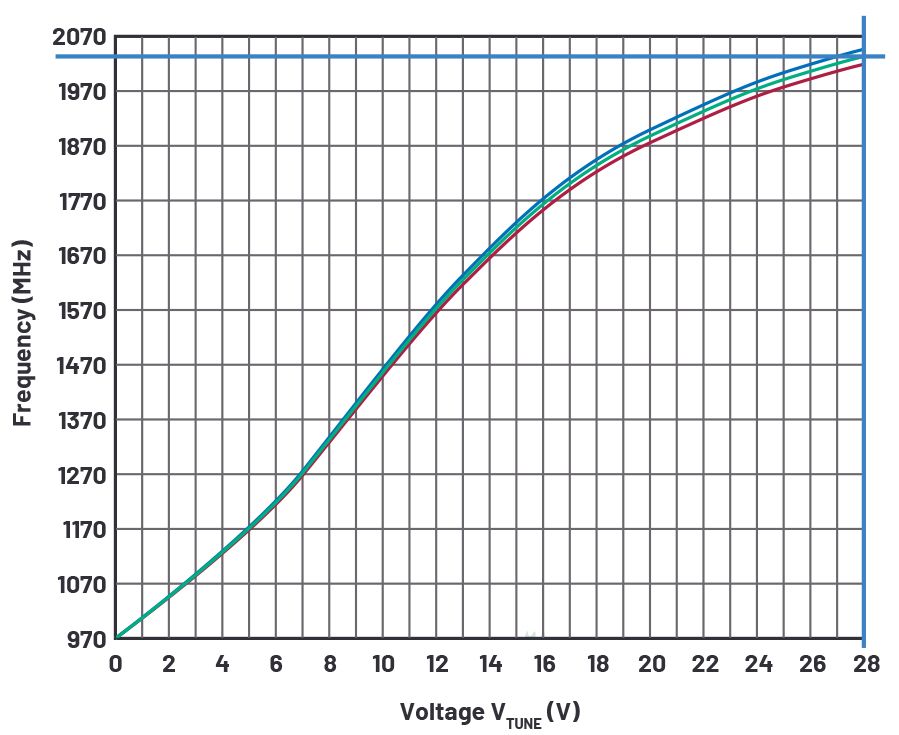

作為VCO,可以使用Synergy微波公司的DCYS100200-12。它允許在 28 V (V調整),如圖 3 中的圖形所示。

圖3.DCYS100200-12 的控制電壓與頻率的關系。

產生高控制電壓有幾種可能性。一種是使用有源環路濾波器,它主要由一個高速放大器和一個低通濾波器組成,該濾波器對鑒相器(CP外) 變成干凈的直流電壓。作為替代方案,可以使用集成電荷泵的PLL頻率合成器,例如ADI公司(ADI)的ADF4150HV,它不需要額外的有源環路濾波器。雖然這兩種解決方案都需要高壓電源,但ADF4150HV可以減少元件數量。還可以避免有源濾波放大器引起的失真和相位噪聲。此外,ADF4150HV還允許實現小數N分頻或整數N分頻鎖相環頻率合成器。因此,VCO頻率可以分頻1、2、4、8或16,以便輸出頻率可以低至最低31.25 MHz。

ADF4150HV集成電荷泵所需的高電壓可通過DC-DC升壓轉換器ADP1613產生,而不會影響PLL性能。ADP1613是一款集成功率晶體管的高效開關穩壓器,可輕松實現高達20 V的輸出電壓。 通過使用額外的外部元件,特別是通過外部功率晶體管,也可以獲得更高的輸出電壓。ADP1613的開關頻率可在650 kHz至1.3 MHz范圍內調節。這導致更好的瞬態響應和簡單的噪聲過濾。通常,建議選擇大于1 MHz的開關頻率,以便PLL環路濾波器降低開關噪聲。

采用ADF4150HV的鎖相環頻率合成器電路采用集成RF分頻器,提供超寬帶PLL功能。它可實現 62.5 MHz 至 2 GHz 的頻率覆蓋范圍。使用相同的PLL硬件設計,可以為系統中的多種不同硬件平臺生成不同的頻率。但是,如果各種VCO類型需要設計,則在設計中加入相應的環路濾波器是有意義的。通過這種方式,可以確保鎖相環可靠地運行。對于相對較寬的輸出頻率調節范圍以及相關的較高輸出功率,ADF4150HV的每個RF輸出也需要一個小濾波器結構。27 nH電感與50 Ω電阻并聯,可為高達3 GHz的頻率提供良好的調節。電阻器提供定義的輸出阻抗。較低的電感將導致頻帶擴展到較低的范圍。

如今,在一個外殼中也可以提供用于更大頻率范圍(即PLL、濾波器和VCO)的集成解決方案,但由于不同組件之間的距離很近,這可能會導致不希望的耦合。分立式設計和由此產生的物理分離將這種風險降至最低。

PLL頻率合成器仿真工具ADIsimPLL?還為HF功能模塊和建模HF信號鏈的開發提供了有用的支持。它允許設計人員相對輕松地仿真可能影響PLL性能的所有重要非線性效應;例如,頻率合成過程中不需要的雜散(雜散頻率)。

審核編輯:郭婷

-

濾波器

+關注

關注

161文章

7860瀏覽量

178931 -

振蕩器

+關注

關注

28文章

3847瀏覽量

139361 -

pll

+關注

關注

6文章

781瀏覽量

135332

發布評論請先 登錄

相關推薦

ADI:驅動高壓鎖相環頻率合成器電路的VCO

一種基于ADF4106的鎖相環頻率合成器應用實例介紹

基于ADF4106的鎖相環頻率合成器

驅動高壓鎖相環頻率合成器電路的VCO

驅動高壓鎖相環頻率合成器電路的VCO

評論