最近在項目中以SpinalHDL為主體做系統集成,其中遇到了不少模塊命名與管理的坑,借此機會,再來聊一聊混合編程中的模塊件命名與管理的事情。

問題是什么

不可否認,在當前的整體大環境下,Verilog/SystemVerilog仍然是主流,而SpinalHDL其本質上更像是一個生成Verilog的腳本工具。在團隊合作中,最終拿去生成跑綜合及布局布線生網表的仍然是Verilog代碼。團隊合作時當同時存在SpianlHDL代碼和Verilog代碼時不可避免的存在命名沖突的問題:

盡管SpinalHDL支持參數化設計,但其參數化是基于Scala層面上的,當我們調用SpinalHDL同一個IP以不同的參數例化時往往會為每次例化均生成一個Verilog模塊代碼。而當合作中存在多人調用組件生成RTL代碼時最后往往會有模塊命名撞車的問題。

在《被忽略的兩個Tips》及《換個名字混江湖》中對于模塊的命名均有提到一些方法,這里就真實的使用場景來看看這個問題。

setDefinitionName

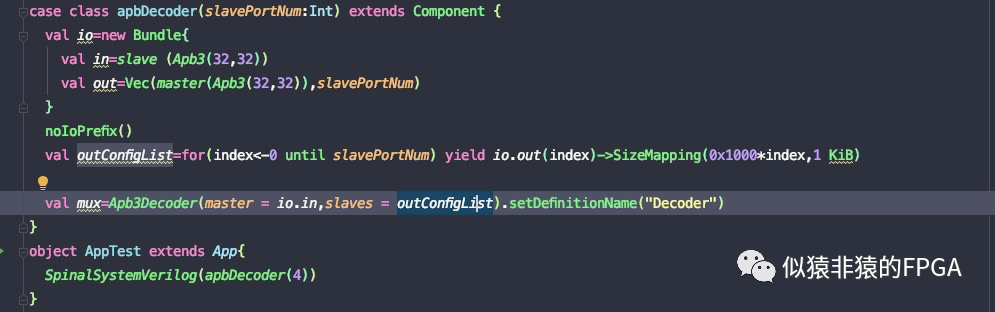

在《換個名字混江湖》中對setDefinitionName的使用有較為詳細的介紹,setDefinitionName可以手動的修改最終生成的Verilog代碼對應的模塊名,像下面的這段代碼:

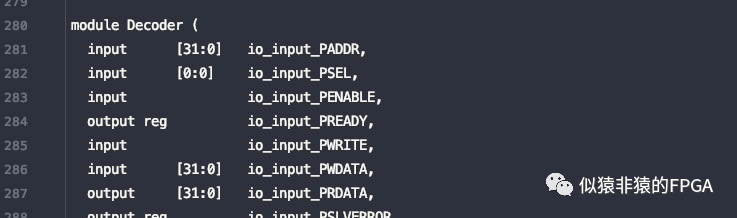

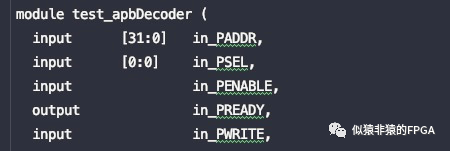

這里在例化Apb3Decoder這個SpinalHDL中的IP組件時,通過setDefinitionName來設置生成RTL代碼時該模塊名重新命名為Deocer。最終生成的代碼便是下面這樣:

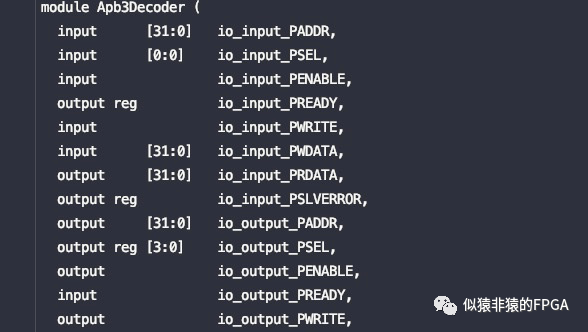

倘若不添加setDefinitionName指定那么生成的RTL代碼則保持原來的名字:

通過setDefinitionName可以手動的為我們的模塊指定特定的名稱,但如此做帶來的問題是我們需要要求每個人在例化每個模塊時均指定名稱。稍有不慎漏掉一個那么在最后合并整體工程時便會有重復命名的問題。更值得把握的是當我們調用的其他lib有多層嵌套例化時那么這種方式便顯得更為復雜了。

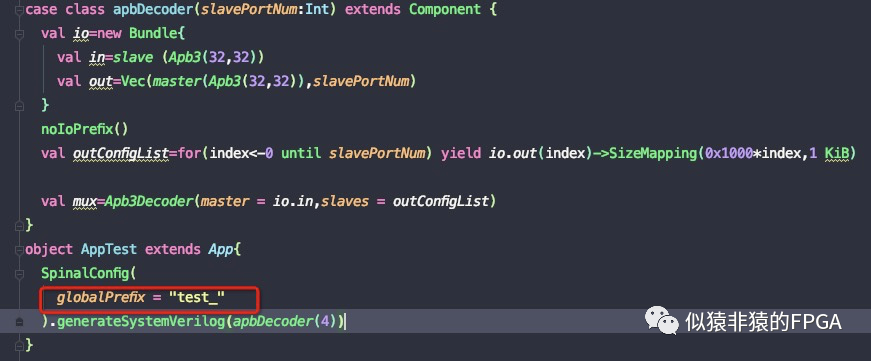

globalPrefix

通過globalPrefix的方式可以使得在生成RTL代碼時為每個模塊添加一個特定的前綴。像下面的代碼:

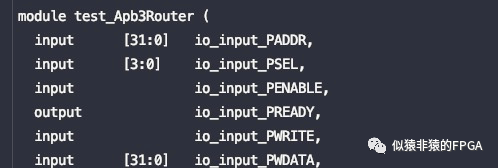

指定每個模塊的命名前面均添加“test_”,可以看到最終生成的RTL代碼的每個模塊前均添加有"test_"前綴:

多人合作時根據每個人負責的功能模塊分別添加響應的模塊命名前綴似乎是一個很的方式,然而是否通用? 看下面的例子:

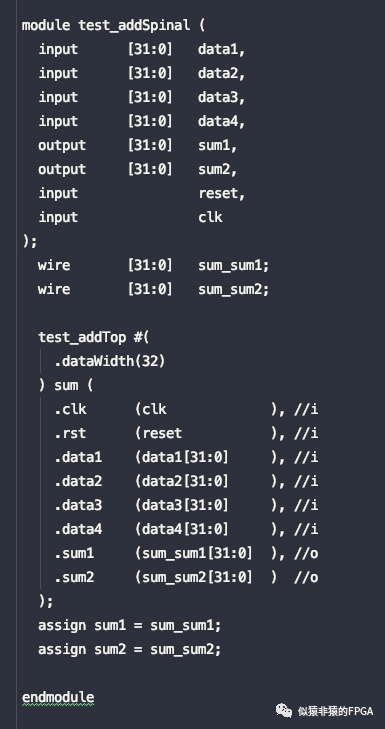

這里我們在SpinalHDL中調用了封裝好的RTL代碼addTop,如果我們在例化時指定globalPrefix為“test_”,那么看看會是什么樣子:

問題來了,我例化的BlackBox代碼模塊名稱為addTop,而這里例化的時候卻例化了test_addTop——一個壓根沒有的模塊。

也就意味著當代碼里存在Verilog和SpinalHDL代碼混合使用時那么這種globalPrefix方式便顯得太“一刀切”了。

怎么做

解決不了上面的問題那么無論SpinalHDL再怎么優秀那終究是雞肋~

怎么做?合二為一唄!

看下面的代碼:

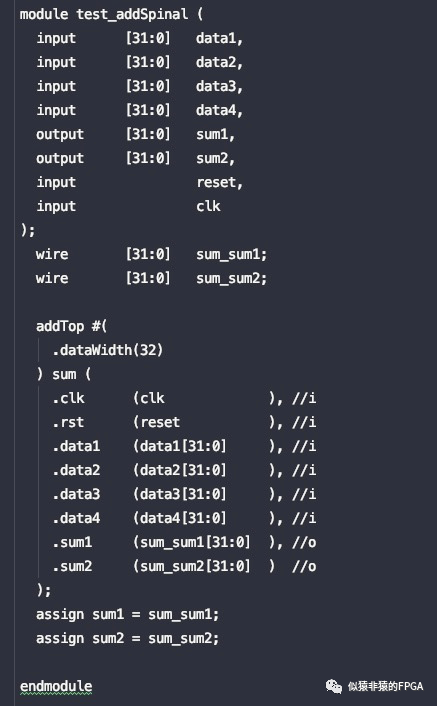

而最終生成的RTL代碼為:

是不是看起來解決了我們的問題? setDefinitionName的優先級是高于globalPrefix的,我們在例化BlackBox時通過setDefinitionName指定模塊的名字來避免在添加globalPrefix時帶來的問題便可。

小小建議

在當前的環境下,團隊合作時若你采用SpinalHDL作為編程語言不妨采用下面的方式來進行混合編程下的模塊命名與管理:

1、若只負責單個模塊的開發,那么在生成rtl代碼時根據模塊的功能通過globalPrefix添加適當的前綴。

2、若在SpinalHDL中例化封裝Verilog代碼時,在例化時通過setDefinitionName指定例化時的模塊名稱確保生成RTL代碼時不會被修改掉。

審核編輯:湯梓紅

-

模塊

+關注

關注

7文章

2733瀏覽量

47747 -

Verilog

+關注

關注

28文章

1351瀏覽量

110391 -

混合編程

+關注

關注

0文章

26瀏覽量

8274

原文標題:混合編程中的模塊命名與管理

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

混合編程中的模塊命名與管理

混合編程中的模塊命名與管理

評論