敏捷開發理念在芯片開發中的應用

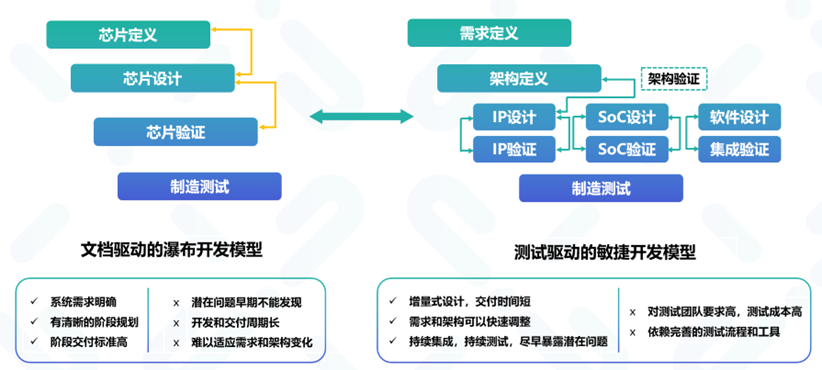

1970年溫斯頓·羅伊斯(Winston Royce)提出了著名的開發流程“瀑布模型”。瀑布模型是將產品開發的各個周期按固定順序而連接,形如瀑布流水,最終得到產品。直到80年代早期,它一直是被廣泛采用的軟件開發模型,在同時期的芯片開發項目中,也基本是采用瀑布模型。瀑布模型的優點是階段劃分明確,有明確的文檔輸入輸出,但這種流程交付周期長,對階段交付標準要求高。90年代開始一直到2000年之后,隨著軟件定制要求快速提高,以“Scrum”和“Agile”命名的敏捷開發方法逐漸發展,敏捷的核心在于更快、更多、更好的迭代,以更早的集成、測試、交付來發現問題和調整產品。但是敏捷開發方法對測試工具和測試團隊提出了更高的要求。

敏捷開發并沒有一個標準的定義,常見的特點有:

拆分和并行開發:大系統拆分成可以并行開發的子模塊,各模塊并行開發、并行測試,并能夠集成為最終系統進行系統級測試;

持續集成、持續部署、持續測試:盡快盡早把各系統模塊進行組合,并以最終面向用戶的形式進行測試,并及時把結果反饋給開發;

自動化流程:把代碼提交、模塊測試、系統集成、系統部署、系統級測試的多個步驟形成自動化流程,自動化后即能用更多的高效與廉價算力來代替人工投入,并增加測試迭代次數,盡快反饋Bug,提高質量;

以測試來驅動開發:因為從代碼到系統的部署和測試流程完全自動且更加及時,因此敏捷流程中往往測試代碼先于功能代碼開發,用測試代碼來驅動功能代碼的開發和測試;

盡可能復用成熟模塊:復用現有的、經測試的可用模塊,是降低開發和測試成本的重要手段。

敏捷驗證解決芯片開發的瓶頸

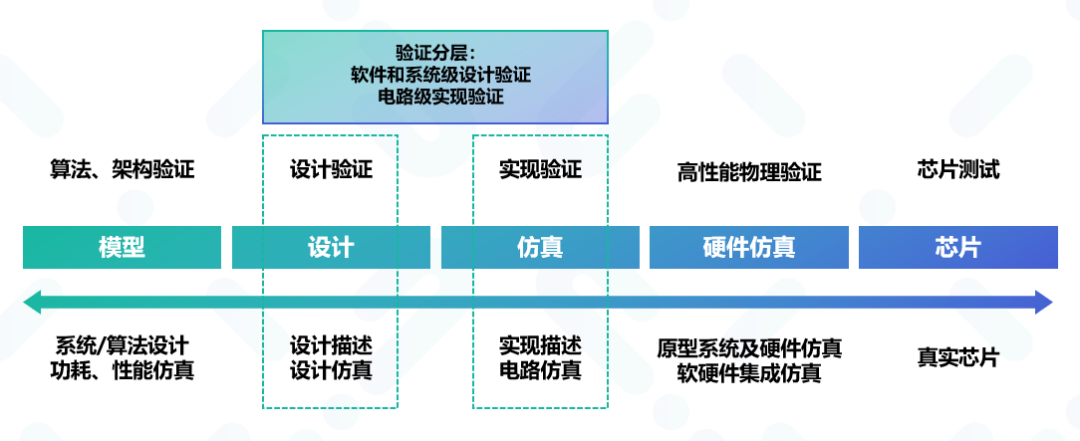

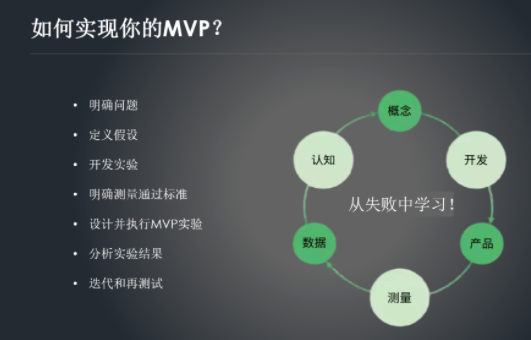

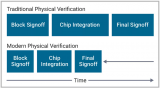

敏捷開發實際上是一種理念而不是標準,與經典的“瀑布流程”之間并沒有明確的分界線。雖然在軟件特別是互聯網軟件領域應用得較多,但敏捷的理念已經逐漸被應用于很多工程開發領域。芯片開發制造作為一種特別復雜的系統工程,同樣也不例外。如果我們回顧上世紀六、七十年代到九十年代的芯片設計和EDA發展歷程,在開發流程上可以總結為如下圖的變化,即芯片開發從早期的“定義-設計-驗證-制造”瀑布模型逐漸細分,芯片越來越復雜,需求和架構的定義逐漸成為不同的階段,而設計階段隨著RTL語言的發展也分化為IP、前端設計、后端設計、軟件設計、系統集成,每個設計步驟都需要有對應的驗證,并誕生了對應的建模、集成、驗證的各類語言和工具。

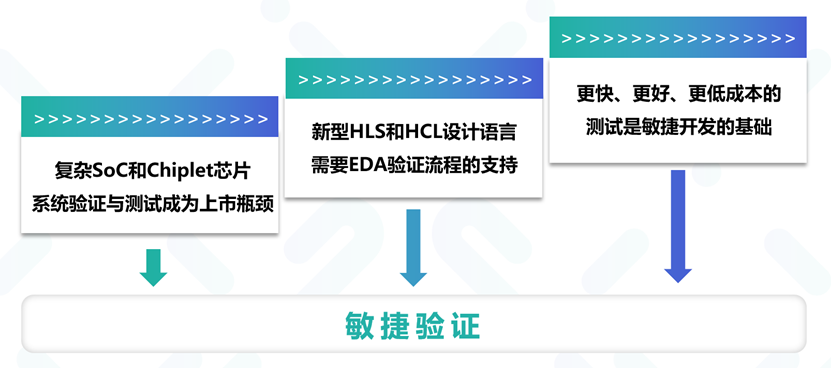

除此之外,近年來基于“敏捷設計”的理念,出現了多種提高RTL語言邏輯表達層次的電路描述語言,比如Bluespec、Chisel、SpinalHDL、nMigen等HDL語言和框架,它們基于Scala或Python等語言,加入RTL級描述和代碼構建功能,主要出發點是簡化從架構定義到硬件邏輯描述的流程,并能從這樣的硬件邏輯描述自動生成RTL級電路實現。同時基于類C語言等高層次語言的HLS綜合方法學,也在過去十幾年逐步發展。這些都在推動芯片開發敏捷化的發展。

目前的HLS或HDL等高層次設計語言,更多集中在從架構定義到邏輯設計、電路實現的敏捷流程,側重于提高芯片設計抽象層級,用可參數化、可復用的高級語言做設計,目的是讓架構和邏輯的修改能快速反映到設計實現中。但是存在的問題是脫離了傳統芯片電路級驗證、調試、修改的流程,驗證環節沒有加速反而一定程度上讓驗證與設計脫節,增加了驗證困難,因此在芯片開發流程中還沒有得到普遍應用。

隨著芯片的規模和復雜度越來越高,對芯片的驗證要求越來越高。如何更有效地完成芯片所有功能的驗證成為最大的挑戰,芯片驗證工作已經占用了整個開發流程的70%時間和資源,成為實際上的瓶頸。在芯片開發周期的所有階段——包括架構、模塊設計、綜合、系統集成、軟件開發和物理設計階段,都會引入錯誤,而且很多錯誤是無法在當前階段完全發現和解決的。這個背景也非常符合敏捷理念所面對的問題:用更快更完善的迭代流程,讓設計和驗證更“敏捷”地進入下一階段,才能更早發現每個模塊在后期階段才能暴露出的潛在問題。

從上文可以看出,沒有自動、智能、快捷的驗證流程和工具,就無法完成復雜大規模芯片的低成本敏捷開發流程,也無法推動EDA工具流程向敏捷開發方向發展。因此,優化和完善芯片敏捷開發流程,首先要解決如何實現設計驗證敏捷化的問題。

芯片敏捷驗證的發展目標

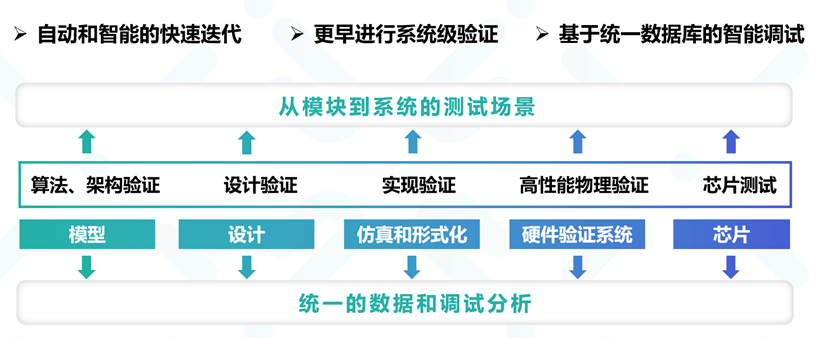

綜合敏捷開發在其它行業的經驗,并結合其在芯片開發流程中的歷史、現狀,我們初步提出敏捷驗證的主要發展目標,以發展出下一代EDA 2.0的核心驗證流程。

特別值得一提的是,這里列出的每一個點目標,都需要EDA算法團隊、EDA工具廠商、芯片設計團隊、計算平臺供應商這整個生態的緊密結合和配合,不僅僅從技術角度,還需要從應用模式角度變革,才能快速推動現有EDA流程的發展。

自動和智能的快速迭代

EDA驗證的本質是基于特定流程的大量計算,而近年來全球算力發展的突飛猛進,讓超大規模計算的成本大幅降低,這給計算替代分析的工程方法學帶來了更多空間,敏捷驗證在迭代流程和計算優化方向的發展目標包括但不限于如下優化點:

支持自動化的快速部署、持續迭代流程

自動化流程是整個敏捷驗證和敏捷開發的核心基礎,目前的模塊和IP級開發,一般基于UVM等測試框架,使用自動化腳本完成仿真流程并收集測試結果和覆蓋率數據,單個工具的流程自動化已經比較完善。但是,面向功能測試或約束隨機的測試用例,還是需要大量的人工分析和編寫。同時多種EDA工具之間的協同,特別是到集成驗證階段,還經常需要大量人工介入來完成集成和實現,因此實際情況往往是各種工具單獨使用,模塊驗證和集成驗證相互隔離。我們需要發展更自動和智能的平臺級EDA工具,實現多工具協同下的測試用例生成、設計編譯、實現、驗證計算、數據收集一直到部分調試分析的自動化,以支持敏捷開發中“快速部署和持續迭代”的工程方法學,縮小從設計到驗證的周期及成本。

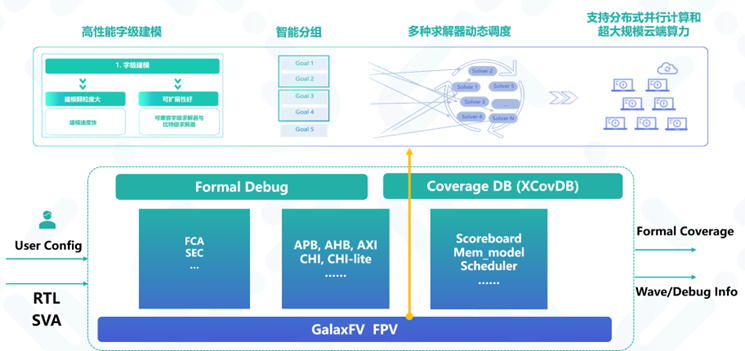

更多使用基于大規模算力的形式化驗證方法

形式化驗證方法能夠從數學建模角度全面地驗證設計是否正確,是對仿真驗證方法的有效補充,也對驗證自動化的發展有利。但過去形式化驗證的應用往往受限于求解空間和計算量。隨著近年來全球算力規模的大發展,以及AI方法在輔助形式化驗證求解方向開始取得進展,將會有效推動形式化驗證得到更廣泛使用。同時,形式化驗證工具也需要從計算性能、核心調度算法、應用場景支持、云計算應用不斷改進,基于新型形式化驗證EDA工具,驗證流程會更加依靠大規模算力而不是人工投入。如芯華章科技的GalaxFV形式化驗證產品,已經在形式化驗證工具的前沿發展上取得了一定進展。

更早引入系統集成驗證到迭代流程中

設計者越來越認識到,芯片設計的后端實現過程以及與軟件的大系統集成,往往會引入新的問題或者暴露設計的深層次問題,而且未來Chiplet級芯片的創新發展,會對EDA系統級驗證提出極高要求。因此,EDA驗證過程,需要基于自動化的EDA工具、各種功能、性能、互聯模型的支持以及多驗證平臺的聯合仿真,在驗證迭代中盡早引入后端的實現驗證和軟硬件系統集成,推動EDA前端仿真、功能驗證、后端實現、后端驗簽等全流程步驟的自動化,讓架構和設計的任何修改都能夠快速反映到驗證系統中,并進行從模塊級到系統級的迭代測試,讓架構和設計的問題盡快暴露在更接近真實環境的系統中,這也包括了系統級性能和功耗的提前驗證。當然,更早實現系統級的驗證迭代不意味著放松模塊級的測試要求。

更敏捷的驗證計算

EDA算法優化 :EDA驗證相關的核心邏輯和求解器的算法優化和異構實現;

EDA計算并行化 :基于多核、多節點、高速聯接的并行計算網絡結構,加速EDA驗證的并行計算;

EDA計算規模化:基于架構靈活、成本更低的大規模彈性云計算資源,在更高層次實現EDA驗證集群的并行化;

EDA計算異構加速:EDA驗證計算傳統上主要依賴主流CPU主機,但隨著異構計算的快速發展,新型CPU、GPU、光計算甚至量子計算平臺,會越來越多地進入傳統EDA計算的領域,以實現更高效、更低成本的大規模計算;

基于大數據的AI機器學習和“傳統計算”的結合:大數據分析和機器學習被不斷應用在前端驗證、后端布局和驗證、制造測試等不同的EDA驗證階段,是一個已經出現并會不斷加速的趨勢;

更早進行系統級驗證

系統層驗證和電路層驗證分離

傳統芯片硬件開發的特點是邏輯設計和電路實現緊密結合,在驗證環節同樣也是如此。但是隨著SoC芯片復雜度提高,芯片驗證的很大一部分工作更偏向于系統功能測試和軟件測試,特別是依賴操作系統和大量中間層軟件環境的系統測試,用傳統的電路級驗證語言很難支持。因此,EDA工具實現系統軟件層功能驗證和實現層電路驗證的分離,讓用戶更多使用傳統軟件層的高級語言來完成系統層驗證,是未來驗證語言和驗證工具的重要目標。

這可以有效降低對驗證工程師的綜合性要求,并減輕驗證中的開發工作量,復用更多現有的軟件生態,并在邏輯無關的底層實現級更多使用形式化驗證、驗證IP復用等方法自動驗證。同時,未來chiplet多芯粒芯片的發展目標,也會逐步降低對電路實現層驗證的需求,而逐漸加大對系統軟件層面功能和性能驗證的比重。

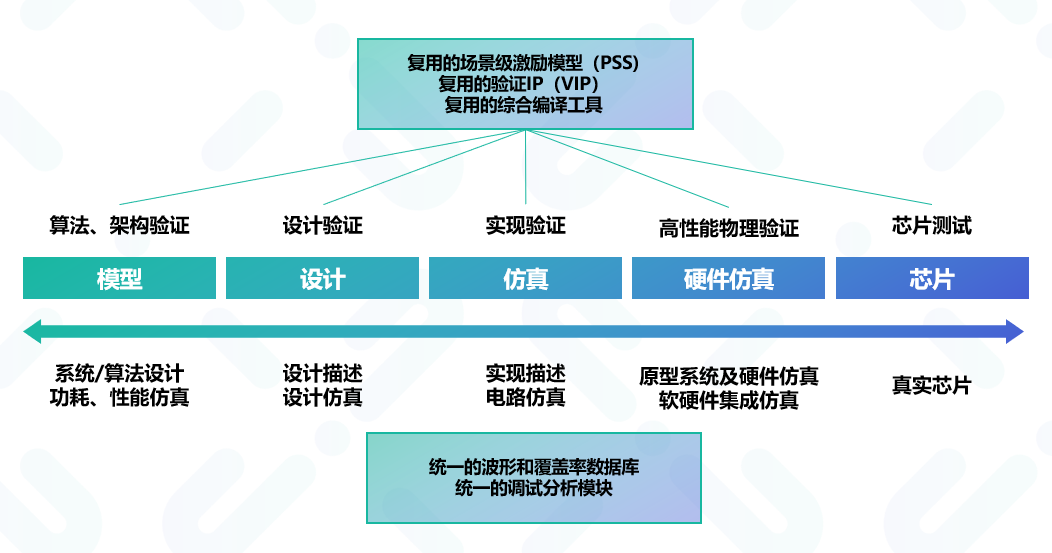

更多的驗證復用

敏捷驗證的另一個重要發展方向是從驗證工具、驗證數據、驗證IP到測試用例的統一和大規模復用。例如基于PSS(Portable Stimulus Standard)標準和工具的復雜場景測試用例,可以覆蓋從ESL級模型到最終芯片實現的多級測試復用。而更統一的設計編譯工具,可以有效減少軟件仿真、硬件仿真、形式化求解等多種工具相互遷移時的重復編譯時間。最終多種驗證工具所產生的互補的驗證結果和數據,應該能集中到統一的中央數據庫中,并通過管理工具進行項目驗證進程的計劃、管理。最終整個驗證流程和多種驗證工具不應該是碎片化的,而應該形成統一的驗證平臺(Verification Platform)。

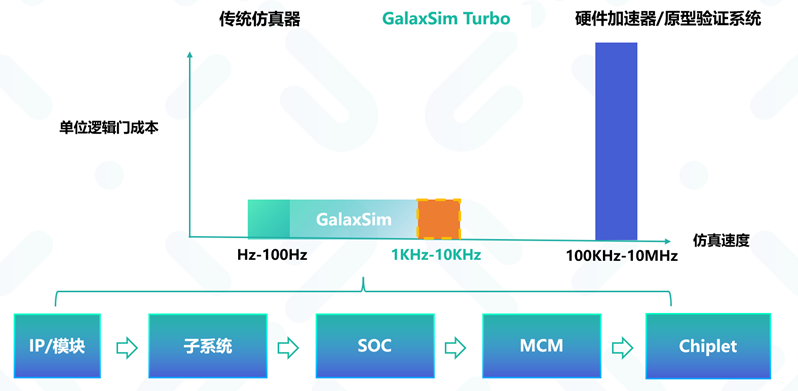

基于軟硬件仿真的系統驗證自動化

仿真是驗證過程中的核心手段。隨著SoC和Chiplet芯片越來越廣泛應用,在驗證過程中盡早啟動系統級驗證、并減少系統級驗證的實現成本,是驗證敏捷化的最重要需求。具體來說,大規模系統級驗證在軟件仿真階段,過去沒有很好的EDA手段,最近芯華章科技推出的GalaxSim仿真Turbo模式,首次填補了系統級軟件仿真的空白,在提前做系統級驗證、降低大規模系統驗證成本方面走出了第一步。

同時,硬件系統平臺仍然是大規模高性能系統仿真的必要手段。過去在硬件系統仿真上,我們遇到的很大困難是產品和人力成本的高投入,從設計到系統驗證這個流程需要在多種軟硬件平臺上一次又一次地由工程師來實現。芯華章科技的硬件驗證系統產品,致力于統一軟硬件平臺,降低客戶在EDA成本和人力成本上的大量投入。

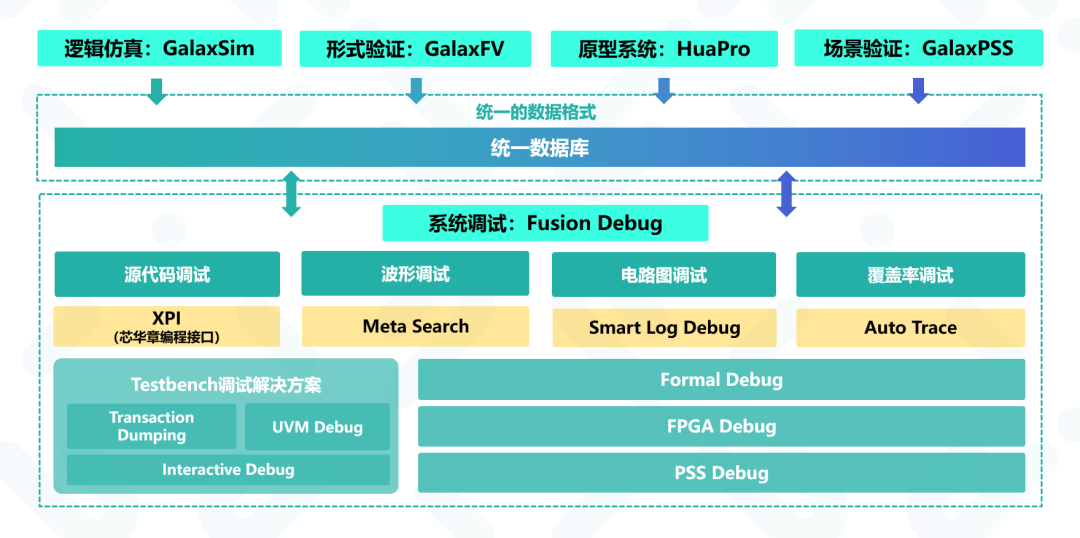

基于統一數據庫的智能調試分析

基于統一數據的統一調試

除了利用多種靜態和動態的驗證方法和不同的驗證工具,我們都知道,波形、源代碼、電路的調試,以及覆蓋率的分析和改進等工作,占系統芯片設計中4成以上的工作量。因此,更敏捷的驗證需要各種EDA工具能統一和合并所產生的大量基礎數據,并提供給芯片設計驗證團隊統一的調試工具,基于這些基礎數據去進行分析調試,以貫穿整個驗證環節,支持更敏捷的迭代。芯華章的FusionDebug,貫穿之前提及的系統驗證技術與工具,具備開放的接口,高效的壓縮和讀寫速度,支持分布式調試,能很好的支持敏捷驗證快速迭代,分析與調試所需。

更智能和更高抽象層次的調試

驗證計算與調試分析是不能分離的,所有驗證過程中暴露出來的設計問題,目前都需要人工從電路到架構自下而上的分析去解決。但敏捷驗證中的標準化接口模塊復用、分析工具智能化、調試工具智能化,可以逐步輔助解決從電路、信號波形和Log數據向設計邏輯和架構的逆向映射,提高調試的抽象層次,并利用基于大數據的機器學習方法縮小問題分析空間,最終實現在設計層面而不是電路層面解決絕大部分的調試需求,并減少調試對人工投入的需求。

結語

敏捷開發思想已經普遍應用在軟件和系統產品工程領域,而在芯片設計工程中還處于探索階段,但敏捷的思想和價值對EDA及芯片行業的發展非常重要,因此發展更加敏捷的芯片驗證技術,推動芯片的全流程敏捷開發真正實現,對實現芯華章科技提出的EDA 2.0發展目標極其關鍵,未來發展還需要整個行業的共同努力。芯華章針對數字芯片驗證流程已經提供了多種驗證產品,配合芯華章的通用基礎技術模塊共同構成“智V驗證平臺”。

同時芯華章于2022年成立研究院,目前也在開展敏捷驗證相關的系列研究,歡迎行業專家與同仁的交流、合作,共同推動敏捷驗證和敏捷開發在EDA設計流程中的應用。

審核編輯:郭婷

-

芯片

+關注

關注

456文章

51180瀏覽量

427268 -

eda

+關注

關注

71文章

2788瀏覽量

173866 -

C語言

+關注

關注

180文章

7614瀏覽量

137714

原文標題:敏捷驗證加速系統設計與架構創新

文章出處:【微信號:X-EPIC,微信公眾號:芯華章科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

低代碼在敏捷開發中的應用

PLM如何推動企業實現全生命周期管理的數字化轉型

無線充芯片-手機無線充電芯片-無線充電芯片開發定制

華為云 Astro 低代碼平臺開啟 AI 敏捷組裝時代,探索低代碼創新無限可能

芯華章生態戰略亮相DAC,發布全流程敏捷驗證管理器FusionFlex,并聯合華大九天推出數模混合仿真解決方案

芯華章推出EDA全流程敏捷驗證管理器昭睿FusionFlex

大規模 SoC 原型驗證面臨哪些技術挑戰?

FPGA是實現敏捷、安全的工業4.0發展的關鍵

fpga原型驗證流程

硬件敏捷怎么玩?

敏捷驗證推動芯片的全流程敏捷開發真正實現

敏捷驗證推動芯片的全流程敏捷開發真正實現

評論