相比`define的全局scope,“l(fā)et” 可以只作用在局部scope。

“l(fā)et”和`define一樣也是定義了一個(gè)文本替換。

define是驗(yàn)證環(huán)境開發(fā)以及RTL開發(fā)過程中的一個(gè)非常常用的技巧,但是define是全局的,這是優(yōu)點(diǎn)也是缺點(diǎn),很容易就會(huì)對(duì)其他模塊的驗(yàn)證環(huán)境產(chǎn)生干擾。

相比來說,“l(fā)et” 的使用更加安全,因?yàn)椤發(fā)et”只會(huì)作用到局部。

module example; logic r1,r2, r3,r4,clk,clk1; let exDefLet = r1 || r2; always @ (posedge clk) begin: ablock let exDefLet = r1 & r2; r3=exDefLet; end always @ (posedge clk1) begin: bblock r4=exDefLet; end endmodule

就等價(jià)于

module example; logic r1,r2, r3,r4,clk,clk1; always @ (posedge clk) begin :ablock r3=r1 & r2; end always @ (posedge clk1) begin: bblock r4=r1 || r2 ; end endmodule

如果我們使用的是`define,而不是“l(fā)et”。

module example; logic r1,r2, r3,r4,clk,clk1; `defne exDefLet r1 || r2; always @ (posedge clk) begin :ablock `defne exDefLet r1 & r2; r3=`exDefLet; end always @ (posedge clk1) begin: bblock r4=`exDefLet; end endmodule

后面的全局define會(huì)覆蓋前面的define,那上面的例子就等價(jià)于

module example; logic r1,r2, r3,r4,clk,clk1; always @ (posedge clk) begin: ablock r3 = r1 & r2; end always @ (posedge clk1) begin: bblock r4 = r1 & r2; end endmodule

審核編輯:湯梓紅

-

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110395 -

System

+關(guān)注

關(guān)注

0文章

165瀏覽量

37076 -

LET

+關(guān)注

關(guān)注

0文章

11瀏覽量

10264

原文標(biāo)題:SystemVerilog中的“l(fā)et”語法

文章出處:【微信號(hào):芯片驗(yàn)證工程師,微信公眾號(hào):芯片驗(yàn)證工程師】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

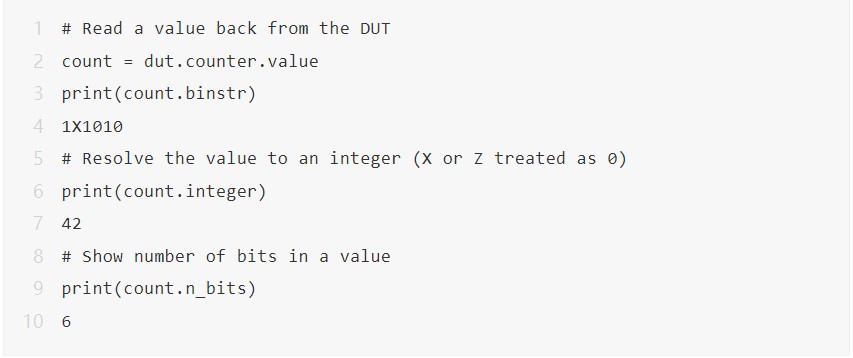

cocotb中的基礎(chǔ)語法與SystemVerilog中的常用語法對(duì)照總結(jié)

SystemVerilog中的Virtual Methods

systemverilog------Let's Go

使用SystemVerilog來簡(jiǎn)化FPGA中接口的連接方式

剛裝IC617建一個(gè)systemverilog的cell總是報(bào)語法錯(cuò)誤怎么去解決?

cocotb中的基礎(chǔ)語法

SystemVerilog中的Shallow Copy

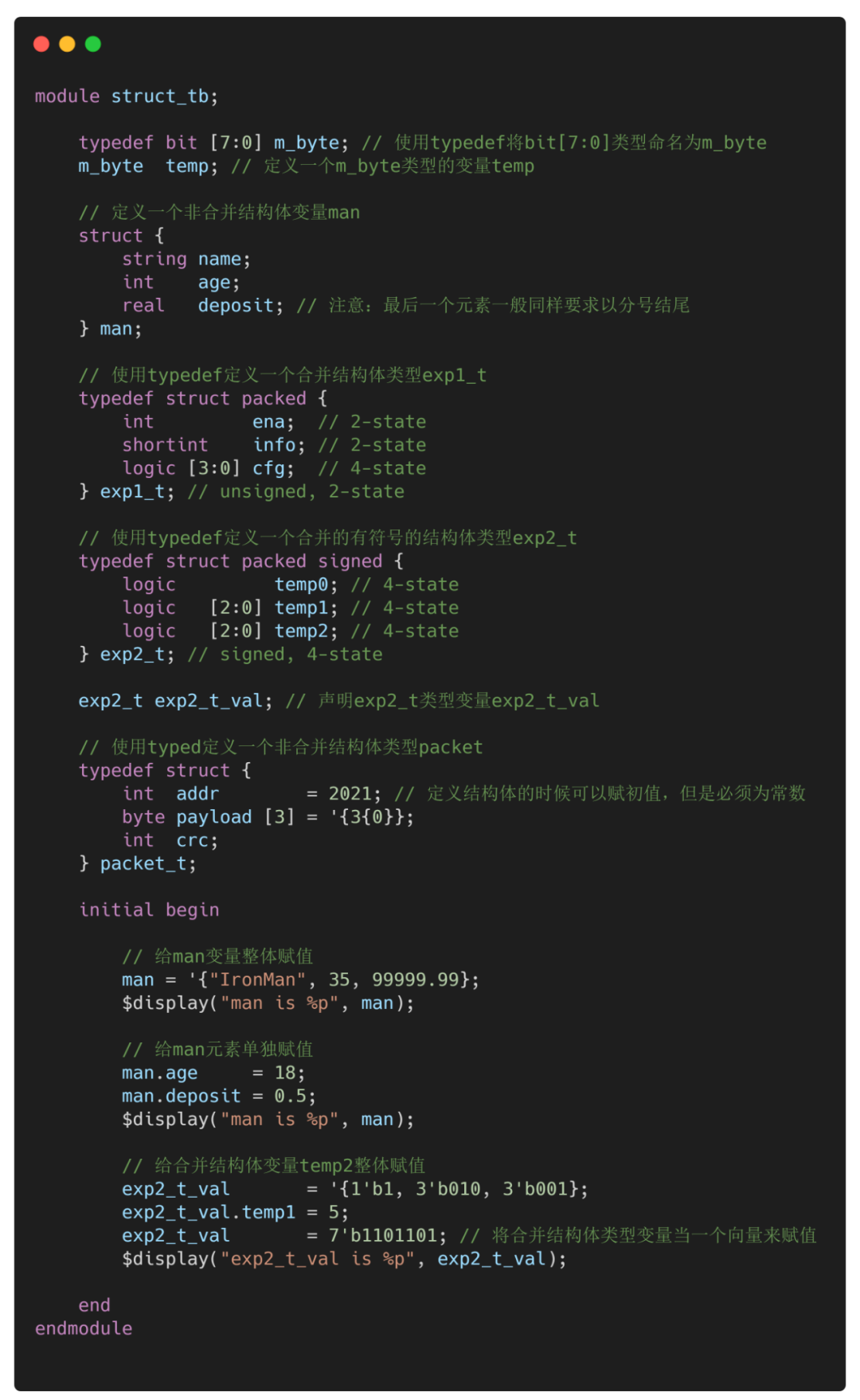

SystemVerilog中至關(guān)重要的結(jié)構(gòu)體和自定義類型

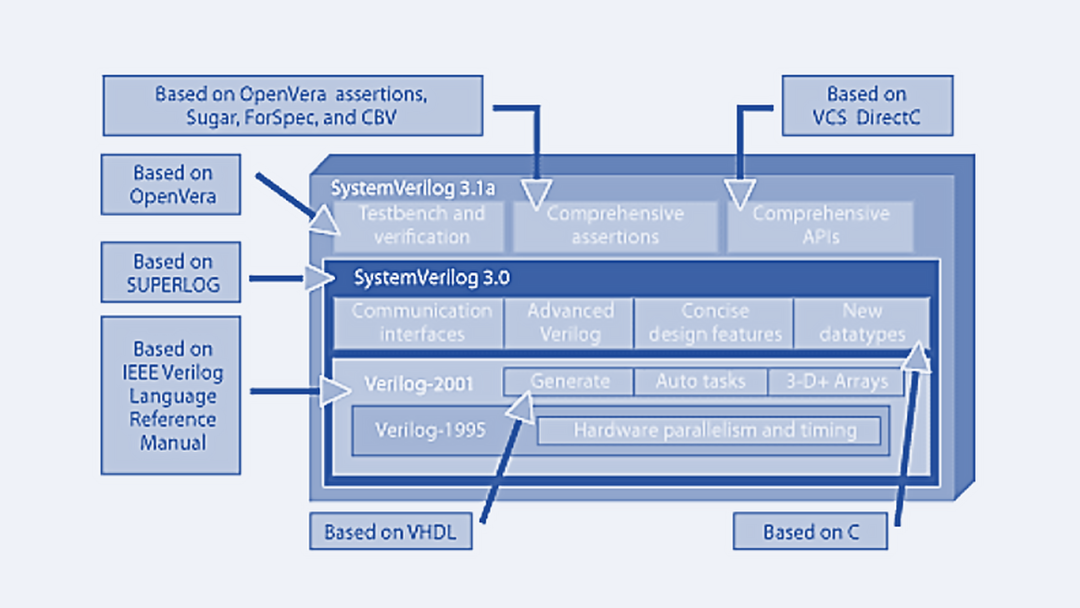

解碼國產(chǎn)EDA數(shù)字仿真器系列之二 | 如何實(shí)現(xiàn)全面的SystemVerilog語法覆蓋?

如何實(shí)現(xiàn)全面的SystemVerilog語法覆蓋

SystemVerilog中的“l(fā)et”語法

SystemVerilog中的“l(fā)et”語法

評(píng)論