在使用Altium Designer的過程中

我們收到許多用戶的提問

Q&A系列將針對用戶關注度較高的問題

請Altium技術專家為大家答疑解惑

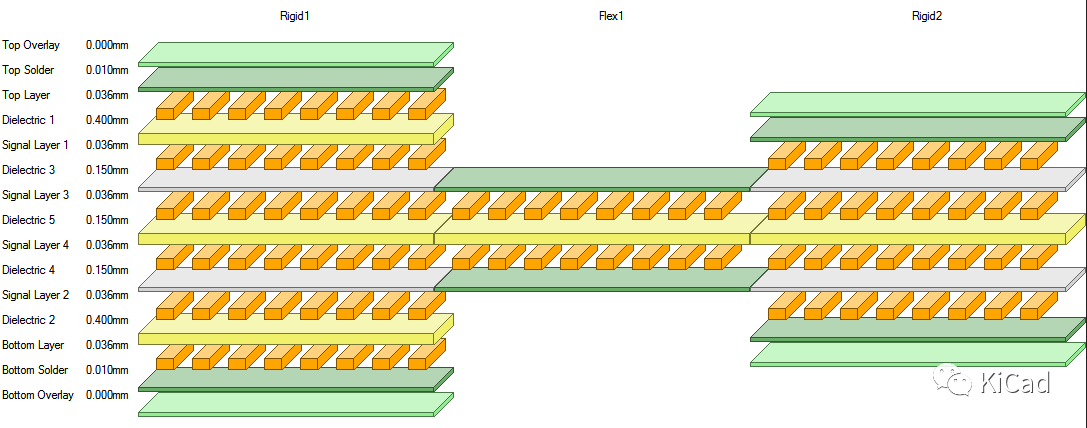

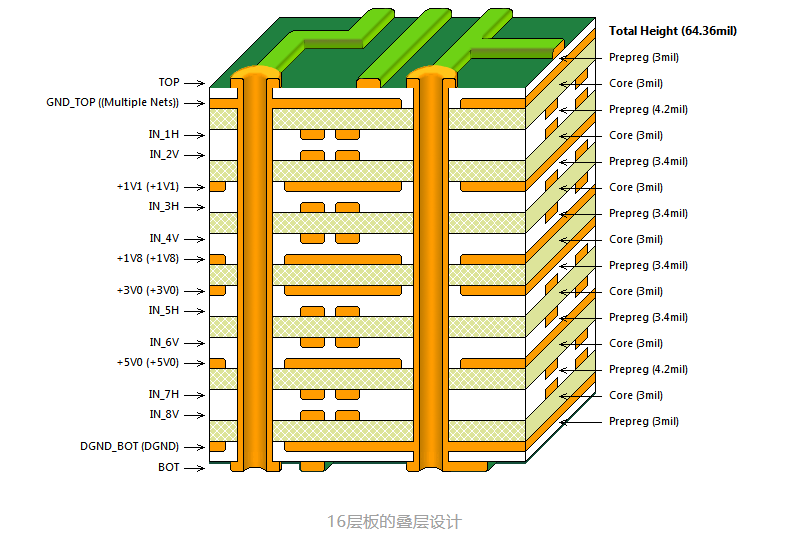

為存檔而在*.PcbDoc中放置層堆棧表等文檔時可能會遇到一些問題,因為它可能不支持所有新增元素,例如,表面處理層。Altium認為舊方法有些過時,因此希望能引導您使用Draftsman。

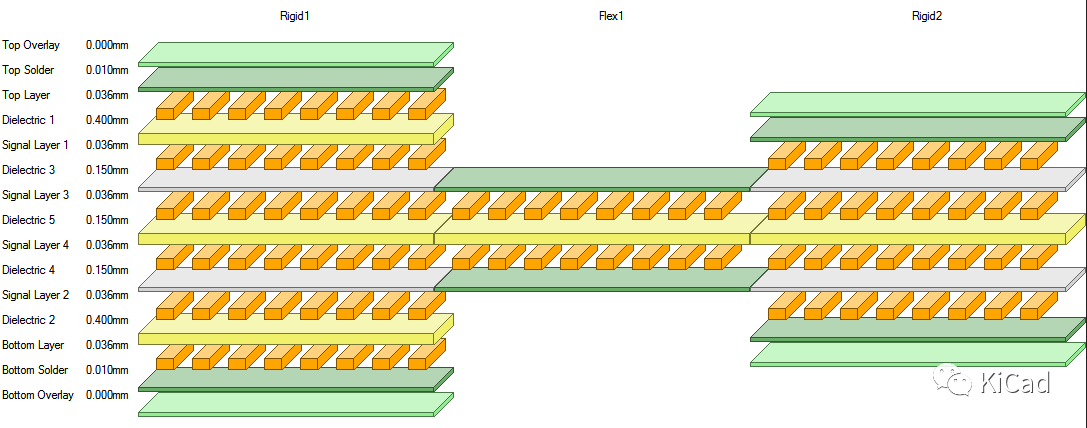

我們建議使用Draftsman來滿足您所有的圖紙綜合輸出需求。Draftsman乍一看可能令人望而卻步,但是它其實可以變得簡單,僅需在 Draftsman頁面上添加一個堆棧層并將其配置為outjob的一部分即可。

以下是示例步驟:

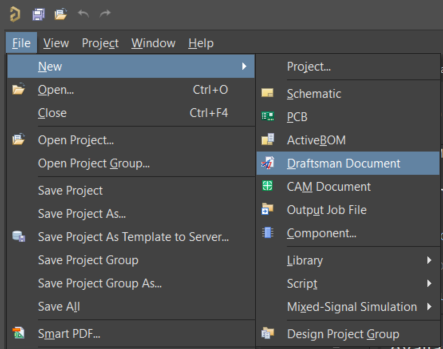

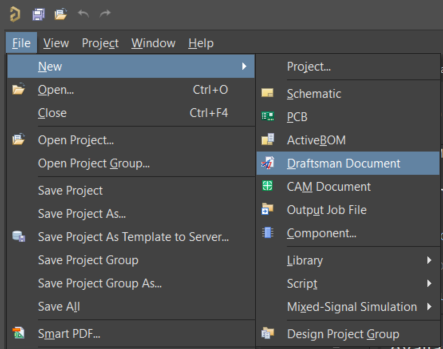

1.在您的項目中添加一個新的Draftsman文檔,并使其在您的工作區中處于活動狀態。

2.從菜單中選擇Place ? Layer Stack Legend,然后將圖層堆棧在頁面上。

3.保存Draftsman文檔。

4.在您的Outjob中,將剛剛創建的Draftsman添加至Documentation Outputs,并將其與Output Containers中的PDF對象鏈接。

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

PDF

-

Altium Designer

-

Draftsman

原文標題:【Q&A】層堆棧導出PDF時缺少底部表面處理層

文章出處:【微信號:AltiumChina,微信公眾號:Altium】歡迎添加關注!文章轉載請注明出處。

相關推薦

原子層為單位,逐步去除材料表面,從而實現高精度、均勻的刻蝕過程。它與 ALD(原子層沉積)相對,一個是逐層沉積材料,一個是逐層去除材料。 ?

![的頭像]() 發表于

發表于 01-20 09:32

?70次閱讀

在鈣鈦礦/硅疊層太陽能電池中,使用硅異質結(SHJ)太陽能電池作為底部電池是實現高效率的最有前景的方法之一。目前,大多數高效疊層太陽能電池使用厚的浮區(FZ)底部電池,這在工業大規模生

![的頭像]() 發表于

發表于 01-17 09:03

?203次閱讀

OSI模型是一個七層的網絡通信框架,每一層都承擔著特定的職責,以確保數據能夠從源頭順利傳輸到目的地。從底部的物理層開始,這一層負責在物理媒介

![的頭像]() 發表于

發表于 12-26 15:27

?291次閱讀

在之前的文章中,我們介紹了IEEE 802.3cz[1]協議,MultiGABSE-AU物理層中XMII、PCS子層以及兩個可選功能的相關內容,本篇將介紹MultiGABSE-AU物理層PMA子

![的頭像]() 發表于

發表于 12-23 10:20

?284次閱讀

)的開發和生產。通信堆棧是AUTOSAR架構中的關鍵組成部分,負責處理ECU之間的通信。 AUTOSAR中通信堆棧的配置 通信模型 : AUTOSAR定義了一種分層的通信模型,包括應用層

![的頭像]() 發表于

發表于 12-17 15:01

?373次閱讀

“ ?不同EDA對于PCB中物理層的定義基本相同,比如信號層、絲印、阻焊、助焊等。但對于工藝層(輔助層)的定義會略有不同,比如Altium Designer沒有專門的板框

![的頭像]() 發表于

發表于 11-12 12:21

?574次閱讀

金屬層2(M2)工藝與金屬層1工藝類似。金屬層2工藝是指形成第二層金屬互連線,金屬互連線的目的是實現把第一層金屬或者第三

![的頭像]() 發表于

發表于 10-24 16:02

?376次閱讀

超級電容器因其高功率密度、長循環壽命和快速充放電能力而在許多領域受到重視。這些特性主要歸功于其獨特的雙電層結構。 超級電容器的工作原理 雙電層的形成 : 當電極浸入電解質中時,電極表面的電荷會吸引

![的頭像]() 發表于

發表于 09-27 10:29

?444次閱讀

電子發燒友網站提供《將一個第15.4層堆棧傳感器連接到多個網關.pdf》資料免費下載

發表于 09-26 11:05

?0次下載

。這種結構使得四層鋁基板在散熱、電氣性能、機械強度等方面都具有出色的表現,因此被廣泛應用于各種高功率、高可靠性的電子設備中。 四層鋁基板的制造工藝主要包括基板制備、電路層制作、層壓、鉆孔、鍍銅、

![的頭像]() 發表于

發表于 08-08 11:40

?377次閱讀

面積為0.5um。其中,200MP型號的傳感器用于對標三星旗下HP2、HP9兩款傳感器,或許它會被用在三星S25系列中。 在過去10多年時間里,索尼一直是CMOS圖像傳感器技術領導者,先是用銅互連技術代替鋁互聯技術,接著是BSI代替FSI,堆棧式結構實現了傳感器集成大規模數字電路,2

![的頭像]() 發表于

發表于 08-02 16:24

?784次閱讀

在深度學習中,卷積神經網絡(Convolutional Neural Network, CNN)是一種特別適用于處理圖像數據的神經網絡結構。它通過卷積層、池化層和全連接層的組合,實現了

![的頭像]() 發表于

發表于 07-11 14:18

?6872次閱讀

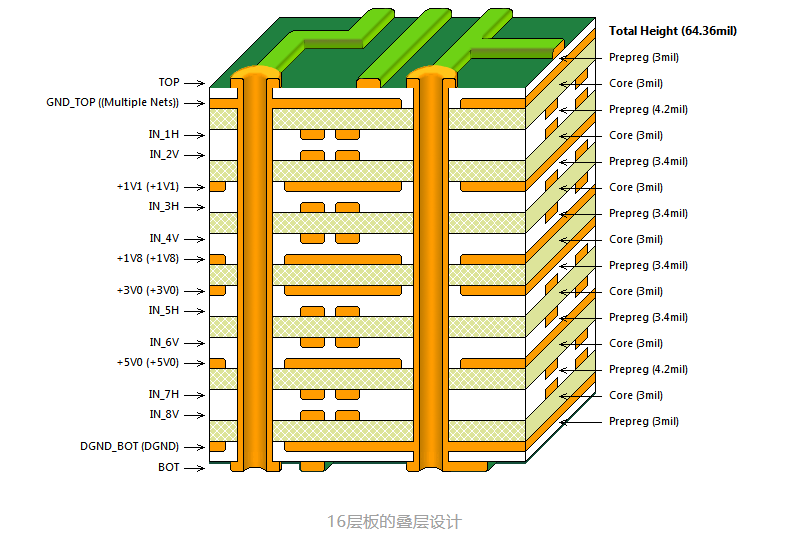

對于信號層,通常每個信號層都與內電層直接相鄰,與其他信號層有有效的隔離,以減小串擾。在設計過程中,可以考慮多層參考地平面,以增強電磁吸收能力。

![的頭像]() 發表于

發表于 04-10 16:02

?2637次閱讀

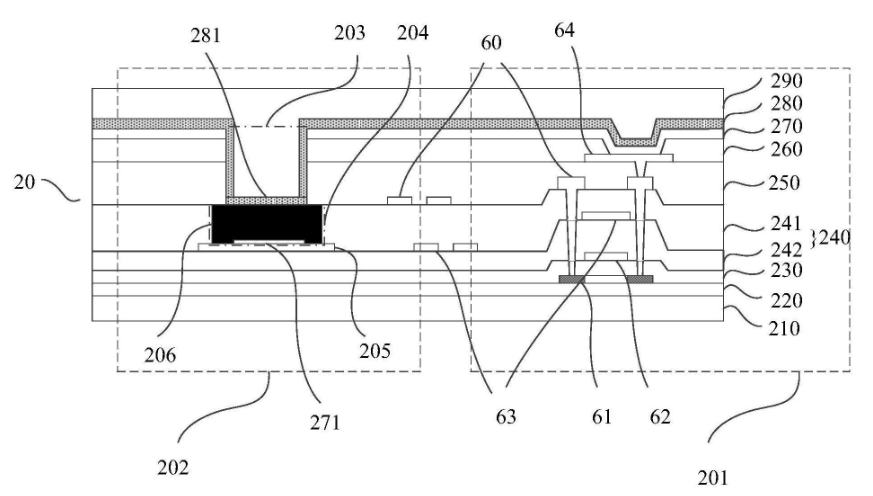

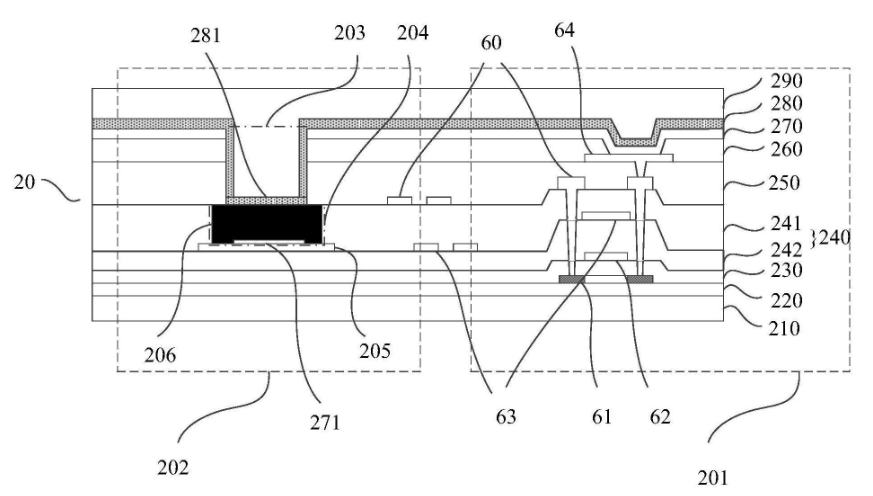

該專利主要內容如下:顯示面板由層間介質層、平坦化層和像素界定層有序堆疊而成;在顯示面板非像素區的第一功能層內置入內切結構和至少一個電極搭接結

![的頭像]() 發表于

發表于 02-21 09:40

?821次閱讀

以下幾個因素: 焊盤平整度 正如之前提到的,某些表面處理技術可能會導致表面不平整,這可能會影響性能、焊接能力和其它因素。如果表面平整度是一個重要的考慮因素,那么您應該考慮具有薄而均勻

![的頭像]() 發表于

發表于 02-16 17:09

?2017次閱讀

層堆棧導出PDF時缺少底部表面處理層

層堆棧導出PDF時缺少底部表面處理層

評論