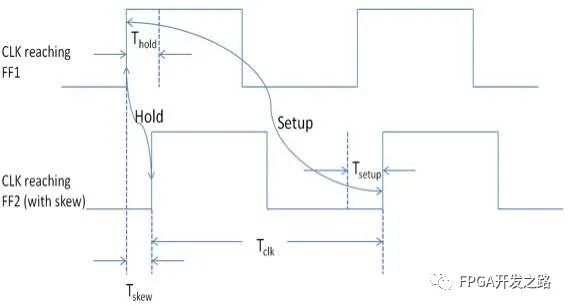

做數(shù)字電路設(shè)計的可能都見過圖一所示的setup和hold時間檢查,從圖中可以明顯看出,setup time檢查下一個沿,而hold time檢查同一個沿。那么這是為什么呢 ?

圖1

數(shù)字電路的工作原理

以數(shù)字電路設(shè)計常見的狀態(tài)機(jī)為例,下一個狀態(tài)的值總是由當(dāng)前狀態(tài)加一些判斷條件決定。為了保證下一個狀態(tài)值的正確,新的狀態(tài)值要在下一個時鐘沿被正確采樣,同時不能被當(dāng)前時鐘沿采樣。

因此,setup time 的檢查是為了保證數(shù)據(jù)在下一個時鐘沿被正確采樣,而 hold time 的檢查是保證數(shù)據(jù)不被當(dāng)前沿采樣或破壞,滿足了這兩點(diǎn),數(shù)字電路便能正常工作。

Hold Time Violation

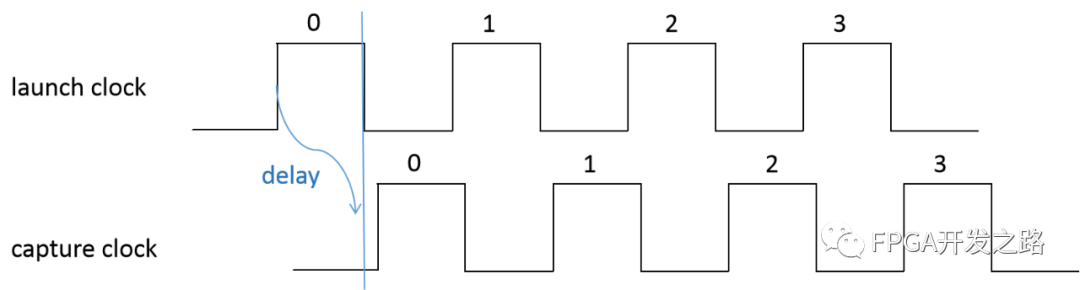

考慮一個兩級移位寄存器,其launch clock 和 capture clock如圖2所示。可以看到clock skew非常大,大于半個時鐘周期。假設(shè)數(shù)據(jù)的延遲小于半個時鐘周期,那么 hold time 的檢查公式必然不滿足, 即 Tcq + Tcomb < Tclk_skew + Thold。

對于這個兩級移位寄存器,我們希望的值是 00(cycle0), 01(cycle1), 10(cycle2),00(cycle3)。但是由于第二級寄存器有hold time violation,數(shù)據(jù)在當(dāng)前沿就被采樣,那么我們實際看到的值為 00(cycle0),11(cycle1),00(cycle2),00(cycle3),完全是錯誤的結(jié)果。

圖2

時序違反一定會有亞穩(wěn)態(tài)發(fā)生嗎

不一定。寄存器進(jìn)入亞穩(wěn)態(tài)有兩個前提條件,一是數(shù)據(jù)要發(fā)生變化,二是數(shù)據(jù)的變化要發(fā)生在setup time和hold time限制的范圍內(nèi)。以上述圖2為例,假設(shè)數(shù)據(jù)的變化沒有出現(xiàn)在setup和hold time限制的范圍內(nèi),盡管是有hold time violation,也是沒有亞穩(wěn)態(tài)發(fā)生的。

-

寄存器

+關(guān)注

關(guān)注

31文章

5363瀏覽量

121151 -

數(shù)字電路

+關(guān)注

關(guān)注

193文章

1629瀏覽量

80821 -

Setup

+關(guān)注

關(guān)注

0文章

30瀏覽量

12040

原文標(biāo)題:為什么setup檢查下一個沿而hold檢查當(dāng)前沿

文章出處:【微信號:FPGA開發(fā)之路,微信公眾號:FPGA開發(fā)之路】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

FPC檢查,FPC檢查是什么意思

Setup/Hold Time Problem

解釋下setup和hold time

什么是Setup和Hold時間

建立時間和保持時間(setup time 和 hold time)

技術(shù)研發(fā)是華為基石 華為下一個研究前沿是AI

如何為下一個符號消除PCB設(shè)計項目

關(guān)于FPGA的五個基本概念

特斯拉披露:下一個超級工廠可能在美國而不在印度

Verilog中四個基礎(chǔ)的時序分析

5個FPGA基本概念問答

啟用負(fù)時序檢查的步驟

通過解剖一個邊沿觸發(fā)器簡要說明setup和hold產(chǎn)生原因

Wi-Fi 6E:Wi-Fi的下一個前沿

為什么setup檢查下一個沿而hold檢查當(dāng)前沿

為什么setup檢查下一個沿而hold檢查當(dāng)前沿

評論