Cadence 于 10 月 12 日發布了 Cadence Certus Closure Solution,這是同類型產品中首款采用大規模并行計算和分布式架構的全自動環境。Cadence Certus Closure Solution 環境實現了設計收斂的自動化,并將整個設計收斂周期從數周縮短至一夜之間 —— 包括從簽核優化到布線、靜態時序分析(STA)和參數提取。

該解決方案支持無限容量,勝任大型芯片設計項目,與目前其他方法和流程相比,最多可將生產力提高 10 倍。傳統流程如下圖的藍色輪軸所示,每個迭代單一階段的完整運行都需要 5 - 7 天,且迭代次數無法提前預知,甚至最多需要 30 次。簡單計算一下,全芯片所有流程加起來可能需要耗時 3 個月之久。

上述流程會用到兩個主要工具,分別是用于模塊層次優化的 Tempus ECO,以及用于 SoC 層面靜態時序分析的 Tempus STA。這里缺失了全芯片(或子系統)優化與簽核。至于分區間功耗恢復等則只能忽略,因為實在沒時間處理。

Cadence Certus Closure Solution 將上述流程自動化,實現隔夜優化和簽核收斂。在 Innovus 工作流程中,基于 Tempus 簽核解決方案(STA 或 DSTA)及 Tempus ECO 的基礎中,Certus Closure Solution 可以進一步發揮時序簽核和 ECO 技術在廣度和深度上的優勢。

顯而易見,我們是通過將所有任務大規模分布處理以及全流程自動化來達成這一目標的。下方圖表列出了所有細節。作為大規模并行系統,管理器會負責控制所有任務,并將計算結果匯總以判定下一步該做什么。

此外,模塊之間的功率恢復功能可以降低 10% - 15% 的功耗,全芯片最高降低 5%。這也就是文中之前提到的,人工流程的話根本沒時間處理這個問題。

總結一下,Certus 的核心優勢包括:

創新的可擴展架構:Cadence Certus Closure Solution 采用的分布式客戶端管理器支持全自動化,分布式分層優化以及芯片層級的簽核收斂。

提高工程設計效率:它減少了在多個團隊中進行多次冗長迭代的需要,縮短收斂時間

SmartHub 界面:增強的 GUI 擁有更好的交互性和更詳細的時序糾錯,支持交叉驗證以實現設計收斂的最后環節。

增量簽核:周轉時間縮短 10 倍,支持對變更模塊進行靈活恢復和替換,利用增量時序刷新縮短設計收斂時間。

3D-IC 設計效率:與 Cadence Integrity 3D-IC 解決方案緊密集成,幫助用戶收斂異構工藝中裸片間的時序路徑。

-

芯片

+關注

關注

456文章

51182瀏覽量

427279 -

Cadence

+關注

關注

65文章

930瀏覽量

142456 -

管理器

+關注

關注

0文章

248瀏覽量

18616

原文標題:Cadence Certus Closure Solution 助力全芯片并行優化

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

使用獨立ADC和使用MCU的內部ADC來實現模數轉換,有什么性能、技術上的區別嗎?

按照TAS5711的datasheet中的上電時序進行上電,芯片正常工作,但是無法編輯寄存器,是時序有問題嗎?

節能回饋式負載技術創新與發展

淺談國產異構雙核RISC-V+FPGA處理器AG32VF407的優勢和應用場景

Cadence Quantus DSPF Interactive Output的優勢和特點

射頻技術有哪些優勢和劣勢

蘋果最新消息 韋德布什上調蘋果目標價 庫克:將繼續在AI技術上投資

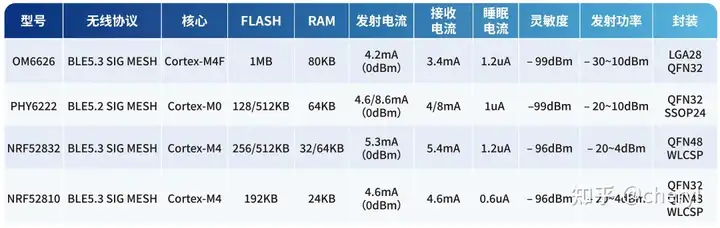

基于OM6626 NRF528210系列的ESL電子價簽應用

Certus Closure Solution可發揮時序簽核和ECO技術上的優勢

Certus Closure Solution可發揮時序簽核和ECO技術上的優勢

評論