隊列同樣可以保存類對象,這在驗證環(huán)境中是非常有用的,下面是一個例子:

class animals;

string sname;

int i1;

function new (string name="UN");

sname = name;

i1++;

endfunction

endclass

module tb;

// queue of class type 'animals'

animals alist [$];

initial begin

animals f, f2; //declare two variables of type animals

// Create a new class object 'f' and push into the queue

f = new ("lion");

alist.push_front (f);

// Create another class object 'f2'and push into the queue

f2 = new ("tiger");

alist.push_back (f2);

// Iterate through queue and access each class object

foreach (alist[i]) begin

$display ("alist[%0d] = %s", i, alist[i].sname);

$display ("alist[%0d] = %p", i, alist[i]);

end

// Simply display the whole queue

$display ("alist = %p", alist);

end

endmodule

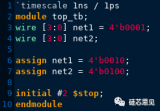

仿真log:

# KERNEL: alist[0] = lion

# KERNEL: alist[0] = '{sname:"lion", i1:1}

# KERNEL: alist[1] = tiger

# KERNEL: alist[1] = '{sname:"tiger", i1:1}

# KERNEL: alist = '{'{sname:"lion", i1:1}, '{sname:"tiger", i1:1}}

該示例聲明了一個名為“animals”的類,字符串“name”初始化為“UN”。

聲明了兩個“animals”類型的對象" f "和“f2”。

創(chuàng)建“animals”類型的對象隊列“alist”。

分別實例化兩個對象“f”和“f2”,然后push到隊列中。

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規(guī)問題,請聯系本站處理。

舉報投訴

-

Verilog

+關注

關注

28文章

1351瀏覽量

110397 -

System

+關注

關注

0文章

165瀏覽量

37078 -

隊列

+關注

關注

1文章

46瀏覽量

10927

原文標題:SystemVerilog中的類隊列

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

SystemVerilog 3.1a語言參考手冊

本參考手冊詳細描述了Accellera為使用Verilog硬件描述語言在更高的抽象層次上進行系統(tǒng)的建模和驗證所作的擴展。這些擴展將Verilog語言推向了系統(tǒng)級空間和驗證級空間。SystemVerilog

發(fā)表于 07-22 12:14

?188次下載

SystemC 和SystemVerilog的比較

就 SystemC 和 SystemVerilog 這兩種語言而言, SystemC 是C++在硬件支持方面的擴展,而 SystemVerilog 則繼承了 Verilog,并對 Verilo

發(fā)表于 08-16 10:52

?5412次閱讀

System Verilog與verilog的對比

SystemVerilog語言簡介 SystemVerilog是一種硬件描述和驗證語言(HDVL),它基于IEEE1364-2001 Verilog硬件描述語言(HDL),并對其進行了擴展,包括擴充

使用Verilog/SystemVerilog硬件描述語言練習數字硬件設計

HDLBits 是一組小型電路設計習題集,使用 Verilog/SystemVerilog 硬件描述語言 (HDL) 練習數字硬件設計~

FPGA學習-SystemVerilog語言簡介

SystemVerilog是一種硬件描述和驗證語言(HDVL),它基于IEEE1364-2001 Verilog硬件描述語言(HDL),并對其進行了擴展,包括擴充了 C語言 數據類型、結構、壓縮和非

從Verilog PLI到SystemVerilog DPI的演變過程

寫過Verilog和systemverilog的人肯定都用過系統(tǒng)自定義的函數$display,這是預定好的,可以直接調用的功能。

如何實現全面的SystemVerilog語法覆蓋

SystemVeirlog的全面支持是開發(fā)商用仿真器的第一道門檻。市面上可以找到不少基于純Verilog的仿真器,但是真正能完整支持SystemVerilog 的仍然屈指可數。如何全面地支持SystemVerilog語言,是開發(fā)

verilog-2005和systemverilog-2017標準規(guī)范

作為邏輯工程師,在FPGA和數字IC開發(fā)和設計中,一般采用verilog,VHDL或SystemVerilog等作為硬件描述語言進行工程設計,將一張白板描繪出萬里江山圖景。

SystemVerilog在硬件設計部分有哪些優(yōu)勢

談到SystemVerilog,很多工程師都認為SystemVerilog僅僅是一門驗證語言,事實上不只如此。傳統(tǒng)的Verilog和VHDL被稱為HDL(Hardware Description

SystemVerilog相比于Verilog的優(yōu)勢

我們再從對可綜合代碼的支持角度看看SystemVerilog相比于Verilog的優(yōu)勢。針對硬件設計,SystemVerilog引入了三種進程always_ff,always_comb

verilog同步和異步的區(qū)別 verilog阻塞賦值和非阻塞賦值的區(qū)別

Verilog中同步和異步的區(qū)別,以及阻塞賦值和非阻塞賦值的區(qū)別。 一、Verilog中同步和異步的區(qū)別 同步傳輸和異步傳輸是指數據在電路中

systemverilog和verilog的區(qū)別

systemverilog和verilog的區(qū)別

評論