本文來(lái)源電子發(fā)燒友社區(qū),作者:卿小小_9e6, 帖子地址:https://bbs.elecfans.com/jishu_2304220_1_1.html

飛凌RZ/G2L開(kāi)發(fā)板使用的CPU(RZ/G2L)是瑞薩在智能工控領(lǐng)域的一款高性能、超高效處理器。 RZ/G2L采用ARMCortex-A55內(nèi)核,運(yùn)行頻率高達(dá)1.2GHz, 內(nèi)部集成Arm Cortex-M33@200MHz。 配備Mali-G31 GPU@500MHz圖形處理器及多種顯示接口,并具有豐富的行業(yè)應(yīng)用接口,主要應(yīng)用于各種具有視頻輸出的工控行業(yè)。

1. CPU性能測(cè)試飛凌RZ/G2L開(kāi)發(fā)板使用的CPU(RZ/G2L)是瑞薩在智能工控領(lǐng)域的一款高性能、超高效處理器。 RZ/G2L采用ARMCortex-A55內(nèi)核,運(yùn)行頻率高達(dá)1.2GHz, 內(nèi)部集成Arm Cortex-M33@200MHz。 配備Mali-G31 GPU@500MHz圖形處理器及多種顯示接口,并具有豐富的行業(yè)應(yīng)用接口,主要應(yīng)用于各種具有視頻輸出的工控行業(yè)。

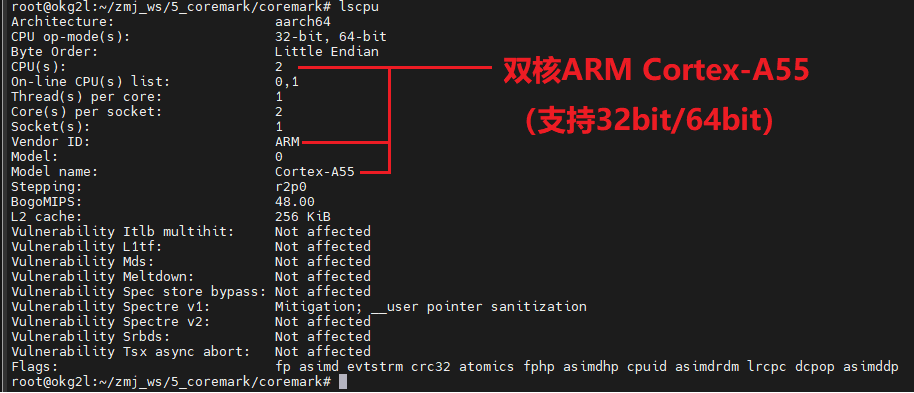

1.1 查看CPU信息

查看CPU信息,反饋結(jié)果是ARM Cortex-A55雙核,支持32-bit/64-bit兩種模式,L2-Cache大小為256kB。

- //------查看CPU信息:lscpu

- //---指令

- lscpu

- //---log信息

- Architecture: aarch64

- CPU op-mode(s): 32-bit, 64-bit

- Byte Order: Little Endian

- CPU(s): 2

- On-line CPU(s) list: 0,1

- Thread(s) per core: 1

- Core(s) per socket: 2

- Socket(s): 1

- Vendor ID: ARM

- Model: 0

- Model name: Cortex-A55

- Stepping: r2p0

- BogoMIPS: 48.00

- L2 cache: 256 KiB

- Vulnerability Itlb multihit: Not affected

- Vulnerability L1tf: Not affected

- Vulnerability Mds: Not affected

- Vulnerability Meltdown: Not affected

- Vulnerability Spec store bypass: Not affected

- Vulnerability Spectre v1: Mitigation; __user pointer sanitization

- Vulnerability Spectre v2: Not affected

- Vulnerability Srbds: Not affected

- Vulnerability Tsx async abort: Not affected

- Flags: fp asimd evtstrm crc32 atomics fphp asimdhp cpuid asimdrdm lrcpc dcpop asimddp

1.2 CoreMark

1.2.1 CoreMark簡(jiǎn)介

//------CoreMark簡(jiǎn)介

CoreMark是由EEMBC(Embedded Microprocessor Benchmark Consortium)的Shay Gla-On于2009年提出的一項(xiàng)基準(zhǔn)測(cè)試程序,CoreMark的主要目標(biāo)是簡(jiǎn)化操作,并提供一套測(cè)試單核處理器核心的方法。測(cè)試標(biāo)準(zhǔn)是在配置參數(shù)的組合下單位時(shí)間內(nèi)運(yùn)行的CoreMark程序次數(shù)(單位:CoreMark/MHz),該數(shù)字值越大則說(shuō)明測(cè)試的性能越好。目前在嵌入式CPU行業(yè)中普遍公認(rèn)的性能測(cè)試指標(biāo)的標(biāo)準(zhǔn)主要使用以下三種,MIPS、Dhrystone、Coremark,而CoreMark與Dhrystone一樣,擁有體積小、方便移植、易于理解、免費(fèi)并且顯示單個(gè)數(shù)字基準(zhǔn)分?jǐn)?shù)。與Dhrystone不同的是,Dhrystone的主要部分實(shí)際上暴露了編譯器優(yōu)化工作負(fù)載的能力,而不是實(shí)際MCU或CPU的能力,的性能,而CoreMark具有特定的運(yùn)行和報(bào)告規(guī)則,從而可以避免由于所使用的編譯庫(kù)不同而導(dǎo)致的測(cè)試結(jié)果難以比較。

1.2.2 CoreMark源碼獲取

//------CoreMark源碼獲取

EEMBC在將CoreMark源碼托管在GitHub上可以訪問(wèn)github.com/eembc/coremark直接點(diǎn)擊下載獲得源碼;也可以通過(guò)git命令下載到本地。

- //------CoreMark源碼獲取

- //---直接下載

- https://github.com/eembc/coremark

- //---Git下載

- git clone https://github.com/eembc/coremark.git

CoreMark項(xiàng)目的詳細(xì)介紹,可以查閱當(dāng)前目錄下“coremark/docs/html/index.html”。該項(xiàng)目以下是當(dāng)前目錄的個(gè)文件介紹:

- #在tree命令的輸出中,作了部分刪除(不影響分析整個(gè)CoreMark工程)

- imaginemiracle@:coremark$ tree

- .

- ├── barebones --移植到裸機(jī)環(huán)境下需要修改的目錄

- │ ├── core_portme.c --移植的目標(biāo)平臺(tái)配置信息

- │ ├── core_portme.h --計(jì)時(shí)以及板級(jí)初始化實(shí)現(xiàn)

- │ ├── core_portme.mak --該子目錄的makefile

- │ ├── cvt.c

- │ └── ee_printf.c --打印函數(shù)串口發(fā)送實(shí)現(xiàn)

- ├── core_list_join.c --列表操作程序

- ├── core_main.c --主程序

- ├── coremark.h --項(xiàng)目配置與數(shù)據(jù)結(jié)構(gòu)的定義頭文件

- ├── coremark.md5

- ├── core_matrix.c --矩陣運(yùn)算程序

- ├── core_state.c --狀態(tài)機(jī)控制程序

- ├── core_util.c --CRC計(jì)算程序

- ├── cygwin --x86 cygwin和gcc 3.4(四核,雙核和單核系統(tǒng))的測(cè)試代碼

- │ ├── core_portme.c

- │ ├── core_portme.h

- │ └── core_portme.mak

- ├── freebsd --以下同理,是在不同操作系統(tǒng)下的測(cè)試代碼

- │ ├── ...

- ├── LICENSE.md

- ├── linux

- │ ├── ...

- ├── linux64

- │ ├── ...

- ├── macos

- │ ├── ...

- ├── Makefile

- ├── README.md --自述文件,CoreMark項(xiàng)目的基本介紹

- ├── rtems

- │ ├── ...

- └── simple

- ├── ...

- └──

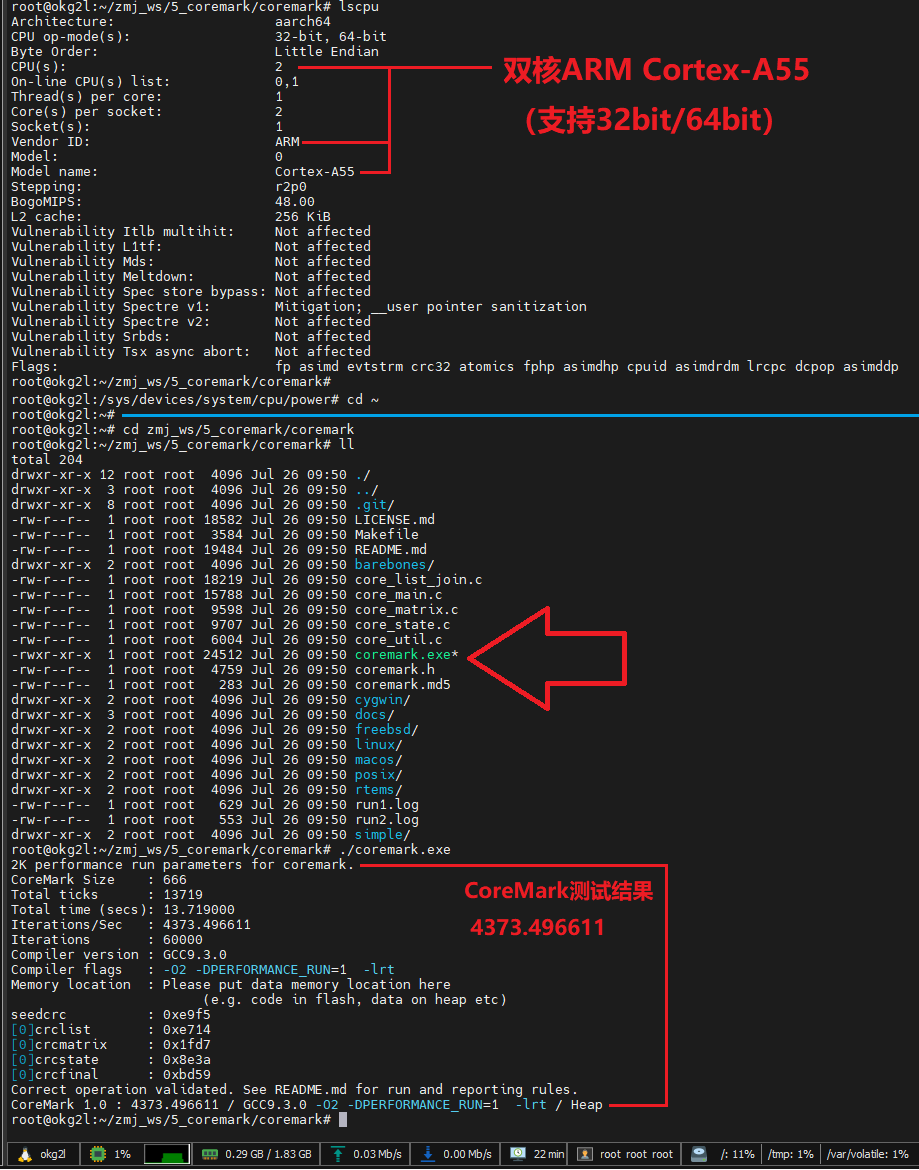

1.2.3 運(yùn)行coremark.exe測(cè)試性能

//------在目標(biāo)平臺(tái)上運(yùn)行coremark.rvexe測(cè)試性能

執(zhí)行命令:./coremark.exe

- //------在目標(biāo)平臺(tái)上運(yùn)行coremark.rvexe測(cè)試性能

- ./coremark.exe

- //------CoreMark得分

- CoreMark 1.0 : 4373.496611

測(cè)試結(jié)果如下圖所示:

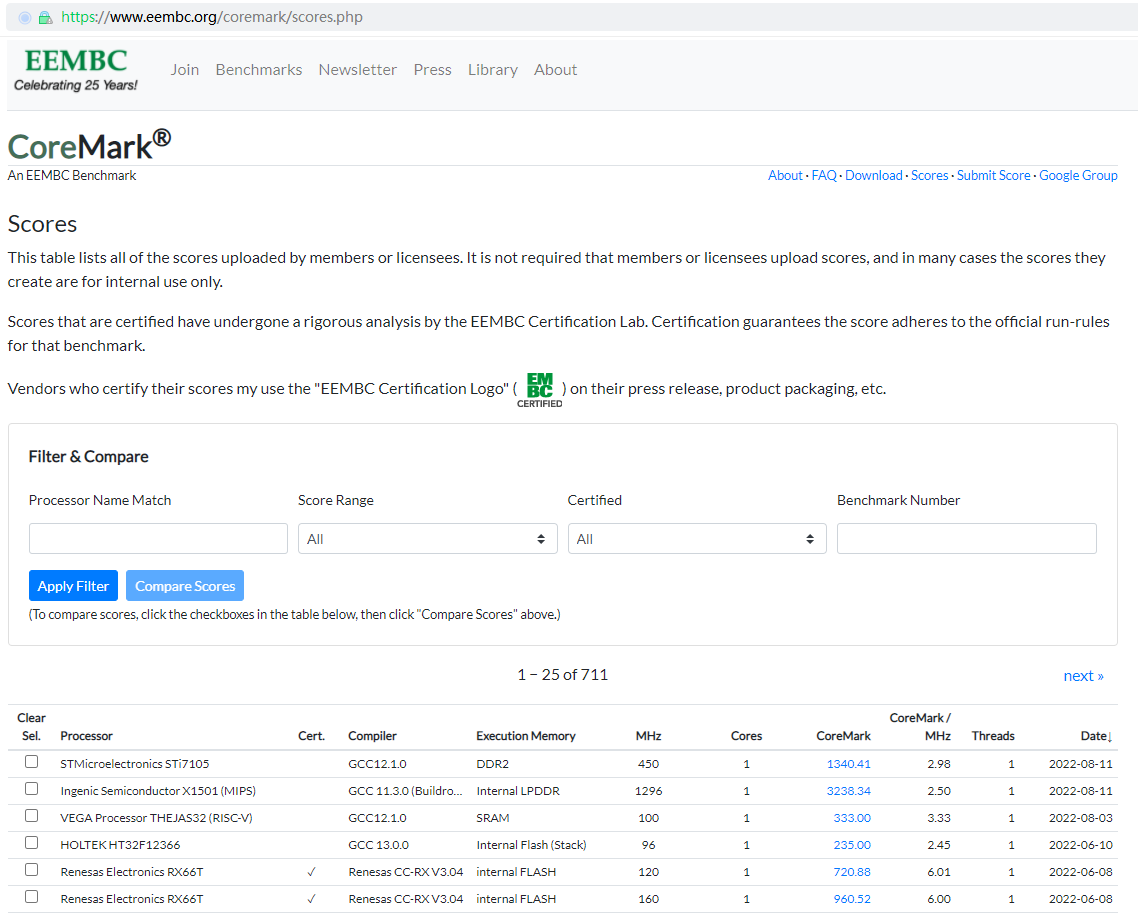

1.2.4 CoreMark跑分榜/結(jié)果比對(duì)

可以看到EEMBC目前已經(jīng)上傳了711款型號(hào)的微控制器CoreMark跑分結(jié)果,可以在EEMBC的coremark/scores里看到。

- //------EEMBC的CoreMark結(jié)果

- https://www.eembc.org/coremark/scores.php

1.2.5 參考鏈接

參考鏈接:《CPU性能測(cè)試——CoreMark篇》

- //------《CPU性能測(cè)試——CoreMark篇》

- https://blog.csdn.net/qq_36393978/article/details/111629341

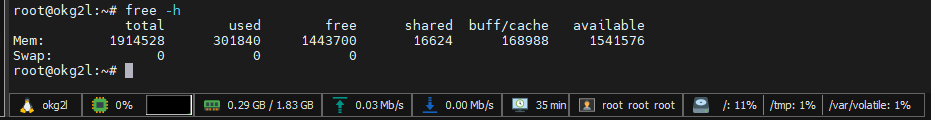

2. DDR內(nèi)存性能測(cè)試

飛凌RZ/G2L開(kāi)發(fā)板上有2GB大小的RAM內(nèi)存,下面使用多種方式進(jìn)行內(nèi)存性能測(cè)試。

2.1 DDR內(nèi)存基本信息

RZ/V2L開(kāi)發(fā)板板載2GB的RAM,通過(guò)“free -h”指令查看DDR內(nèi)存大小。

STREAM內(nèi)存帶寬測(cè)試。

- //------RAM性能測(cè)試

- root@okg2l:~# stream

- STREAM copy latency: 6.44 nanoseconds

- STREAM copy bandwidth: 2485.24 MB/sec

- STREAM scale latency: 7.09 nanoseconds

- STREAM scale bandwidth: 2257.65 MB/sec

- STREAM add latency: 9.65 nanoseconds

- STREAM add bandwidth: 2486.79 MB/sec

- STREAM triad latency: 9.62 nanoseconds

- STREAM triad bandwidth: 2496.10 MB/sec

- //------各測(cè)試項(xiàng)含義

- a.Copy-復(fù)制操作

- 從內(nèi)存單元中讀取一個(gè)數(shù),并復(fù)制到其他內(nèi)存單元中,兩次訪問(wèn)內(nèi)存操作

- b.Scale-乘法操作

- 從內(nèi)存單元中讀取一個(gè)數(shù),與常數(shù)相乘,得到的記過(guò)存到其他內(nèi)存單元,兩次訪問(wèn)內(nèi)存操作

- c.Add-加法操作

- 從兩個(gè)內(nèi)存單元中分別讀取兩個(gè)數(shù),將其進(jìn)行加法操作后,得到的結(jié)果寫(xiě)入另一個(gè)內(nèi)存單元中,3次訪問(wèn)內(nèi)存操作

- d.Triad-前面三種的結(jié)合

- 先從內(nèi)存中讀取一個(gè)數(shù),與一個(gè)常數(shù)相乘得到一個(gè)乘積,然后從另一個(gè)內(nèi)存單元中讀取一個(gè)數(shù)與剛才乘積結(jié)果相加,得到的結(jié)果寫(xiě)入內(nèi)存。

- 共計(jì)3次訪問(wèn)內(nèi)存操作。

- 測(cè)試結(jié)果一般的規(guī)律是Add > Triad > Copy > Scale。一次Add操作需要訪問(wèn)三次內(nèi)存(兩個(gè)讀操作,一個(gè)寫(xiě)操作),Triad操作也需要三次訪問(wèn)內(nèi)存, Copy和Scale操作需要兩次訪問(wèn)內(nèi)存。單位操作內(nèi),訪問(wèn)內(nèi)存次數(shù)越多,越能夠掩蓋訪存延遲,帶寬越大。

- 單核Stream測(cè)試,影響的因素除了內(nèi)存控制器能力外,還有Core的ROB、Load/Store對(duì)其影響,因此不是單純的內(nèi)存帶寬性能測(cè)試。

- 而多核Stream測(cè)試,通過(guò)多核同時(shí)發(fā)出大量?jī)?nèi)存訪問(wèn)請(qǐng)求,能夠更加飽和地訪問(wèn)內(nèi)存,從而測(cè)試到內(nèi)存帶寬的極限性能。

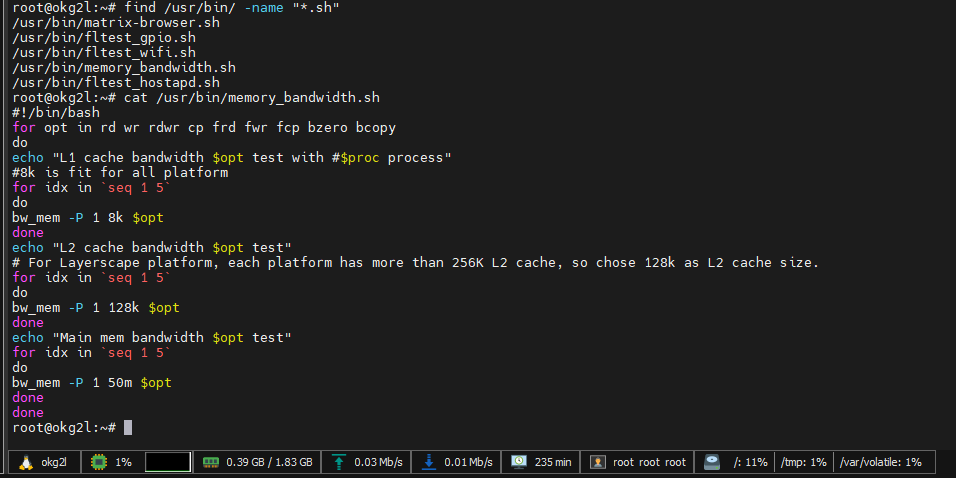

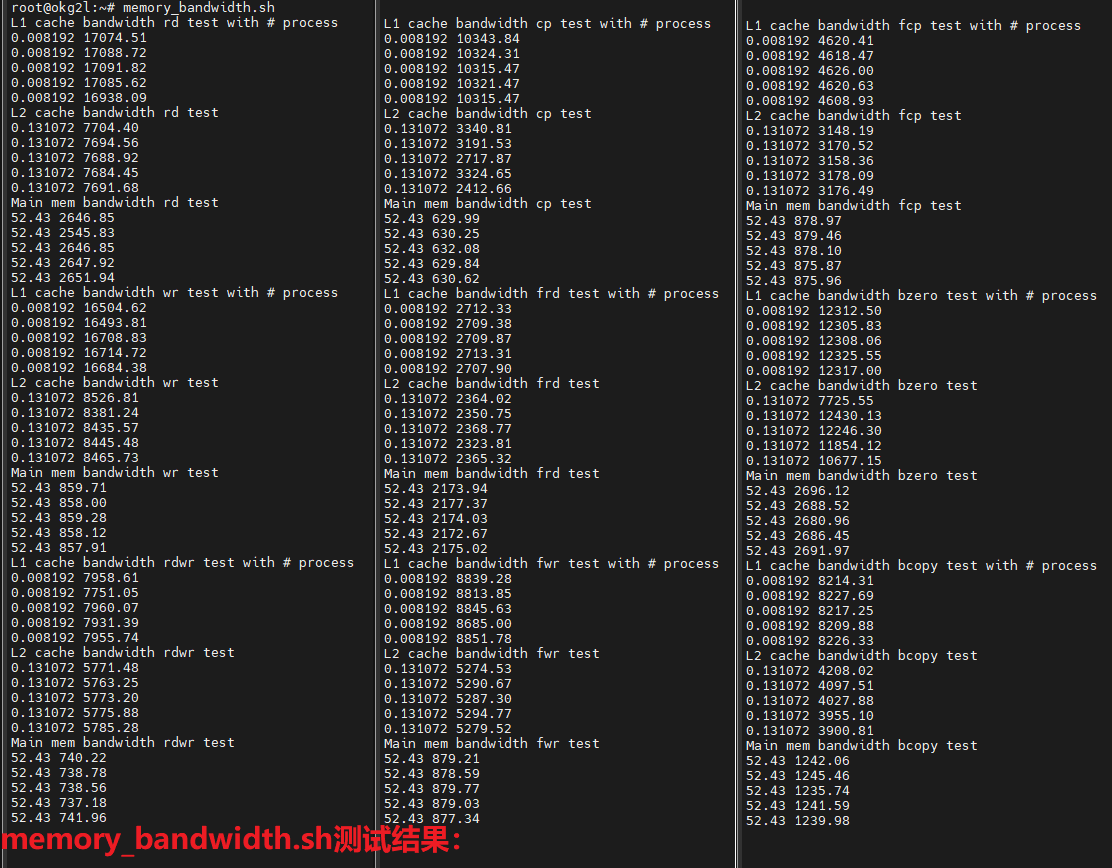

2.3 內(nèi)存帶寬測(cè)試-memory_bandwidth.sh

內(nèi)存帶寬測(cè)試-memory_bandwidth.sh

- //------測(cè)試工具(飛凌系統(tǒng)已帶)

- memory_bandwidth.sh

- //------memory_bandwidth.sh目錄

- /usr/bin/memory_bandwidth.sh

- //------查找memory_bandwidth.sh

- find /usr/bin/ -name "*.sh"

- //------測(cè)試指令

- memory_bandwidth.sh

- //------腳本內(nèi)容

- #!/bin/bash

- for opt in rd wr rdwr cp frd fwr fcp bzero bcopy

- do

- echo "L1 cache bandwidth $opt test with #$proc process"

- #8k is fit for all platform

- for idx in `seq 1 5`

- do

- bw_mem -P 1 8k $opt

- done

- echo "L2 cache bandwidth $opt test"

- # For Layerscape platform, each platform has more than 256K L2 cache, so chose 128k as L2 cache size.

- for idx in `seq 1 5`

- do

- bw_mem -P 1 128k $opt

- done

- echo "Main mem bandwidth $opt test"

- for idx in `seq 1 5`

- do

- bw_mem -P 1 50m $opt

- done

- done

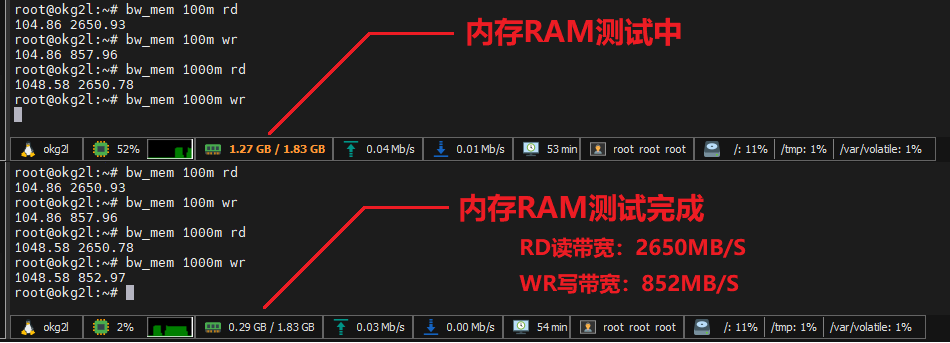

2.4 內(nèi)存帶寬測(cè)試-bw_mem

內(nèi)存帶寬測(cè)試-bw_mem工具可以對(duì)內(nèi)存RAM進(jìn)行指定容量讀寫(xiě)測(cè)試。

- //------測(cè)試工具(飛凌系統(tǒng)已帶)

- bw_mem

- //------測(cè)試指令(容量根據(jù)實(shí)際情況指定)

- bw_mem 100m rd

- bw_mem 100m wr

- bw_mem 1000m rd

- bw_mem 1000m wr

- //------測(cè)試結(jié)果

- RD讀帶寬:2650MB/S

- WR寫(xiě)帶寬:852MB/S

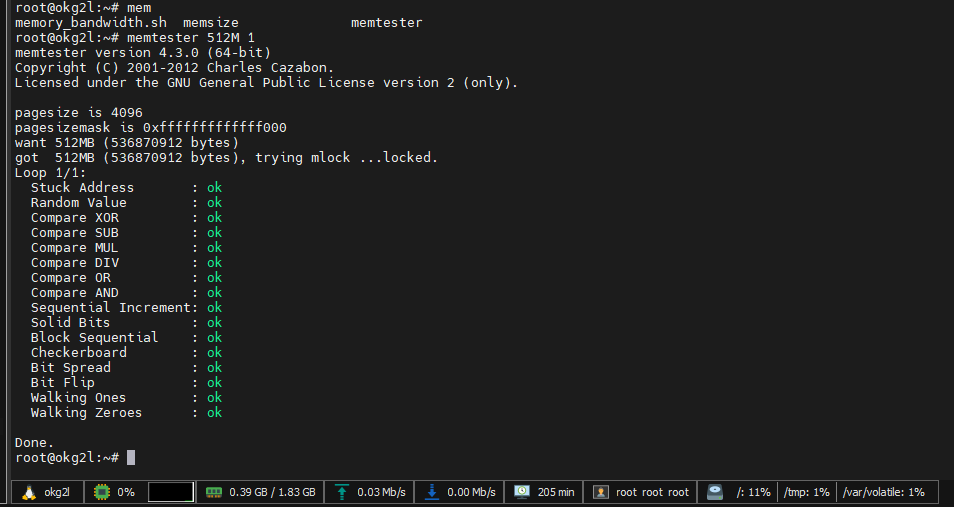

2.5 內(nèi)存功能壓力測(cè)試-memtester

內(nèi)存功能壓力測(cè)試-memtester

- //------測(cè)試工具(飛凌系統(tǒng)已帶)

- memtester

- //------測(cè)試指令

- memtester 512M 1

//------END

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

飛凌

+關(guān)注

關(guān)注

0文章

134瀏覽量

16171 -

開(kāi)發(fā)板試用

+關(guān)注

關(guān)注

3文章

301瀏覽量

2147

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

瑞薩電子RZ MPU家族精品RZ/N2L產(chǎn)品介紹

瑞薩生態(tài)合作伙伴RT-Thread推出了一款高性能、多功能以太網(wǎng)MPU開(kāi)發(fā)板EtherKit,搭載瑞薩電子RZ/N2L,并攜手瑞薩電子舉辦了產(chǎn)品發(fā)布會(huì)和產(chǎn)品研討。瑞薩電子在本次活動(dòng)中介

瑞薩電子RZ/N2L MPU產(chǎn)品介紹

瑞薩生態(tài)合作伙伴RT-Thread推出了一款高性能、多功能以太網(wǎng)MPU開(kāi)發(fā)板EtherKit,搭載瑞薩電子RZ/N2L,并攜手瑞薩電子舉辦了產(chǎn)品發(fā)布會(huì)和產(chǎn)品研討。瑞薩電子在本次活動(dòng)中介

飛凌嵌入式受邀亮相瑞薩2024工業(yè)技術(shù)研討會(huì)

飛凌嵌入式作為瑞薩電子的生態(tài)合作伙伴,給2024瑞薩電子MCU/MPU工業(yè)技術(shù)研討會(huì)的現(xiàn)場(chǎng)觀眾帶去了基于RZ/G2L高性能多核異構(gòu)處理器設(shè)計(jì)

瑞薩RZ/G2L微處理器的SD卡GPIO控制功能介紹

RZ/G2L微處理器配備Cortex-A55(1.2 GHz) CPU、16位DDR3L/DDR4接口、帶Arm Mali-G31的3D圖形加速引擎以及視頻編解碼器(H.264)。此外

RZ/G2L高速虛擬串口方案 基于瑞薩RZ/G2L SMARC開(kāi)發(fā)板的虛擬(Virtual UART)實(shí)現(xiàn)方案

RZ/G2L具有豐富的外設(shè),比如千兆以太網(wǎng),CANFD以及豐富的UART接口,可以滿(mǎn)足工業(yè)數(shù)據(jù)收集處理相關(guān)的應(yīng)用。本文主要介紹基于瑞薩RZ/G2L SMARC

發(fā)表于 11-20 14:41

?572次閱讀

有獎(jiǎng)試用!!RA-Eco-RA4E2-64PIN-V1.0開(kāi)發(fā)板試用活動(dòng)開(kāi)始報(bào)名

有獎(jiǎng)試用!!RA-Eco-RA4E2-64PIN-V1.0開(kāi)發(fā)板試用活動(dòng)開(kāi)始報(bào)名

RZ/T2M, RZ/T2L, RZ/N2L電機(jī)解決方案套件數(shù)據(jù)手冊(cè)

電子發(fā)燒友網(wǎng)站提供《RZ/T2M, RZ/T2L, RZ/N2L電機(jī)解決方案套件數(shù)據(jù)手冊(cè).rar

發(fā)表于 05-13 18:12

?5次下載

瑞薩教你如何使用RZ/T2L RZ/N2L RSK J-Link OB

? 瑞薩RZ/T2L MPU RZ/T2L是一款高性能MPU,可通過(guò)EtherCAT實(shí)現(xiàn)高速、高精度的實(shí)時(shí)控制。

RZ/G2L Demo調(diào)試經(jīng)驗(yàn)流程分享(1)

r01us0553ej0107-rz-g(Release Note).pdf,r01us0556ej0102-rz-g(Board_StartUp_Guide_smarcEVK).pdf,對(duì)SMARC EVK of RZ/

RZ/G2L SD卡啟動(dòng)環(huán)境變量存儲(chǔ)設(shè)置

RZ/G2L微處理器配備Cortex-A55(1.2 GHz)CPU、16位DDR3L/DDR4接口、帶Arm Mali-G31的3D圖形加速引擎以及視頻編解碼器(H.264)。

瑞薩RZ/V2L預(yù)訓(xùn)練的人工智能模型

RZ/V2L還與RZ/G2L封裝和引腳兼容。這使得RZ/G2L用戶(hù)可輕松升級(jí)至

發(fā)表于 03-21 13:51

?455次閱讀

【米爾-瑞薩RZ/G2UL開(kāi)發(fā)板】3.雜項(xiàng)測(cè)試

【米爾-瑞薩RZ/G2UL開(kāi)發(fā)板】3.雜項(xiàng)測(cè)試

不知道為啥我這板子好多奇奇怪怪的調(diào)試信息蹦出來(lái),臨時(shí)抑制辦法

echo 1 4 1 7 > /proc/sys/kernel

發(fā)表于 02-28 15:25

RZ/G2L微處理器DDR ECC功能和機(jī)制概要

RZ/G2L微處理器配備Cortex?-A55 (1.2 GHz) CPU、16位DDR3L/DDR4接口、帶Arm Mali-G31的3D圖形加速引擎以及視頻編解碼器(H.264)。

【飛凌RZ/G2L開(kāi)發(fā)板試用體驗(yàn)】+05.RZ/V2L開(kāi)發(fā)板的性能讀寫(xiě)測(cè)試(zmj)

【飛凌RZ/G2L開(kāi)發(fā)板試用體驗(yàn)】+05.RZ/V2L開(kāi)發(fā)板的性能讀寫(xiě)測(cè)試(zmj)

評(píng)論