目錄

JESD204協議標準的分類和區別:

JESD204A

JESD204B

JESD204B的各層規范

由于高速ADC的迅速發展,傳輸速率已經邁入GSPS,因此JESD204B標準協議將會成為應用范圍最廣的接口傳輸協議。

JESD204協議標準的分類和區別:

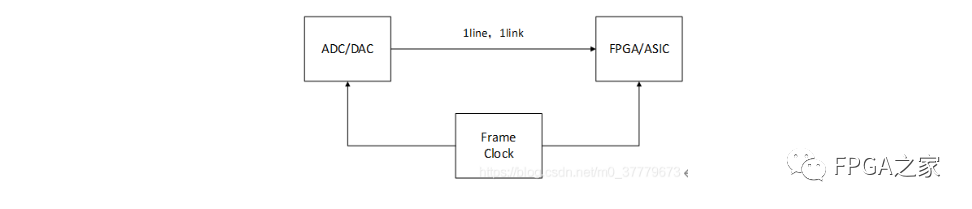

第一版JESD204標準協議問世于2006年4月,由JEDEC國際協會發布。其中,ADC或DAC為數據轉換器,ASIC或FPGA為接收機。

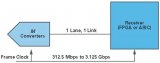

由于當時對轉換器速率和分辨率的要求不高,所以最初的JESD204B標準只考慮了一個通道和一個鏈路,傳輸速率可達到3.125Gbps。發送端與接收端則共用一個系統時鐘。其傳輸結構如下圖所示:

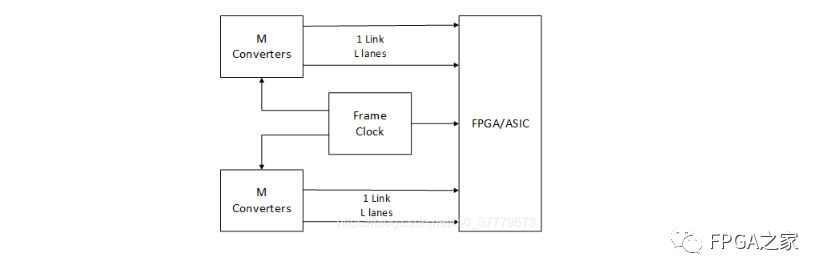

JESD204A

第一個修訂版本JESD204A標準于2018年4月發布。相較于JESD204標準最顯著的更新為該版本支持多鏈路和多通道串行數據傳輸。除此之外,該版本新添加了轉換器的多重對準能力,而最高傳輸速率達到了3.125Gbps,大大提高了轉換器的采樣率和分辨率。其傳輸結構如下圖所示:

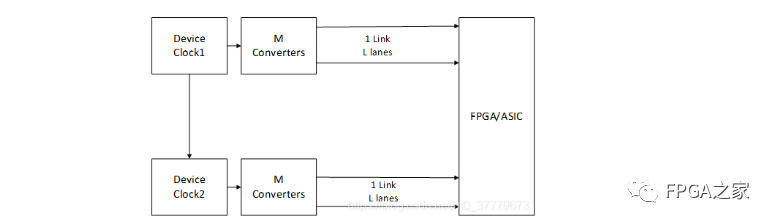

JESD204B

JESD204B標準在2011年8月于JESDEC公司發布。該標準可支持單個轉換器的內部同步和多個轉換器之間的同步,數據傳輸速率可達到12.5Gbps。且速率可分為不同的等級。相較于之前的版本,JESD204B沒有單一的時鐘源,既可以使用器件內部時鐘也可以外接時鐘。其中JESD204B還提供了三種不同的傳輸模式,即子類0,子類1,子類2。子類1,可以支持確定的延時。其傳輸結構如下圖所示:

經過兩次較大的修訂,JESD204標準協議越來越完善,其性能不斷提高,可以基本滿足現今高速轉換器的要求。所以,JESD204B標準有望成為事實應用中未來轉換器的協議標準。

JESD204B的各層規范

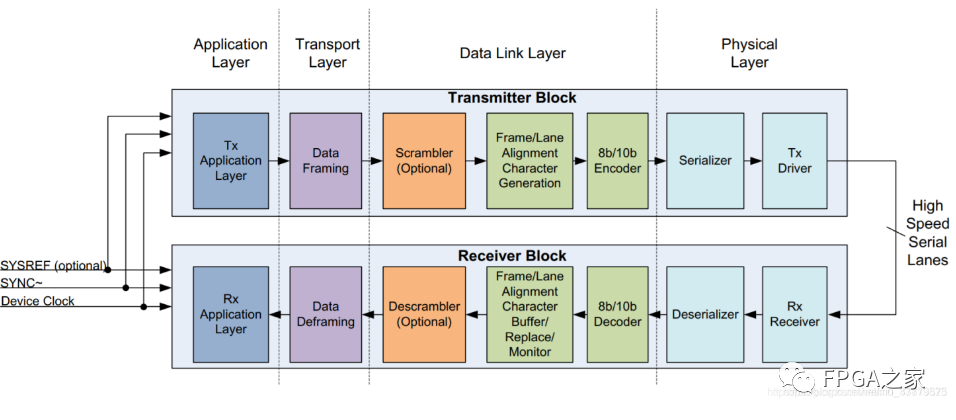

JESD204B標準協議具有四層結構,分別為應用層,傳輸層數據鏈路層,物理層。

應用層:

應用層的功能實完成傳輸通道的配置和數據映射轉換。與別的傳輸協議不同的是,設計人員必須以相同的配置方式來配置發送機和接收機,以便正確傳輸和解析數據。

傳輸層:

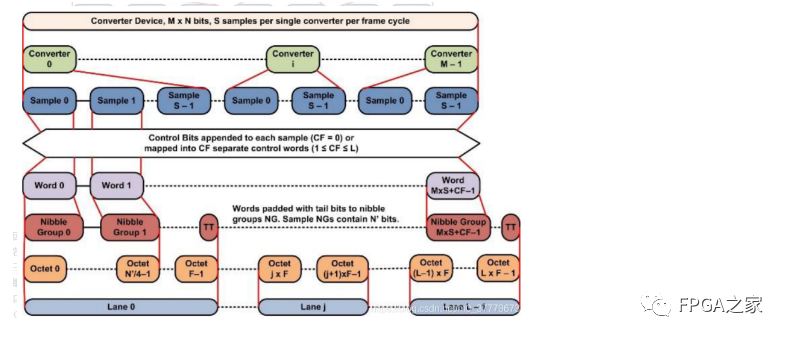

傳輸層的功能是實現數據樣本與字符幀之間的映射。傳輸層將這些映射后的數據進行組幀。在傳輸層內,仍是并行數據形式,而不是所認為的串行數據形式。將這些并行數據發送到數傳輸通道路。并行數據的寬度由組幀后的結構決定,單字節為8位,雙字節為16位,以此類推。

數據鏈路層:

數據鏈路層實現接收并行的組幀數據的組幀,組幀后數據包含原始數據樣本、控制字符和冗余字符。在數據鏈路層內將數據采用8B/10B編碼。數據鏈路層通過鏈路建立過程同步JESD204B鏈路。

鏈路同步過程分為三大階段:代碼組同步(CGS)、初始化通道同步(ILAS)和數據傳輸階段。

鏈路需要以下信號:共享參考時鐘(一般為FPGA內部時鐘),一個或多個CML物理數據傳輸通道,以及一個或多個同步信號(例如SYNC信號)。使用不同的子類取決要使用的信號:

子類0:采用設備時鐘,物理數據通道和同步信號SYNC~

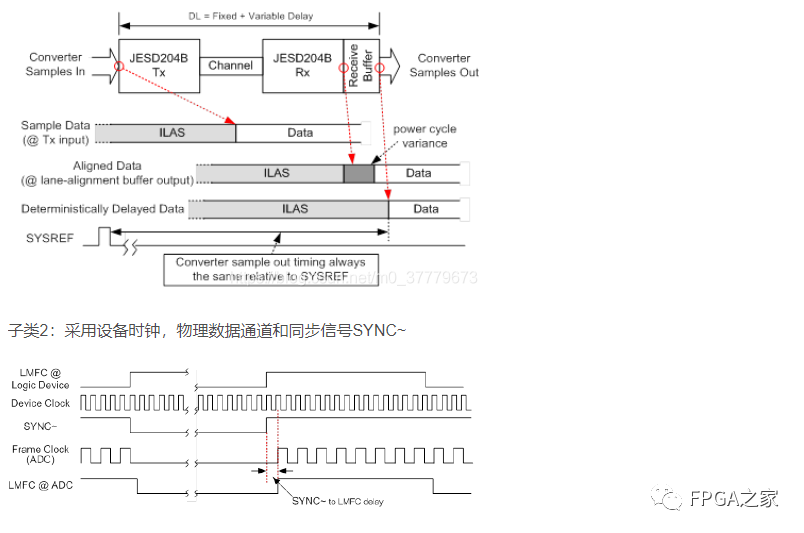

子類1:采用設備時鐘,物理數據通道,同步信號SYNC~和SYSREF

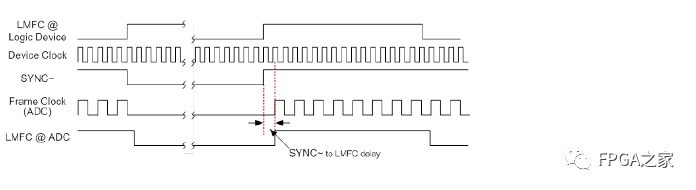

子類2:采用設備時鐘,物理數據通道和同步信號SYNC~

1、代碼組同步(CGS)階段

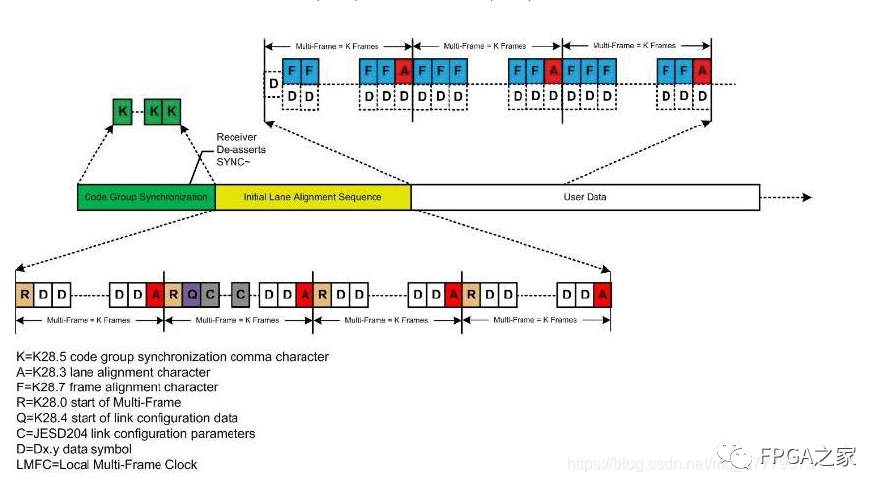

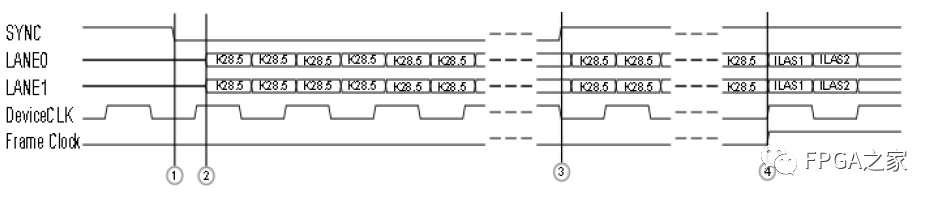

在同步鏈路中,代碼組同步(CGS)階段是最核心的部分,可由下圖所展現。下面對五個特殊點進行說明。

初試階段,接收機Rx將SYNC信號拉低(置0),同時發出一個同步請求。

發送機Tx接收到同步請求后,在下一個時鐘周期內,發送連續的/K28.5/符號(每個符號10位)。

當接收機Rx接收到至少4個無錯誤且連續/K28.5/符號時,然后將SYNC信號拉高(置1)。

如果接收機Rx沒有完成(3)的所有過程,則代表代碼組同步將失敗,鏈路仍然留在CGS階段。接收機Rx繼續發送同步請求。

CGS階段結束, ILAS階段開始。

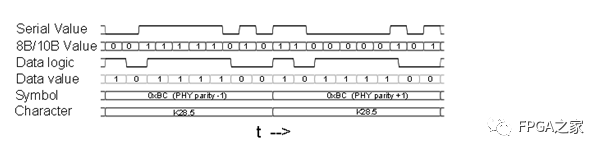

/K28.5/在FPGA仿真中體現為BC碼。當出現連續四個無錯誤BC時,Rx同步,并將SYNC信號拉高。下圖為/K28.5/字符的邏輯輸出。

2、初始通道的同步階段(ILAS)

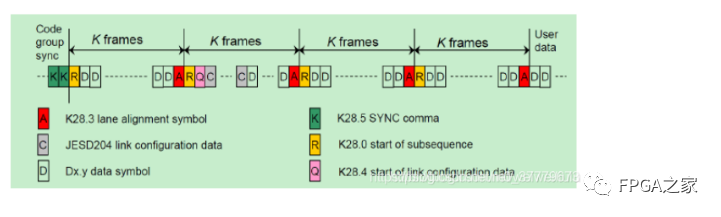

初始通道同步階段(ILAS)階段的作用是允許接收機Rx對齊來自各個鏈路的通道,以及驗證鏈路參數是否配置正確。為了解決走線的長度不同以及傳輸過程中出現的字符偏斜,通道必須對齊。在實際應用中,不論配置IP核時是否啟用加擾功能 ,初試通道同步階段始終是無加擾傳輸。當SYNC信號由低電平0跳變為高電平1時,便進入ILAS階段。當發送機內的檢測模塊接收一個完整多幀后,便開始連續發送4個數據多幀。在所需的字符中插入冗余字符,以便傳送完整的多幀,如下圖所示。

4個多幀包括:

(1)多幀1:以/R/字符[K28.0]開始,以/A/字符[K28.3]結束。

(2)多幀2:以/R/字符開始,后接/Q/ [K28.4]字符,然后是14個配置8位字的鏈路配置參數,最后以/A/字符結束。

(3)多幀3:與多幀1相同。

(4)多幀4:與多幀1相同。

3、數據傳輸階段(Data)

在數據傳輸階段,通過預先插入的控制字符來判斷幀是否對齊。如果在數據傳輸階段,數據或幀沒有很好的對齊,會造成大量額外資源消耗。為了解決這個問題,JESD204B在幀的結尾處會采用字符替換。字符替換只能發在每幀的末尾,接收機通過發送對齊字符信號。字符替換有著嚴格的要求,必須是當前字符幀的最后一個字符與上一幀的最后一個字符相同時,才可以發生。這有利于判斷經過ILAS序列后,對齊是否未改變。

出現下列情況時,會對發送器執行字符替換:

? 若不使用加擾功能,并且字符幀的最后8位字與上一字幀的最后8位字一致。

? 若使用了加擾功能,并且多幀的最后一個8位字等于0x7C,或幀的最后一個8位字等于0xFC。

JESD204B的接收期間內,存在著一個多幀計數器(LMFC),它持續計數到規定的值時,會置0重新開始計數。此時發送一個公共信號SYSREF到所有發送機和接收機,這些接收機和發送機器收到SYSREF信號時復位其LMFC,這樣使得在一個時間時鐘周期內所有LMFC同時置0。并將SYNC信號由高電平拉低為低電平(所有Tx與Rx器件都能接收到SYNC被拉低看到)后,發送器在下一次LMFC重新置0時開始ILAS階段。

如果參數設置正確且計數時間大于(發送機發送時間)+(通道傳輸時間)+(接收機接收時間),則接收機將在下一個LMFC之前從接收機的SerDes進行傳輸。接收器將數據發送到FIFO,然后在下一個計數器LMFC邊界時刻輸出數據。

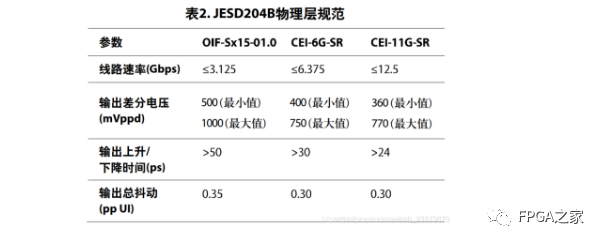

物理層:

物理層中對接收到的數據進行并串轉換,對數據鏈路層所輸出8B/10B編碼數據以高速率發送和接收。(8B/10B編解碼原理及實現:https://blog.csdn.net/m0_37779673/article/details/118464343)物理層包括發送模塊,并串轉換模塊、內部時鐘同步模塊和接收模塊。由于其數據的高速傳輸,各個模塊常常采用單元設計。

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605984 -

轉換器

+關注

關注

27文章

8743瀏覽量

148031 -

接口

+關注

關注

33文章

8691瀏覽量

151911 -

JESD204

+關注

關注

0文章

9瀏覽量

7946

原文標題:JESD204標準概述

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

請問AD9683的引腳如何與zynq 7015芯片中的 JESD204 ip核端口對應相連?

在Xilinx FPGA上快速實現JESD204B

JESD204 v5.2約束使用生成的dcp構建邏輯計時失敗

JESD204接口簡介

串行LVDS和JESD204B的對比

JESD204標準解析

JESD204評估許可證問題

為什么JESD204內核不使用GTX通道綁定功能來對齊通道?

JESD204C標準值得注意的新特性

AD9683的引腳如何與zynq 7015芯片中的JESD204 ip核端口對應相連?

FPGA通用接口JESD204轉換器接口標準詳解

采用JESD204標準的高速串行接口的應用

JESD204——它是什么?

虹科干貨 | 使用JESD204串行接口高速橋接模擬和數字世界

JESD204協議標準的分類和區別

JESD204協議標準的分類和區別

評論