在剛剛結(jié)束的GTIC 2022全球AI芯片峰會(huì)存算一體專題論壇上,億鑄科技創(chuàng)始人、董事長(zhǎng)兼CEO熊大鵬博士發(fā)表了題為“存算新動(dòng)能——基于ReRAM的全數(shù)字化實(shí)現(xiàn)”的演講,介紹了億鑄科技基于ReRAM的全數(shù)字化存算一體AI大算力芯片技術(shù)等深度內(nèi)容,以下為演講回顧。

AI芯片正在經(jīng)歷三個(gè)階段:第一個(gè)階段是通用CPU;第二個(gè)階段是專用的加速芯片,其中比較有代表性的是GPU或者基于dataflow數(shù)據(jù)流、TPU這種以脈動(dòng)陣列的方式對(duì)AI進(jìn)行加速的芯片;而現(xiàn)在我們正在進(jìn)入第三個(gè)階段——存算一體芯片。從第一個(gè)階段到第二個(gè)階段的主要驅(qū)動(dòng)力是計(jì)算工藝的提升,以加大計(jì)算能力;而第二個(gè)階段到第三個(gè)階段的轉(zhuǎn)換我們認(rèn)為主要是存儲(chǔ)墻所導(dǎo)致的,大量的數(shù)據(jù)搬運(yùn)帶來的瓶頸使能耗增加、計(jì)算效率大大下降。

就像我們?cè)谏钲谂e行峰會(huì),大家來自不同城市地區(qū),從各自居住的地方乘坐各種交通工具來到會(huì)場(chǎng),在行程住宿上花費(fèi)的時(shí)間金錢精力遠(yuǎn)遠(yuǎn)超過了在會(huì)議本身上付出的成本。從某種意義上來說,這就類似于存算分離——居住的地方和會(huì)場(chǎng)是分開的。想象一下,如果大家都用網(wǎng)絡(luò)視頻參加本次峰會(huì),時(shí)間金錢精力等成本就會(huì)大幅度降低,從這個(gè)角度來看,視頻會(huì)議就像是存算一體——工作的地方就是居住的地方,居住的地方也是工作的地方。同樣,由于存算分離,AI計(jì)算的數(shù)據(jù)搬運(yùn)量非常大,會(huì)導(dǎo)致功耗大大增加,這就是存儲(chǔ)墻。

此外,不管是傳輸還是計(jì)算工藝本身的限制,能效比已經(jīng)接近極限。無論是20W,75W,150W的模組還是PCIe板卡,目前能支持的最高算力已經(jīng)達(dá)到了天花板。以75W為例,不管是7nm工藝或?qū)頃?huì)有的更高工藝,150TOPS到200TOPS已經(jīng)基本封頂,這是存儲(chǔ)墻帶來的能耗墻導(dǎo)致的。

第三個(gè)問題我們稱為編譯墻或是生態(tài)墻,也可以說是可編程性,由于存算分離,數(shù)據(jù)搬運(yùn)容易發(fā)生擁塞,尤其是在動(dòng)態(tài)環(huán)境下,對(duì)數(shù)據(jù)進(jìn)行調(diào)度和管理其實(shí)非常復(fù)雜,所以編譯器無法在靜態(tài)可預(yù)測(cè)的情況下對(duì)算子、函數(shù)、程序或者網(wǎng)絡(luò)做整體的優(yōu)化,只能手動(dòng)、一個(gè)個(gè)或者一層層對(duì)程序進(jìn)行優(yōu)化,包括層與層之間的適配等,耗費(fèi)了大量時(shí)間。傳統(tǒng)架構(gòu)的AI對(duì)像ResNet-50這種軟件做優(yōu)化通常需要幾十個(gè)人花費(fèi)幾個(gè)月的時(shí)間,這就是存儲(chǔ)墻帶來的編譯墻。

而存算一體架構(gòu)可以打破傳統(tǒng)的馮·諾依曼架構(gòu)帶來的這“三堵墻”。

硬件加速的基本定律叫做阿姆達(dá)爾定律,如同力學(xué)里面的牛頓定律。在這個(gè)公式中,大家可以看到一個(gè)F和一個(gè)α,F(xiàn)是計(jì)算所花的時(shí)間除以數(shù)據(jù)搬運(yùn)加上計(jì)算時(shí)間的百分比,α取決于算力的堆疊或者工藝提升之后工作頻率的提升。計(jì)算速度每年大概會(huì)提升40%,但是數(shù)據(jù)搬運(yùn)的速度大概每年提高不到10%,使得兩者之間的鴻溝越來越大,這個(gè)比例未來可能會(huì)小于0.8、0.5甚至更低。如果以F為0.5為例,以后無論使用多先進(jìn)的工藝,性能的提升都不會(huì)超過兩倍這個(gè)天花板,這也就解釋了為什么基于馮·諾依曼架構(gòu)AI芯片算力密度的天花板是不可避免的。

那么存算一體又為什么能突破天花板,達(dá)成線性上升呢?因?yàn)檫@里的F值約等于1,緩存數(shù)據(jù)搬運(yùn)的時(shí)間非常小,基本上可以忽略不計(jì),1-F接近0,這個(gè)公式在存算一體架構(gòu)下,硬件加速和α呈線性關(guān)系,核數(shù)堆得越多或者工藝越先進(jìn),硬件加速的倍數(shù)就越高。這個(gè)公式就從理論上解釋了存算一體可以打破傳統(tǒng)馮·諾依曼架構(gòu)算力密度、能效比等限制的天生優(yōu)勢(shì)。

就像其他演講者提到的,用純模擬的方式實(shí)現(xiàn)存算一體,會(huì)比傳統(tǒng)存算分離架構(gòu)下能效比提升幾十甚至上百倍。憶阻器W相當(dāng)于一個(gè)乘法器和加法器,在數(shù)字領(lǐng)域,做一個(gè)乘法器和加法器大概需要1700個(gè)晶體管左右,但在這里一個(gè)簡(jiǎn)單的憶阻器就可以代替乘法器和加法器,其系統(tǒng)設(shè)計(jì)的復(fù)雜性和功耗等將得到很大的優(yōu)化。

當(dāng)然,模擬的方式也有缺陷,比如精度問題和數(shù)模/模數(shù)轉(zhuǎn)換導(dǎo)致的天花板問題。憶阻器是個(gè)可編程電阻,所以會(huì)受到工藝和工作環(huán)境的影響,在這些影響下,精度就會(huì)有漂移。尤其對(duì)于大算力的AI應(yīng)用來說,精度期望往往是8位、16位,甚至更高。無論是人臉識(shí)別、自動(dòng)駕駛還是語(yǔ)音識(shí)別,都有可能要求16位的整數(shù)或者浮點(diǎn),而16位的精度誤差不能超過百萬分之一,從物理上來說,憶阻器無法達(dá)到這樣的精度。

另外一個(gè)問題是模擬需要數(shù)模/模數(shù)轉(zhuǎn)換,這個(gè)就帶來了性能、能耗和晶圓面積過大等方面的瓶頸。所以憶阻器有優(yōu)點(diǎn),也有一些需要克服的挑戰(zhàn)。要想解決這些問題,國(guó)內(nèi)國(guó)外企業(yè),包括我們自己,都嘗試過數(shù)模混合的方式。也就是一部分采用數(shù)字化,另一部分采用模擬的方式實(shí)現(xiàn)存算一體,因?yàn)槟M和數(shù)字化各有各的好處。

這里舉一個(gè)簡(jiǎn)單的例子。如果一個(gè)憶阻器表達(dá)8位或者16位的精度就會(huì)帶來精度問題,那么我們僅僅用這個(gè)憶阻器表達(dá)4位的精度,如果需要做8位的計(jì)算,就用兩個(gè)憶阻器來表達(dá),算完之后得到兩個(gè)結(jié)果:Y1(0)和Y1(1),通過外圍的邏輯組合來完成一個(gè)完整的8位乘加。這種方式的好處就是解決了部分精度問題,因?yàn)?位精度相對(duì)來說比較容易做到,而且數(shù)模/模數(shù)轉(zhuǎn)換對(duì)精度的要求不高。其不足在于不能絕對(duì)保證它的可靠性,而且數(shù)模/模數(shù)轉(zhuǎn)換在性能方面還有限制,計(jì)算過程相對(duì)復(fù)雜也導(dǎo)致了能效比下降。

而億鑄科技采用的是全數(shù)字化存算一體,全數(shù)字化存算一體的好處就在于不管是8位、16位還是32位,不管是整數(shù)還是浮點(diǎn),在整個(gè)計(jì)算過程中不受到工藝和工作環(huán)境的影響,沒有精度損失,也沒有數(shù)模/模數(shù)轉(zhuǎn)換導(dǎo)致的性能低、能效比低或者晶圓面積過大等問題。能效比可以超過20TOPS/Watt,如果是在75Watt 的PCIe加速卡上做性能可以超過1POPS(1000TOPS),相對(duì)于當(dāng)前主流的算力產(chǎn)品而言,我們用28nm工藝實(shí)現(xiàn)8-10倍能效比。

億鑄科技將存算一體作為一個(gè)IP,整體設(shè)計(jì)還包括CPU、SIMD、對(duì)外接口、ISP、Video Codec、NoC片內(nèi)通訊等等,組成了一個(gè)比較完整的芯片。相比當(dāng)前主流的算力產(chǎn)品,在同樣的功耗下,能效比可以達(dá)到8-10倍的提升。另外作為整體解決方案,因?yàn)槲覀冊(cè)贏I的部分不需要外接的高性能DDR,更不需要HBM/GDDR,所以成本大概只有目前主流板卡的1/3-1/6。

說到軟件和軟件生態(tài),圖中左邊這部分對(duì)于所有開發(fā)者來說都是公開的,下面是傳統(tǒng)架構(gòu)的AI芯片,右邊和傳統(tǒng)不同的是有后端編譯優(yōu)化器。存算一體有天生優(yōu)勢(shì),軟件開發(fā)難度相對(duì)較低,并且編譯器可以自動(dòng)優(yōu)化,避免了每個(gè)算子、每個(gè)函數(shù)、每層的手動(dòng)優(yōu)化的過程。

比如,要把整個(gè)網(wǎng)絡(luò)ResNet-50映射到ReRAM陣列里,為了對(duì)資源進(jìn)行合理地優(yōu)化分配,在靜態(tài)的情況下采用非線性動(dòng)態(tài)優(yōu)化的策略,設(shè)定從frame進(jìn)去到出來處理的整體時(shí)長(zhǎng)最短為優(yōu)化目標(biāo)。它帶來的好處非常明顯——在算子庫(kù)和函數(shù)庫(kù)里有一些基本的素材,依賴編譯器提供的工具來自動(dòng)優(yōu)化執(zhí)行程序,可以指數(shù)級(jí)地減少程序開發(fā)員的工作。另外一個(gè)好處是,芯片落地后,終端用戶部署所花費(fèi)的時(shí)間、人力、物力成本也將大大減少。

最后介紹一下億鑄科技對(duì)存儲(chǔ)介質(zhì)選擇的考量。存算一體有不同的介質(zhì)選擇:有傳統(tǒng)存儲(chǔ)器Flash、SRAM,也有新型存儲(chǔ)器ReRAM、PCRAM、MRAM等等。在不同的應(yīng)用環(huán)境下,每個(gè)介質(zhì)都有自身的優(yōu)缺點(diǎn),但對(duì)于AI大算力這個(gè)特殊的細(xì)分領(lǐng)域來說,從成本、密度、功耗、性能穩(wěn)定性等各方面綜合考慮,我們選擇了ReRAM,也認(rèn)為ReRAM是目前最適合存算一體AI大算力的存儲(chǔ)介質(zhì)。

另外ReRAM還有很多其他優(yōu)勢(shì),比如億鑄選擇的憶阻器高阻值和低阻值之間的平均差異能夠達(dá)到一千倍以上,帶來了穩(wěn)定可靠的優(yōu)勢(shì),也使電路設(shè)計(jì)更加簡(jiǎn)單。另外,ReRAM可以兼容CMOS常規(guī)的工藝。

2021年被稱為ReRAM的元年,從去年開始ReRAM已經(jīng)商用落地、規(guī)模量產(chǎn),未來的成長(zhǎng)空間非常大。比如ReRAM可以往密度、性能兩方面快速發(fā)展。從密度來說,一個(gè)是MLC多模態(tài)形式,另一個(gè)是可以往上3D堆疊,所以從迭代的潛力來看ReRAM也有十分獨(dú)特的優(yōu)勢(shì)。

目前在28nm的工藝上,昕原半導(dǎo)體在去年已經(jīng)開始量產(chǎn)ReRAM,TSMC也開始可以提供量產(chǎn)的能力,二者良率都在90%以上。低端工藝上也有其他廠家可以支持,例如采用Panasonic技術(shù)的UMC。

今天是存算一體專場(chǎng),億鑄科技希望能夠和上下游伙伴們攜手打造存算一體生態(tài),制定中國(guó)自己的標(biāo)準(zhǔn),無論是指令集、SDK、還是開發(fā)工具等,打造我們中國(guó)自己的生態(tài)。我們相信,在存算一體這個(gè)領(lǐng)域上,中國(guó)和其他國(guó)家之間的技術(shù)差距非常小,甚至在某些方面還領(lǐng)先于世界。我們相信,只要大家齊心合力一起打造存算一體生態(tài),一定能迎來非常光明的未來。

-

gpu

+關(guān)注

關(guān)注

28文章

4774瀏覽量

129353 -

芯片技術(shù)

+關(guān)注

關(guān)注

1文章

161瀏覽量

17594 -

AI

+關(guān)注

關(guān)注

87文章

31513瀏覽量

270330 -

數(shù)字化

+關(guān)注

關(guān)注

8文章

8849瀏覽量

62164

原文標(biāo)題:億科技 | 存算一體新動(dòng)能——基于ReRAM的全數(shù)字化技術(shù)

文章出處:【微信號(hào):億鑄科技,微信公眾號(hào):億鑄科技】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

存算一體行業(yè)2024年回顧與2025年展望

億鑄科技榮登2024創(chuàng)業(yè)邦100未來獨(dú)角獸榜單

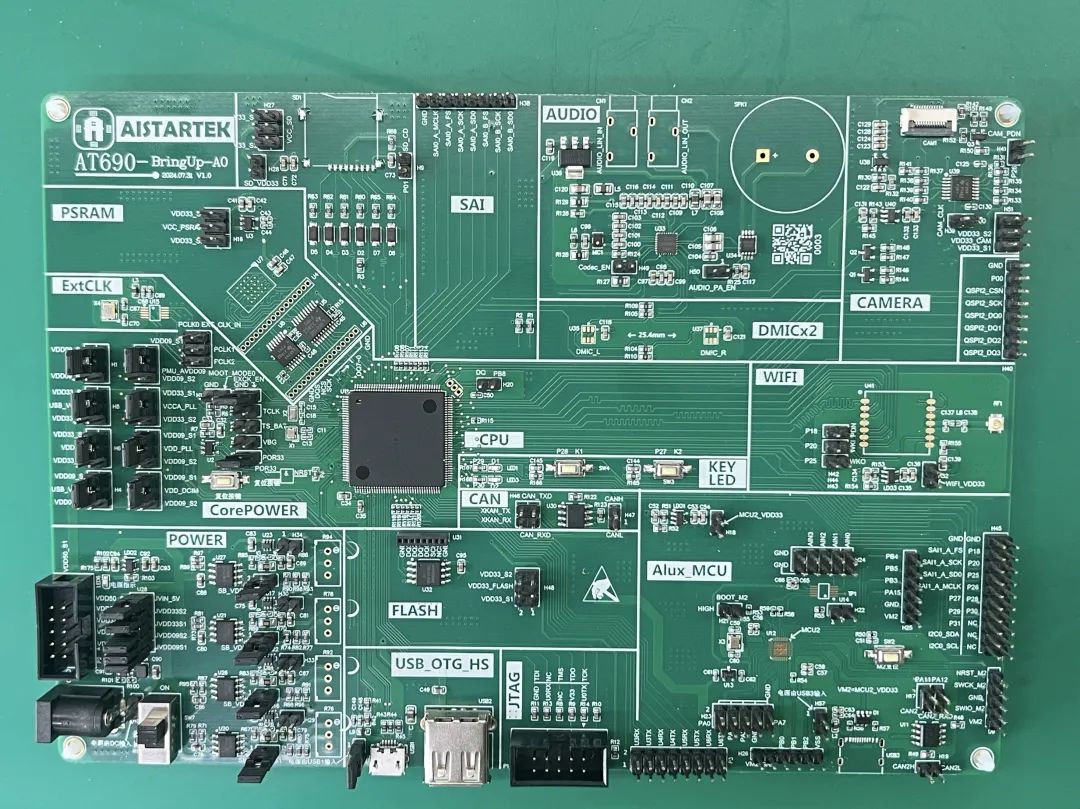

存算于芯 · 智啟未來 — 2024蘋芯科技產(chǎn)品發(fā)布會(huì)盛大召開

億鑄科技入選畢馬威中國(guó)“芯科技”新銳企業(yè)50強(qiáng)

存算一體化與邊緣計(jì)算:重新定義智能計(jì)算的未來

億鑄科技熊大鵬探討AI大算力芯片的挑戰(zhàn)與解決策略

存算一體架構(gòu)創(chuàng)新助力國(guó)產(chǎn)大算力AI芯片騰飛

科技新突破:首款支持多模態(tài)存算一體AI芯片成功問世

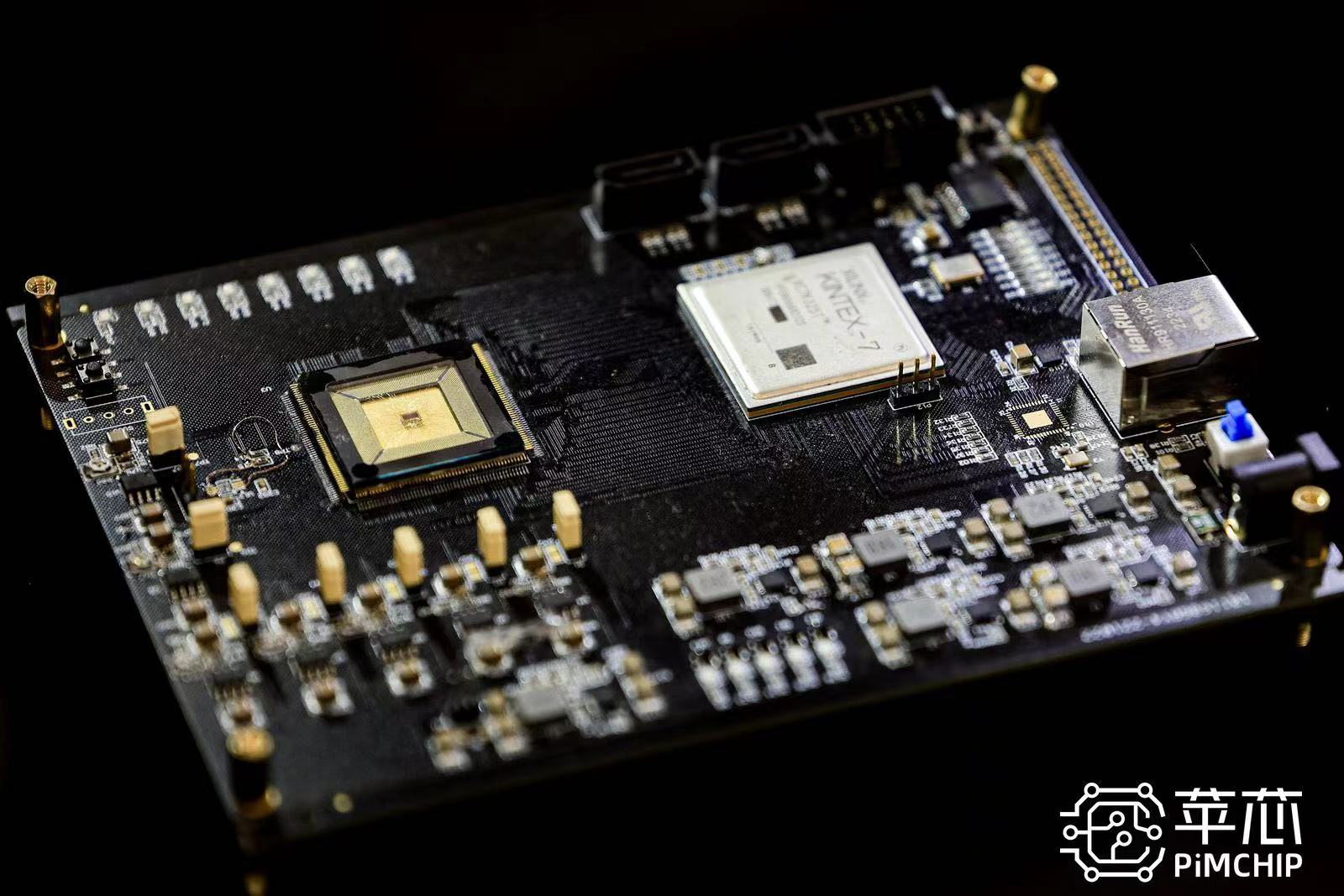

蘋芯科技引領(lǐng)存算一體技術(shù)革新 PIMCHIP系列芯片重塑AI計(jì)算新格局

存算一體AI芯片企業(yè)后摩智能完成數(shù)億元戰(zhàn)略融資

后摩智能推出邊端大模型AI芯片M30,展現(xiàn)出存算一體架構(gòu)優(yōu)勢(shì)

知存科技助力AI應(yīng)用落地:WTMDK2101-ZT1評(píng)估板實(shí)地評(píng)測(cè)與性能揭秘

探索存內(nèi)計(jì)算—基于 SRAM 的存內(nèi)計(jì)算與基于 MRAM 的存算一體的探究

知存科技攜手北大共建存算一體化技術(shù)實(shí)驗(yàn)室,推動(dòng)AI創(chuàng)新

聚焦全國(guó)一體化算力體系構(gòu)建,憶聯(lián)以強(qiáng)大存力“引擎”釋放算力潛能

億鑄科技發(fā)布基于ReRAM的全數(shù)字化存算一體AI大算力芯片技術(shù)

億鑄科技發(fā)布基于ReRAM的全數(shù)字化存算一體AI大算力芯片技術(shù)

評(píng)論