系統總線(System Bus)是系統芯片中各個設備(如嵌入式處理器,存儲器和外設等IP核)之間通信與互連的公共硬件通道,其為設備間訪問共享硬件提供了一種互連機制,在數字系統中承擔數據傳輸的任務。

系統總線連接的設備根據功能的不同分為主設備和從設備。主設備指可以主動發起傳輸任務的設備。例如,處理器可以通過總線控制外設,讀/寫數據;一些外設也可以通過總線訪問其他外設,讀/寫數據。從設備是響應主設備發起的傳輸任務的設備。例如,存儲器響應主設備的讀操作,返回讀數據。此外,一些設備既可以作為主設備主動對總線發起訪問,又可以作為從設備被動響應總線事務。

系統芯片中,通常設計多個主設備和多個從設備。不同的從設備在總線上對應著互不重疊的地址區間,總線通過主設備發起傳輸任務的目標地址。不同總線協議會設計不同的主設備訪問方式。例如:AMBA 2.0協議中規定,同一條AHB(Advanced High Perfoormance Bus)總線上的設備共享固定的地址數據傳輸通道,這意味著其中一個主設備占用AHB總線后其余主設備均處于等待狀態;而AMBA 3.0協議中的AXI總線則使用不同的ID號來區分主設備,主設備可以在其他主設備的訪問未完成的情況下繼續發起請求。

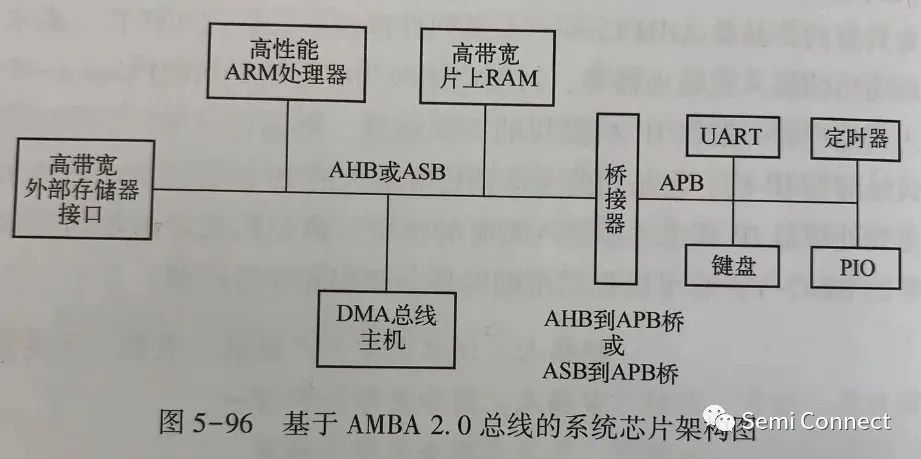

一個基于AMBA 2.0總線的系統芯片架構如圖5-96所示。AHB總線連接嵌入式處理器和存儲器等高速設備,APB總線連接串口,定時器等低速設備。總線仲裁機制包括輪詢機制和優先級機制。總線在傳輸數據時,可以采用不同的傳輸類型以適應不同長度和速度的傳輸需求。高性能ARM處理器是系統的主設備,它可以通過AHB總線訪問高帶寬的外部存儲器接口和高帶寬片上RAM,也可以通過橋接器訪問APB總線上的低速設備UART,鍵盤,定時器和PIO等。

根據工作頻率的不同,總線被設計為高速總線和低速總線:高速總線支持較高的時鐘頻率,擁有較高的數據帶寬和性能,但功耗也較高,一般適用于CPU和DMA等高速設備的連接;低速總線工作頻率較低,雖然性能較差,但功耗較低,適合掛載鍵盤,串口等低速外設。高速總線和低速總線之間可以用過橋進行連接通信。目前,業界系統芯片中較有影響力的總線包括AMBA總線,CoreConnect總線,Wishbone總線和OCP總線等。

審核編輯 :李倩

-

存儲器

+關注

關注

38文章

7528瀏覽量

164344 -

總線

+關注

關注

10文章

2903瀏覽量

88393 -

系統芯片

+關注

關注

0文章

38瀏覽量

18389

原文標題:系統芯片設計—系統總線

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

系統芯片設計—系統總線(System Bus)

系統芯片設計—系統總線(System Bus)

評論