芯片產(chǎn)業(yè)在不斷競(jìng)速,作為AI產(chǎn)業(yè)落地重要基底的AI芯片更是如此。在持續(xù)火熱多年后,如今我國(guó)AI芯片產(chǎn)業(yè)已經(jīng)朝著肉搏階段邁進(jìn),誰(shuí)率先落地產(chǎn)品、構(gòu)建生態(tài),誰(shuí)就能在這場(chǎng)競(jìng)爭(zhēng)中突圍。

激烈的市場(chǎng)競(jìng)爭(zhēng)與迫切的Time to Market,讓人們對(duì)芯片設(shè)計(jì)的“好與快”提出了更高要求,在新一輪挑戰(zhàn)面前,如何整合EDA、IP與設(shè)計(jì)資源,讓AI芯片快人一步?

相輔相成的EDA

EDA全稱Electronic design automation,主要為集成電路的設(shè)計(jì)、生產(chǎn)等提供自動(dòng)化輔助設(shè)計(jì)能力。憑借精細(xì)的軟件設(shè)計(jì),EDA保證了芯片設(shè)計(jì)各個(gè)階段、各個(gè)環(huán)節(jié)的準(zhǔn)確性,縮短了設(shè)計(jì)周期、降低了設(shè)計(jì)成本,因此被人稱之為半導(dǎo)體工業(yè)軟件皇冠上的明珠。

然而人工智能的興起,卻將EDA推向了新浪潮。無(wú)論是在EDA工具中應(yīng)用AI算法賦能芯片設(shè)計(jì)的“AI Inside”,還是EDA工具助力AI芯片高效設(shè)計(jì)的“AI Outside”,都意味著EDA對(duì)于提高AI芯片設(shè)計(jì)效率有著不可或缺的重要作用。

在“AI Outside”方面,AI芯片隨著數(shù)據(jù)爆炸時(shí)代的到來(lái)應(yīng)運(yùn)而生,龐大的算力意味著其往往具備超大的設(shè)計(jì)規(guī)模,對(duì)于芯片來(lái)說(shuō),規(guī)模越大,結(jié)構(gòu)越復(fù)雜、精度越高,對(duì)于EDA軟件的依賴程度也就越高。

以在EDA總體算力比重較大的驗(yàn)證來(lái)說(shuō),作為解鎖芯片流片成敗的關(guān)鍵環(huán)節(jié)之一,要想提高流片成功率,就要在流片之前做好充分的系統(tǒng)級(jí)驗(yàn)證。一般來(lái)說(shuō),芯片驗(yàn)證工作隨著SoC芯片復(fù)雜度、集成度規(guī)模的擴(kuò)大,占比不斷提高,甚至可達(dá)70%。面對(duì)復(fù)雜的設(shè)計(jì)需求,傳統(tǒng)基于電路的仿真技術(shù)無(wú)法實(shí)現(xiàn)對(duì)極端情況的驗(yàn)證覆蓋,使得驗(yàn)證覆蓋率的收斂成為了阻礙AI芯片設(shè)計(jì)效率進(jìn)一步提升的“絆腳石”。

為此,AI芯片在驗(yàn)證策略選擇上往往需要引入多種驗(yàn)證手段,通過(guò)仿真、形式化驗(yàn)證、FPGA原型驗(yàn)證等一系列驗(yàn)證手段提前發(fā)現(xiàn)問(wèn)題,確保芯片在功能、功耗、調(diào)度性能等方面達(dá)到設(shè)計(jì)期望。使用EDA工具,可以針對(duì)AI的分布式、矩陣式等運(yùn)算特點(diǎn),驗(yàn)證AI芯片的性能和收斂能力,推出對(duì)應(yīng)的解決方案,以此來(lái)得到更快的結(jié)果,提高芯片設(shè)計(jì)效率。

圖源:芯華章

這也是EDA的優(yōu)勢(shì)所在,無(wú)論是人工智能,還是云計(jì)算、5G、智能汽車,EDA領(lǐng)域均有對(duì)應(yīng)其應(yīng)用特點(diǎn)的芯片設(shè)計(jì)解決方案,對(duì)于芯片設(shè)計(jì)者而言,EDA工具可以快速將基礎(chǔ)信息進(jìn)行有效的建模和抽象,幫助設(shè)計(jì)者將精力更多地投入上層和系統(tǒng)設(shè)計(jì)。設(shè)計(jì)者只需完善算法設(shè)計(jì),即可通過(guò)EDA實(shí)現(xiàn)一個(gè)性價(jià)比更高、性能更匹配的系統(tǒng)設(shè)計(jì)。

在本土領(lǐng)域,已有多家AI芯片廠商與EDA廠商合作,以此提高設(shè)計(jì)驗(yàn)證效率。例如:國(guó)微思爾芯原型驗(yàn)證工具助力埃瓦科技 3D 視覺(jué) AI 芯片量產(chǎn);鯤云科技采用芯華章的形式化驗(yàn)證工具穹瀚(GalaxFV),提升新一代復(fù)雜AI芯片的設(shè)計(jì)驗(yàn)證效率,進(jìn)一步保障復(fù)雜AI芯片的功能和可靠性。

而在“AI Inside”方面,EDA+AI更是已經(jīng)成為了熱門話題,不少專家都認(rèn)為EDA應(yīng)用AI是必然趨勢(shì),AI在其中可以起到加速和輔助作用。

在傳統(tǒng)EDA設(shè)計(jì)工具中,芯片架構(gòu)探索、設(shè)計(jì)、驗(yàn)證、布局布線等工作的人力占比巨大,隨著人工智能的興起,EDA設(shè)計(jì)工具也開始逐漸朝著智能化趨勢(shì)發(fā)展,在深度、強(qiáng)化學(xué)習(xí)等技術(shù)的加持下,智能化EDA設(shè)計(jì)能夠吸收過(guò)去的設(shè)計(jì)經(jīng)驗(yàn)和數(shù)據(jù), 有效減少人力投入、縮短設(shè)計(jì)周期、提高芯片設(shè)計(jì)及生產(chǎn)的性能和精度。

從某種意義上來(lái)說(shuō),芯片設(shè)計(jì)過(guò)程的復(fù)雜性非常適合 AI 算法。比如,當(dāng)AI應(yīng)用于布局布線、平面規(guī)劃等芯片后端設(shè)計(jì)時(shí),EDA工具可以通過(guò)攝取設(shè)計(jì)工具生成的大數(shù)據(jù)流來(lái)探索搜索空間,觀察設(shè)計(jì)如何隨時(shí)間演變,并調(diào)整設(shè)計(jì)選擇、技術(shù)參數(shù)和工作流程。

又或者,在計(jì)算時(shí)延中使用AI的方法,可以根據(jù)建模精確度把解決方案代入到時(shí)延范圍內(nèi),得到你最終想要的結(jié)果。

總的來(lái)說(shuō),只要AI技術(shù)運(yùn)用得好,可以把后端工具的運(yùn)行時(shí)間縮短。當(dāng)然,AI還可以在前端設(shè)計(jì)時(shí),通過(guò)建模檢測(cè)其在后端的運(yùn)行結(jié)果,讓前端工程師知道他們現(xiàn)在的優(yōu)化動(dòng)作在后端是否有效,能否縮減迭代的速度。

此外,EDA上云作為未來(lái)的趨勢(shì)之一,在云端上可以開放更多的計(jì)算資源,也可以加快設(shè)計(jì)和驗(yàn)證過(guò)程。

Chiplet時(shí)代,大放異彩的IP

與EDA一樣,IP核作為芯片設(shè)計(jì)中的關(guān)鍵一環(huán),通常是指事先定義,經(jīng)過(guò)驗(yàn)證可以重復(fù)使用的、能夠完成某些功能的設(shè)計(jì)模塊,可以降低芯片設(shè)計(jì)中冗余的設(shè)計(jì)成本,以及錯(cuò)誤發(fā)生風(fēng)險(xiǎn),提高設(shè)計(jì)效率。

在如今AI芯片企業(yè)分類中,除了Nvidia、Intel、AMD、Qualcomm、華為海思等芯片設(shè)計(jì)龍頭企業(yè),以及以寒武紀(jì)、地平線等為代表的專注于人工智能芯片研發(fā)企業(yè),還包括了ARM、Cadence、Synopsys等以IP授權(quán)為主要商業(yè)模式的企業(yè)。

對(duì)于AI芯片廠商來(lái)說(shuō),使用成熟、穩(wěn)定、滿足需求、質(zhì)量可靠的IP核,通過(guò)快速?gòu)?fù)用積累的技術(shù),可以有效提高芯片設(shè)計(jì)效率,提升芯片設(shè)計(jì)公司的交付能力,極大縮短SoC芯片的開發(fā)周期。

比如,接口IP的硬化服務(wù)能夠?yàn)?SoC 騰出空間,為達(dá)到更高的 AI 性能提供了寶貴的片上 SRAM 和處理器組件;專業(yè)的AI加速硬件IP能夠提供在芯片中部署AI加速功能所需的工具;內(nèi)存IP核解決方案支持針對(duì)不同AI內(nèi)存約束的高效架構(gòu),可以減少AI應(yīng)用中的延遲。

另外,由于IP廠商只設(shè)計(jì)芯片局部的某些功能模塊,因而更能夠追求這些功能模塊設(shè)計(jì)的最優(yōu)化,不斷迭代,更新,AI芯片廠商也因此可以借助先進(jìn)的IP核,在保持競(jìng)爭(zhēng)力的同時(shí),也可以保障芯片設(shè)計(jì)的按時(shí)交付。

當(dāng)然還有很重要的一點(diǎn)就是:Chiplet時(shí)代的到來(lái)。

Chiplet俗稱芯粒,也叫小芯片,它是將一類滿足特定功能的die(裸片),通過(guò)die-to-die內(nèi)部互聯(lián)技術(shù)實(shí)現(xiàn)多個(gè)模塊芯片與底層基礎(chǔ)芯片封裝在一起,形成一個(gè)系統(tǒng)芯片,以實(shí)現(xiàn)一種新形式的IP復(fù)用。從這個(gè)意義上來(lái)說(shuō),Chiplet也可以看作一個(gè)新的IP重用模式。

圖源:信達(dá)證券

當(dāng)前,算力已經(jīng)成為AI芯片的重要指標(biāo)之一,只有保證充足的算力,才能應(yīng)對(duì)爆發(fā)式增長(zhǎng)的計(jì)算需求。要想提升AI芯片的算力,增大芯片面積是最為簡(jiǎn)單有效的方法,然而芯片面積越大意味著良率越低,成本越高。為了解決芯片性能和良率之間的矛盾問(wèn)題,Chiplet技術(shù)出現(xiàn)了。

在Chiplet的加持下,IP 模塊經(jīng)濟(jì)性和復(fù)用性也有望得到大幅提升。不同功能的IP,如 CPU、存儲(chǔ)器、模擬接口等,可靈活選擇不同的工藝分別進(jìn)行生產(chǎn),從而可以靈活平衡計(jì)算性能與成本,實(shí)現(xiàn)功能模塊的最優(yōu)配置,而不必受限于晶圓廠工藝。

此外,Chiplet還可以看作是硅片級(jí)的IP,企業(yè)僅需將多個(gè)已經(jīng)成功驗(yàn)證的芯粒通過(guò)先進(jìn)封裝技術(shù)進(jìn)行封裝,即可得到相應(yīng)的產(chǎn)品,即高效,也降低了芯片設(shè)計(jì)的難度和成本。

因此,對(duì)于對(duì)性能有著高追求、渴望先進(jìn)工藝的AI芯片來(lái)說(shuō),IP和Chiplet無(wú)疑是其加速的一大利器。

加速中的芯片設(shè)計(jì)服務(wù)

同EDA和IP一樣,芯片設(shè)計(jì)服務(wù)作為芯片設(shè)計(jì)公司和晶圓廠之間的重要橋梁,對(duì)于AI芯片廠商來(lái)說(shuō),也是一個(gè)無(wú)比重要的存在。

不過(guò)與EDA和IP不同的是,IC設(shè)計(jì)服務(wù)提供商的主要作用則是,整合和利用自身的資源集中優(yōu)勢(shì)和豐富專業(yè)的設(shè)計(jì)開發(fā)能力及經(jīng)驗(yàn),為客戶爭(zhēng)取更具競(jìng)爭(zhēng)力的IP資源、晶圓制造乃至封裝測(cè)試等服務(wù)支持,有效降低和縮減客戶的芯片產(chǎn)品設(shè)計(jì)開發(fā)費(fèi)用、開發(fā)風(fēng)險(xiǎn)和開發(fā)周期,降低產(chǎn)品運(yùn)營(yíng)費(fèi)用和風(fēng)險(xiǎn)。

眾所周知,AI芯片的開發(fā)成本相當(dāng)高,尤其是ASIC架構(gòu)設(shè)計(jì)的芯片,流片數(shù)量動(dòng)則千萬(wàn),包含人力成本,投入可高達(dá)2500萬(wàn)美元以上。而與之相對(duì)的卻是,越來(lái)越多的初創(chuàng)型AI芯片企業(yè)。

中商情報(bào)網(wǎng)數(shù)據(jù)顯示,近年來(lái),我國(guó)AI芯片企業(yè)注冊(cè)量快速增長(zhǎng),由2017年的1110家迅速增長(zhǎng)至2021年的13492家,年均復(fù)合增長(zhǎng)率達(dá)86.7%。最新數(shù)據(jù)顯示,2022年1-5月,我國(guó)AI芯片企業(yè)注冊(cè)量達(dá)6783家,已超過(guò)2020年新增企業(yè)數(shù)量。

圖源:中商情報(bào)網(wǎng)

對(duì)于這些資金、人力都短缺的初創(chuàng)型AI芯片企業(yè),只有在有限的時(shí)間和資金中做出產(chǎn)品,才能獲得下一輪資本的青睞,才不會(huì)消失在時(shí)間的洪流中。而在此過(guò)程中,一家可靠、合適的設(shè)計(jì)服務(wù)供應(yīng)商便成為了重中之重。

眾所周知,芯片設(shè)計(jì)過(guò)程不是單方面一來(lái)一回地順序傳遞,而是有大量交互與溝通在重疊進(jìn)行,對(duì)于有芯片設(shè)計(jì)服務(wù)相關(guān)需求的公司而言,選擇設(shè)計(jì)服務(wù)團(tuán)隊(duì),不只是選擇一個(gè)供應(yīng)商,更是在選擇合作伙伴, 反之亦然。

而追趕在行業(yè)風(fēng)口的AI芯片設(shè)計(jì)就如同登山,目之所及有限,殊不知前路風(fēng)景,在披荊斬棘過(guò)程中,如果能匹配到合適的芯片設(shè)計(jì)服務(wù)團(tuán)隊(duì),就如同英雄降魔路上有了寶刀利器,可以更快走向最終勝利。

從上世紀(jì)80年代后期至今,芯片產(chǎn)業(yè)鏈中已經(jīng)涌現(xiàn)了一批芯片設(shè)計(jì)服務(wù)廠商,如何在眾多設(shè)計(jì)服務(wù)團(tuán)隊(duì)中尋找最合適自己的,或許成為了AI初創(chuàng)企業(yè)所需面對(duì)的新難題。

對(duì)于眾多處于初創(chuàng)階段的AI芯片企業(yè)來(lái)說(shuō),有了芯片設(shè)計(jì)服務(wù)商的助力,就可以把寶貴的人力財(cái)力更加專注于市場(chǎng),產(chǎn)品定義以及系統(tǒng)級(jí)支撐, 把芯片實(shí)現(xiàn)的專業(yè)要求交給專業(yè)團(tuán)隊(duì)實(shí)現(xiàn)。不過(guò)需要注意的是,在選擇芯片設(shè)計(jì)服務(wù)商時(shí),要明白自己的所需、所想,選擇與自己最適合、最匹配的,方可事半功倍。

寫在最后

隨著人工智能場(chǎng)景在金融、制造、電信、醫(yī)療、交通等行業(yè)應(yīng)用不斷深化,其發(fā)展也呈現(xiàn)出應(yīng)用場(chǎng)景多元化的特征。愈發(fā)多元的應(yīng)用場(chǎng)景,以及逐漸成熟的技術(shù),讓AI芯片市場(chǎng)競(jìng)爭(zhēng)越來(lái)越激烈。

“工欲善其事,必先利其器。”

想要成為這個(gè)競(jìng)爭(zhēng)激烈的行業(yè)內(nèi)的捷足先登者,或許學(xué)會(huì)運(yùn)用各類工具和設(shè)計(jì)資源,不失為一種正確的打開方式。

審核編輯 :李倩

-

asic

+關(guān)注

關(guān)注

34文章

1206瀏覽量

120765 -

eda

+關(guān)注

關(guān)注

71文章

2788瀏覽量

173876 -

AI芯片

+關(guān)注

關(guān)注

17文章

1906瀏覽量

35217

原文標(biāo)題:芯片競(jìng)速,你的AI芯片如何快人一步

文章出處:【微信號(hào):bdtdsj,微信公眾號(hào):中科院半導(dǎo)體所】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

2024年EDA/IP十大關(guān)鍵詞:除了AI和云化還有什么?

AI與物聯(lián)網(wǎng)雙向奔赴,達(dá)實(shí)智能已在AI應(yīng)用賽道先行一步

如果需要將DDC112U設(shè)置為非連續(xù)模式工作,應(yīng)該如何一步一步正確地設(shè)置芯片?

沙子變芯片,一步步帶你走進(jìn)高科技的微觀世界

SiFive發(fā)布MX系列高性能AI加速器IP

異構(gòu)混訓(xùn)整合不同架構(gòu)芯片資源,提高算力利用率

優(yōu)刻得與聯(lián)想AI實(shí)驗(yàn)室攜手共建高效AI資源池

AI+EDA加速雙向賦能,引領(lǐng)萬(wàn)物智能時(shí)代的創(chuàng)新

AI芯片設(shè)計(jì)來(lái)勢(shì)洶洶,EDA巨頭營(yíng)收順勢(shì)增長(zhǎng)

進(jìn)一步解讀英偉達(dá) Blackwell 架構(gòu)、NVlink及GB200 超級(jí)芯片

英偉達(dá)宣布收購(gòu)Run:ai

risc-v多核芯片在AI方面的應(yīng)用

國(guó)內(nèi)EDA工具AI技術(shù)應(yīng)用現(xiàn)狀及發(fā)展動(dòng)態(tài)分析

安霸發(fā)布5nm制程的CV75S系列芯片,進(jìn)一步拓寬AI SoC產(chǎn)品路線圖

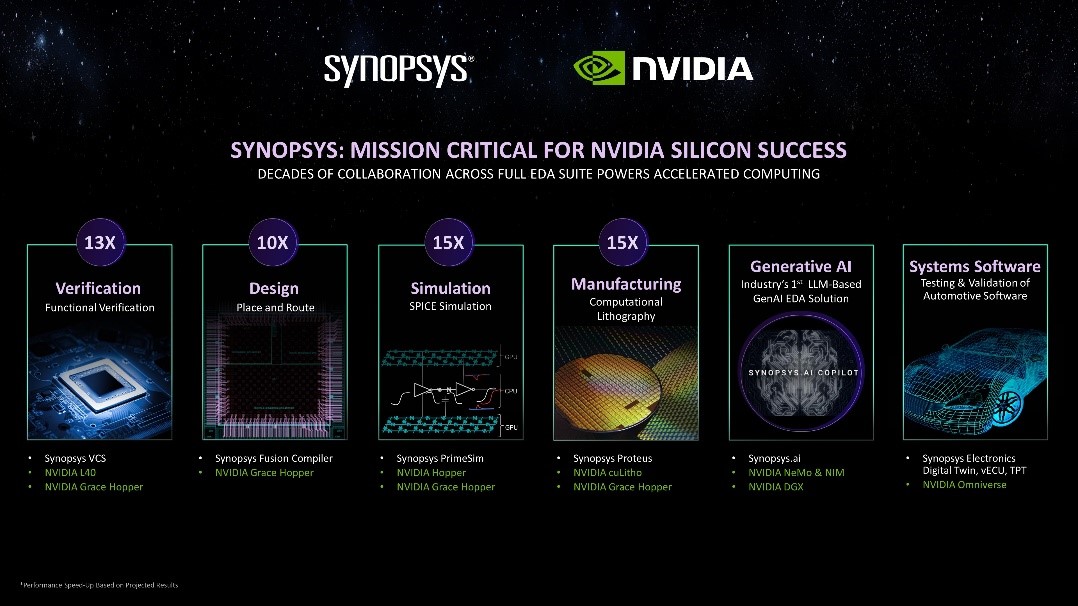

新思科技攜手英偉達(dá):基于加速計(jì)算、生成式AI和Omniverse釋放下一代EDA潛能

如何整合EDA、IP與設(shè)計(jì)資源,讓AI芯片快人一步?

如何整合EDA、IP與設(shè)計(jì)資源,讓AI芯片快人一步?

評(píng)論