我目前電腦用的內存還是DDR4,上個月才配了一臺電腦,用上了DDR5,但我感覺DDR5對于我來說,有點“性能過剩”了。

目前 DDR5 內存都還算不上大眾主流,但三星已經處于下一代 DDR6 內存的早期開發過程中。

在韓國水原舉行的一次研討會上,三星測試和系統封裝 (TSP) 副總裁透露,隨著未來內存本身性能的擴展,封裝技術需要不斷發展。該公司證實,他們已經投入下一代 DDR6 內存的早期開發階段,該內存將使用 MSAP 技術。

據三星稱,MSAP 已被其競爭對手(SK 海力士和美光)用于 DDR5。那么 MSAP 有什么新功能呢?嗯,MSAP 或改進的半加法工藝允許 DRAM 制造商創建具有更精細電路的內存模塊。這是通過在先前未觸及的空白空間中涂覆電路圖案來實現的,從而實現更好的連接和更快的傳輸速度。下一代 DDR6 內存不僅將利用 MSAP 來增強電路連接,還可以適應將被合并到 DDR6 內存中的層數增加。

相關媒體報道指出,之前的tenting方法只在圓形銅板將要形成電路圖案的區域進行涂覆,而將其他區域蝕刻掉。

但在 MSAP 中,除了電路之外的區域都經過涂層處理,而空白區域則進行了電鍍,從而可以實現更精細的電路。三星副總裁說,隨著存儲芯片容量和數據處理速度的增加,封裝的設計必須適應這一點。Ko說,隨著層數的增加和工藝變得更加復雜,內存封裝市場也有望成倍增長。

在扇出方面,另一種將 I/O 端子置于芯片外部以使芯片變得更小同時保持球布局的另一種封裝技術,三星同時應用了扇出晶圓級封裝 (FO-WLP) 和風扇面板級封裝 (FO-PLP)。

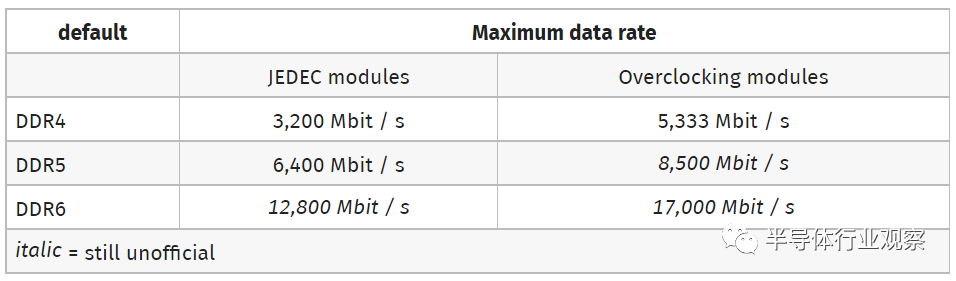

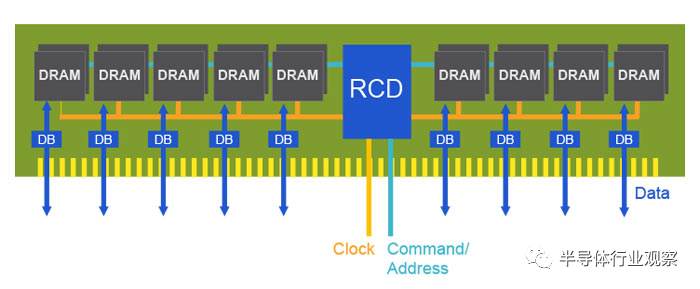

三星預計其 DDR6 設計將在 2024 年完成,但預計 2025 年之后不會商用。在規格方面,DDR6 內存將是現有 DDR5 內存的兩倍,傳輸速度高達 12,800 Mbps(JEDEC ) 和超頻速度超過 17,000 Mbps 范圍。目前,三星最快的 DDR5 DIMM具有高達 7,200 Mbps 的傳輸速度,因此在 JEDEC 上提高了 1.7 倍,在下一代內存芯片的超頻速度下提高了 2.36 倍。至于每個模塊的內存通道數量,DDR6 也將增加一倍,四個 16 位通道由 64 個內存庫連接。

至于標準方面,三星表示,DDR6 標準的開發已經開始,并將得到 JEDEC 的協助,JEDEC 是一個由 300 多名成員組成的半導體工程組織,其中包括一些世界上最大的計算機公司。

話雖如此,內存制造商已經強調了在未來將高達 DDR5-12600 的速度,因此 DDR5 絕對具有消費平臺的潛力。隨著 AMD 的 Zen 4 和英特爾的 Raptor Lake CPU 平臺的推出,預計今年晚些時候 DDR5 內存模塊會更快、更優化。

Samsung 還透露了一些關于GDDR6 標準的后續資訊,該公司可能正在開發GDDR6+ 標準,提供高達24 Gbps 的速度,比目前GDDR6 標準提供的18 Gbps 更快,GDDR6+ 將使用Samsung 1z nm 制程制造。

根據之前的報道GDDR7 標準也在Samsung 的路線圖上,GDDR7 主要將記憶體頻寬增加到32 Gbps,并加入即時錯誤保護功能,不過Samsung 沒有提供近一步的技術資料與路線圖時間。另外,Samsung 將會在2022 年第二季開始大量生產HBM3 (High-Bandwidth-Memory Gen3) 記憶體。

雖然上述記憶體技術距離實際應用到產品上并且公開販售仍需要一段時間,不過時代總會不斷向前進,科技也是,希望科技發展的同時也能兼顧平價,先講求不傷荷包,再求速度。

關于DDR 6,我們可能面臨的挑戰

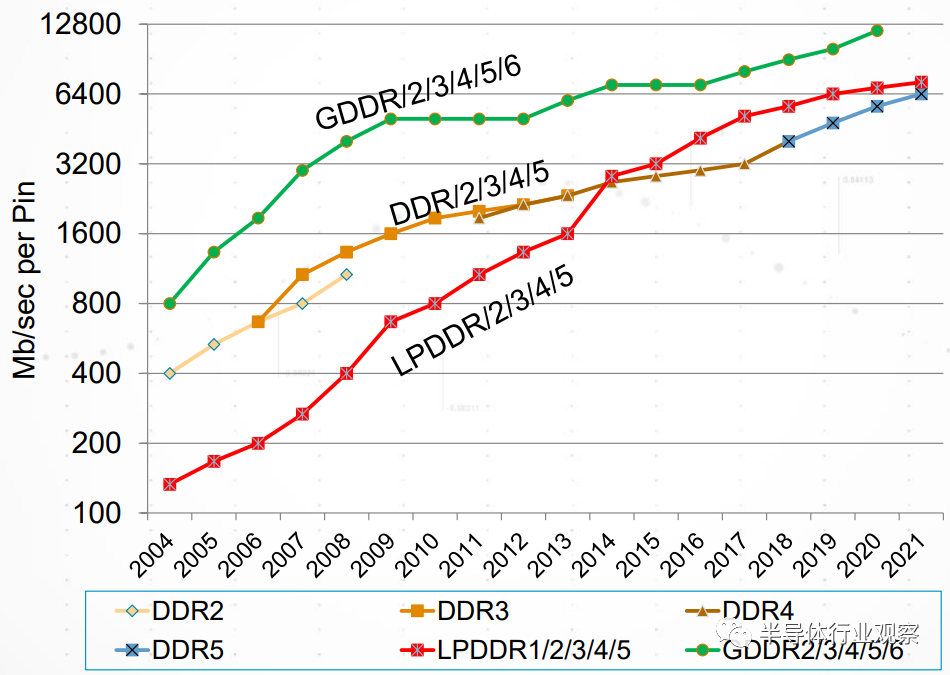

DDR 的引入可以說是電子行業進入高速數字化的時期。當然,ECL 邏輯組件發揮了作用,但 DDR 存儲器一直是一個典型的例子,表明數據速率隨著時間的推移而穩步提高。DDR5 的應用仍在推進中,但業界已經在展望 DDR6 RAM。這讓我想到了應用研究人員在電信中所扮演的基本角色,在 5G 部署完成之前,工程師已經在為 6G 進行開發。

在 DDR3 之前,設計人員需要考慮設計以適應建立和保持時間以及總線上的受控阻抗。直到 DDR3 數據速率的高端為止,色散補償都不是這樣的問題,因為抖動開始成為信號解釋中的主要問題。在低電平信號中看到的相對較小的抖動將大到足以關閉 DDR3 信號的眼圖。因此,更新了 JEDEC 標準以提供 DDR4 眼圖的設計容差。

DDR5 采用了高端 DDR4 數據速率,并通過使總線更快而不是更寬而再次將其翻倍。在布置并行單端網絡方面,您仍在處理 DDR4 布線挑戰,但這些通道要短得多。總線也將運行得足夠快,以至于誤碼主要由接收器處的反射損耗、任何層轉換處以及色散引起。較短的通道有效地降低了總插入損耗,但回波損耗色散 需要通過極高帶寬的極其精確的互連阻抗設計來補償。

對于 DDR5,數據傳輸在具有雙向通信的單端網絡上以短脈沖形式發生。全速時鐘允許在互連的每一端在讀取和寫入之間切換。一切都必須非常快速地切換,這需要無可挑剔的 PDN 設計來盡可能地抑制抖動。典型電路板上的 PDN 阻抗只能變得如此之低,而且 DDR5 中的低信號電平(最大 1.1 V)對數字信號施加了非常嚴格的紋波/抖動限制。這些以反射為主的通道問題和疊加在低電平信號上的低紋波要求現在迫使控制器在 DDR5 接口中使用均衡,以補償信號失真和符號間干擾 (ISI)。請注意,這種均衡已經用于高速差分串行標準(例如,SerDes 通道中的 LVDS)。

DDR5 中還有許多其他設計挑戰需要考慮,但上面列出的挑戰可以說是最大的挑戰。

那么DDR6內存呢?

與前幾代產品一樣,DDR6 RAM 旨在將 DDR5 的最大數據速率提高一倍。如果您正在為 DDR6 RAM 創新模塊,仍然有很多未解決的問題。人們普遍認為總線不會更寬,而且 DDR5 的速度已經快到足以撞上所謂的“內存墻”。這使得調制(例如 PAM 或 QAM)成為提高數據速率超過完全模擬通道(例如 100G 以太網)的最后可用選項。

由于進入模擬高速通道會破壞我們對 DDR 的了解,您可能會看到 PAM 或 QAM 與控制器中嵌入的一些專有均衡方案相結合。雖然主要挑戰在于 IC 設計人員,但當我們查看 DDR6 RAM 通道中使用的高帶寬信號時,電路板設計人員仍有許多需要解決的問題。

DDR6 RAM 中的挑戰主要發生在芯片級,但 DDR5 中相同的板級挑戰也適用于 DDR6 RAM。我上面提到的 DDR5 中的電源完整性挑戰不會在 DDR6 RAM 中消失。一旦對 DDR6 信號施加調制,DDR6 的電源完整性挑戰就是將平坦的 PDN 阻抗擴展到更高的信號帶寬。將平坦的 PDN 阻抗擴展到更高的頻率就是要使 Tx 側的抖動保持在較低水平,從而使 Rx 側的 ISI 保持足夠低,以便可以通過均衡來解析信號。DDR5 模塊的板載電源管理 IC 可能還會出現在 DDR6 RAM 模塊上,以幫助調節整個模塊的電源。

嵌入式系統設計人員可能會落后于 DDR5/6 用戶。與使用模塊(PC 和服務器)的系統相比,它們將擁有更輕松的時間,因為連接器處的損耗被消除并轉移到球/模具級別。然而,更小的空間對于嵌入式設計師來說是一把雙刃劍。這些系統更小,因此他們已經希望將內存 IC 安裝在靠近系統控制器的板上。然而,由于空間更小,他們現在更難以處理電路板部分之間的輻射 EMI。

像在不同功能塊之間進行屏蔽這樣簡單的東西對于嵌入式和 PC/服務器都是有用的。在這里,我們正在討論兩種可能的屏蔽類型:

高帶寬隔離結構。可以調整這些結構以提供高達高頻的高隔離度。它們占據了表層的空間,但這些結構比調諧到更高頻率時變得更小。這是嵌入式系統的一個選項,其中 RAM IC 與控制器放置在同一塊板上。

不同層的創意路由。您可以利用內部平面來防止主板上不同 DDR 總線之間的串擾。一旦你突破了模塊的連接器,模塊可能與其他電路足夠遠,串擾不再是問題。

審核編輯 :李倩

-

芯片

+關注

關注

456文章

51170瀏覽量

427227 -

內存

+關注

關注

8文章

3055瀏覽量

74327 -

DDR4

+關注

關注

12文章

322瀏覽量

40956

原文標題:DDR 6 內存已經投入研發

文章出處:【微信號:strongerHuang,微信公眾號:strongerHuang】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

蘋果2025年面臨多重挑戰

7納米工藝面臨的各種挑戰與解決方案

產業"內卷化"下磁性元件面臨的機遇與挑戰

IPv6的優勢和挑戰

iPhone 16系列或面臨300萬臺減產

PSoC63有沒有可能讓引腳始終保持低電平?

全光網應用面臨的挑戰

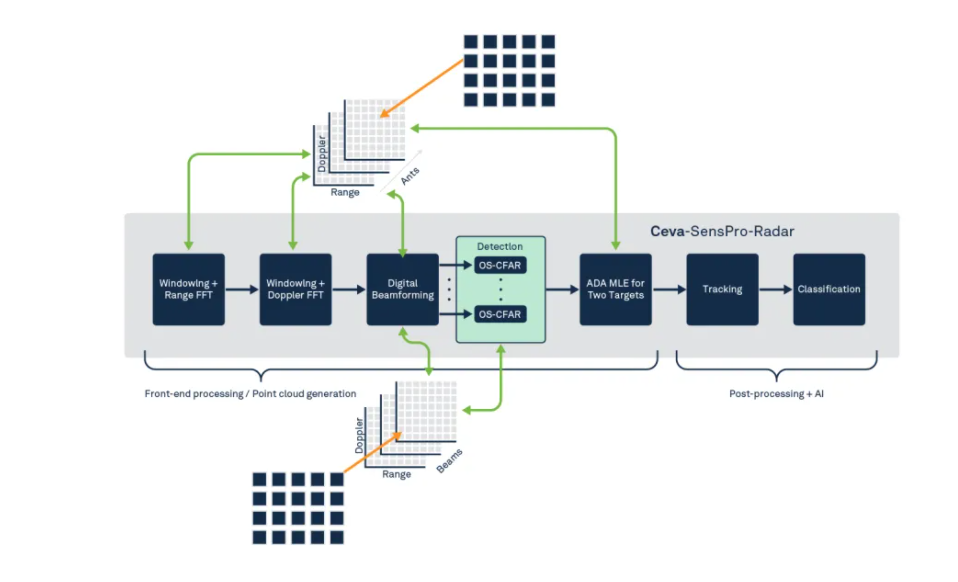

汽車雷達系統設計面臨的挑戰

關于DDR6我們可能面臨的挑戰

關于DDR6我們可能面臨的挑戰

評論