本文章探討一下FPGA的時序input delay約束,本文章內容,來源于明德揚時序約束專題課視頻。

《FPGA時序約束分享01_約束四大步驟》概括性地介紹 了時序約束的四個步驟,對時序約束進行了分類,并得到了一個分類表。

《FPGA時序約束分享02_時鐘約束》詳細介紹了關于時鐘的約束,根據時鐘來源可以分成輸入時鐘約束、PLL等衍生時鐘約束和自己分頻的時鐘約束等三種類型。這三種類型的約束方法均有所不同,讀者需要掌握區分方法。

本文,筆者將詳細介紹輸入延時(input delay)的概念、場景分類、約束參數獲取方法以及約束方法。

大家好,歡迎大家收看明德揚推出的至簡設計法系列視頻教程。本節課我們繼續時序約束的第三個步驟,output delay 的一個設置。我是本人視頻主講潘老師。來講這個視頻這個步驟之前呢,我們來看一下我們的提供的步驟。這個圖片啊,我們第三大步驟就是output delay 的。那我們這個步驟呢要看的時候要看三種情況啊,一種是系統同步的情況,一種是源同步的情況。而源同步呢我們又分SDR和DDR這兩種啊,所以歸納起來我們有三種情況。這三種情況呢就會有不同的設置。我們這次需要參考的資料呢,仍然是我們這個PDF文檔啊,我們提供給大家一個PDF文檔。好,我們看一下啊標題啊,我們這次課程我們呢會講這幾個步驟啊,第一個輸出原始的概念。第二個就是我們用兩種的測量方法去得到我們的時序參數,然后去來進行進行約束。之后呢,我們看第三種呢就是我們的不同情況啊,第一個是系統同步,第二個是源同步。而源同步呢我們就分成SDR和DDR這兩種啊。

第1節:輸出延時概念

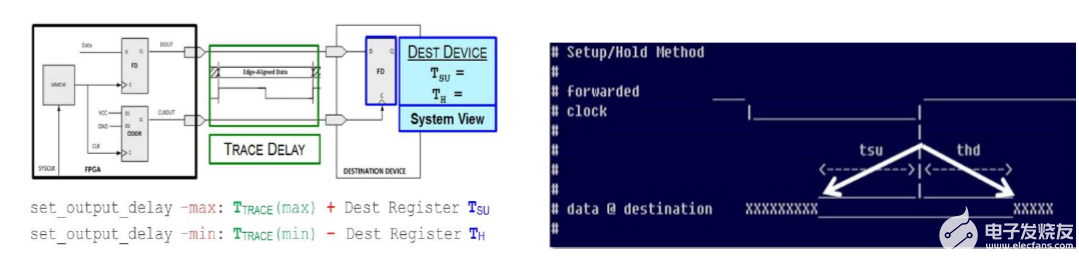

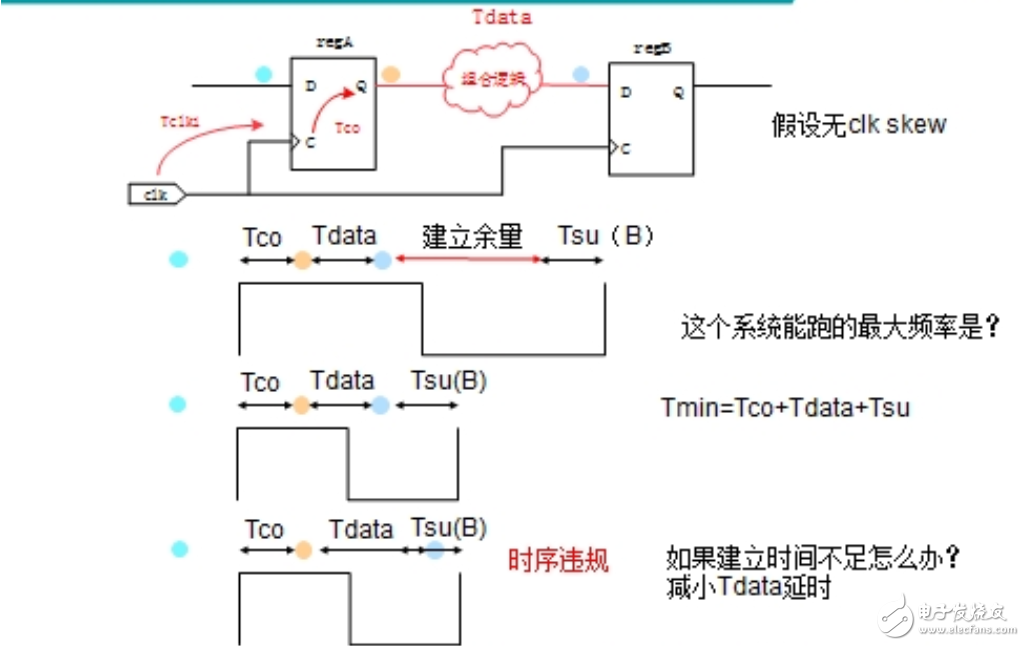

目標:讓FPGA調整時序,使時序滿足下游器件要求。max用于考慮建立時間:跟著正數,表示數據在時鐘采樣沿之前就到達。公式:最大板級延時+TSUmin用于考慮保持時間:后面負數,表示數據在時鐘采樣沿之后還保持了一段時間 。公式:最小板級延時-TH假如板級延時為0,則max就是下游器件的“TSU”;min則是下游器件的“-Th”。

好,我們看第一個輸出延時的概念。首先我們設置輸出延時,為什么要輸出延時呢?我們目標是讓了為了讓fpga調整它自己的輸出的時序,使我們輸出的時序滿足下游器件的一個要求。這樣子呢我們下游器件呢就能夠正確的采集我們的時序了啊,所以目標是這樣子。大家記住目標是為了下游器件正確的采集,因此要保證自己輸出的是正確的啊,所以我們要自己去調整。那么我們同樣的就是告訴fpga,我們下游器件的要求是什么啊,我們告訴我們fpga下游期間要求是什么啊,我們就根據知道這個要求,我來自己調整這個時序的。這就是我們這個輸出延時這個目標。啊,記住fpga是輸出啊,到這個下線是輸入。好,我們的這個呃輸出延時同樣有兩個參數,一個是max,一個是min的,一個是最大,一個是最小的延時,最大的延時。干嘛用呢?你可以用于這樣考慮,是用于考慮建立時間用的啊,他們一般是跟著正數啊,正數表示數據在時鐘采樣沿之前就到達了啊,我們公式呢這個值怎么來的,這種最大板延時加上這個TSU啊,TSU就是建立時間。誰的建立時間呢,是下游器件的建立時間啊,也就是說我的板的延時加上你下游期間他要求的鑒定時間就是我這個max 啊。而這min呢是什么?最小是用于考慮保持時間,誰的保持時間是下游期間保持時間啊,后面跟著負數表示數據在使用采樣沿之后還保持了一段時間啊,是這樣意思,而我們的公式是怎么樣呢?是最小的板級延時啊,就是延時減去TH啊,這個就保持時間。這個參數從哪里來呢?從下游器件這個要求里來啊,比如說我的板子延時在電路板子上延時減去你的這個要求,保持時間就是我的一個啊最min的一個最小延時就注意一般這個值是比較小,而這比較大一減去就成了負數了啊。例如啊例如我們板子延時是零啊,板子假如說一個很理想的情況下,就是我現在一直沒一點延遲都沒有,反正延遲為零,這也是很常見的一種情況啊,反正也是為零。而就是下游期間的這個TSU啊,這個就是下游期間的建立時間要求。而這個面呢則是下游器件的。保持時間這個負號啊,負點擊TH這也是。就是這個時候呢,這個最小的是一個負數啊是個負數。這就是我們的輸入延時概念。在這個里面要記住的是公式啊,最大板的延時加上你的鑒定時間要求,就是我的max 啊,最小板的延時減去TH就是你保持時間,,就是我的最小時間要求。

第2節:約束語句

第3節:輸出延時的目的

第4節:參數獲取的兩種方法

好,第二個我們看一下兩種測量方法。對于。我們的output delay 呢也有兩種的一個測量方式。

4.1 下游器件的參數(推薦)

第一種呢是根據下游器件的參數啊,也就是說我們呃從下游器件它一定有數據手冊。它的數據手冊一定會告訴你這個建立時間和保持時間的要求。我們從在建立時間保時間里面得到它參數之后呢,就可以進行設置了啊,就約束了。

4.2 示波器測量

第二種方法是用吸波器測量我們下游器件的一個輸入端口啊,去看到得到它的時序信息。得到什么時序信息呢?是得到它的一個啊,比如說它延時這種信息啊,但這種呢我們一般呢不常用。我們推薦的是利用這一種方法,這要求我們呢這個硬件呢就做的規范啊,這個很好一些啊,不要說延時來抖來抖去啊這種情況。所以一般我們之前講了也講下游器件這種參數的一個方式。

第5節:各應用場景下的約束方法

好,我們看一下啊,我們分不同情況來討論一下這種情呃怎么約束的問題啊。

5.1 系統同步

好,第三,我們就根據不同情況呢,我們要進行配置的第一種呢叫系統同步。系統同步呢上節課已經講過,就是fpga和下游器件呢都是共用一個時鐘的啊一個時鐘。我們可以認為這個時鐘的延時是等于零的啊等于零的。好,而他fpga把這數據送出來啊,它是有一定的延時啊,送上給這個下游器件。那下游器件這里面它有自己的一個建立時間保持性要求。我們從數據手冊手冊里面會得到它這樣的參數不到它建時間是2萬秒,它的這個TH就是1納秒的,它的鑒定時間保持性要求。而這里呢就是可能我這個延時啊符合我的一個抖動的情況啊。延時這里我們通過一個呃測量啊,或者說計算方式可以得到。比如說它的方式是哎不是它抖動最大是0.5,有時候是0.3,最小是0.3。ok那你這樣得到之后呢,下一步呢我們就知道它進行配置了。比如說它最大延時什么呀,就是我的最大的板級延時,加上我的建立時間要求就是2加上0.5,就是我的最大的一個延時。啊,而最小的是什么呢?這是我最小的0.3,這也是減去我的保持時間要求啊,就是這個1納秒,那是0.3減去一,那就負的0.7,這個是這個要求啊。我們在這PDF130頁呢也有講述這個過程的概念啊,請大家可以看一下啊,我們看到這約束方式。第一個是生成時鐘呢啊這個肯定是要有的,每個端口進來都有個時鐘。然后呢,我們會告訴他這個時鐘啊,這個時鐘它的最大延時是多少呢?是2.5啊,它的對象是這個DOUT,就是這個DOUT。而它最小延時的是-0.7。好,這是系統同步的情況。系統同步就是時鐘呢是共用一個的是fpga跟下游器件共用一個的。

5.2 源同步SDR

好,接下來我們看一下源同步,就是說它的fpga送數據的同時,也送時鐘給下一個模塊啊,時鐘和數據一起送的。其中我們要跟SDR和DDR。SDR是指邊沿上升沿去采樣,SDR是指上升點和下降點都去采樣。

因此我們先看一下SDR是吧?SDR就是上沿進行采樣的方式。啊,同樣的方式呢,我們同樣呢也能得到它的一個結果。它跟是跟系統同步是一樣的啊,它它的方法也是一樣的,它也是通過查數據手冊得到我的鑒定時間,它保持的要求也能知道我的這個延時的抖動是多少啊。比如說我們測量之后得到抖動是多少,得到最大抖動和最小抖動之后呢,我就能配置啊。這公式也講了啊,最大的是指我的延時最大加上我的建立時間要求啊,而最小是指我的延遲最小減去我的這個呃保持時間要求,就是我的最小

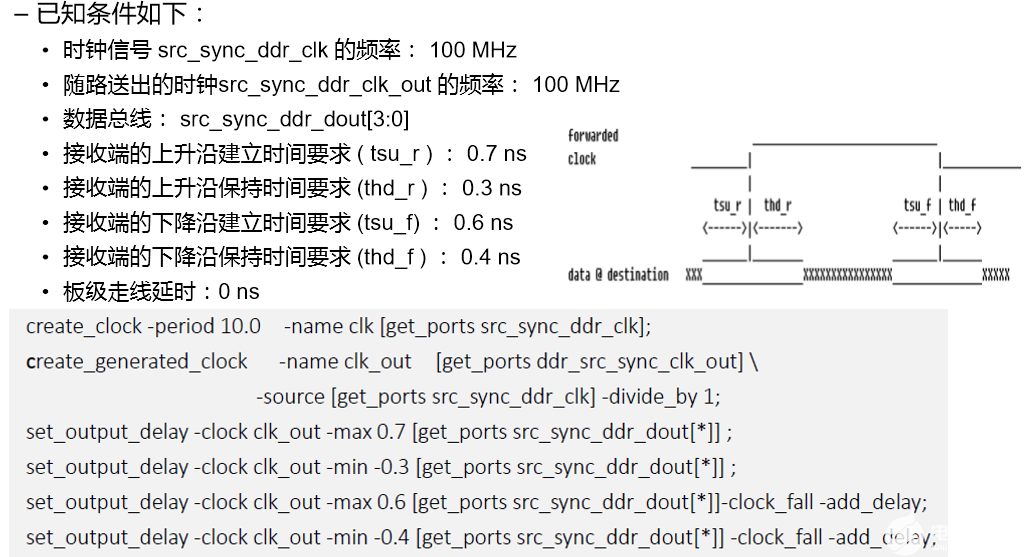

5.3源同步-DDR(查手冊方法)

然后DDR呢,DDR是指上升沿下降沿都是同步,都是都采樣的。因此呢它是這樣子采樣啊,這邊和這邊都會采樣哈,都會采樣。我們可以通過一個方式是吧?例如說我們去查這個手冊啊,我們通過同樣可以查手冊得到他這個要求。比如說他會要求你這個建立時間多少,保持時間多少,而這邊的建立時間多少,保時間多少。例如說我們這里有個例子啊,比如說他的商業鑒定時間要求是0.7。比如說這個是0.7,這個是0.3,這個是0.6和這是0.4啊。因此呢我們就要對它進行配置約束啊,outlay啊我們可以看到時鐘生生成啊生成一個時鐘。好了,我們看一下它最大的一個延時就是啊零點7。對于它來講最大是0.7,最小是什么呢?啊,0減去0.3。我們這時候把那個板子驗收啊,就考慮為零了啊。0減去0.3。而在這個時刻呢,我們是最大的是0.6,最小是零減去0.4,那就是。負的0.4啊,注意的是我們這個for下降沿的時候,要加上這個clock for啊加I杠ADD delay。好,加上這句話啊,這個是我們那個正確的方式。其中這個啊這個比如說這個可能是不一定要的啊,這個中間這個不一樣。我們這最主要在講的是這個后面這個四個部分,前面部分還是跟我們的時鐘的方式是一樣的。比如說我們在前面時鐘進來,還有這個我們就要這個后面。假如說我們配置output delay 哈,再加上后面這四句話的啊。這是我們DDR的一個方式。

好了,有的同學說我們的input delay 有個什么叫邊緣呢?也叫叫中心對齊的。為什么我們這里就沒有了啊,因為大家知道我們input delay 那個是靠測量的方式去得到的啊,而我們這個呢是查數據手冊的方式,查數據手冊。那么他的邊緣這個點的時候,他就不不可能會抖動的啊不可能會抖動的。他一定會建立。你在下降沿的時候呢,你在之前會穩定,穩定多久,之后會穩定多久,因此他一定是這么穩這樣一個情況的啊,他會把這個實際參數要求給你啊,所以我們沒有什么邊緣對齊和中心對齊的一個情況。啊,我們從查數據手冊就會查到這幾個參數,然后進行配置就可以了啊。還有一點就是對于我們的板級延時的一般情況下呢,如果我們硬件做的好的板,這件事是不需要考慮的。也就是說我們的output delay 一般呢就是設置它的鑒定時間啊,就是從手冊里面得到它鑒定時間和保質時間這兩個參數。然后根據它公式直接就是配置就可以了啊,所以它output delay 的方式相對比較簡單。

第6節:總結與建議

好,我們總結一下,我們還是按照根據根據我們的經驗,就是按照前面的順序去索引,找到對應的情況,按要求進行約束啊。比如說我現在這個端口是屬于上面三種情況中的哪一種,如果是哪一種,你就按照那一種進行配置啊進行約束就可以了。

啊,第二個就是我們還是跟前面input delay 的時候強調過的input delay 、output delay就是告訴工具我現在的實際情況。比如說我告訴我fpga下游期間的情況是要求是什么啊,直接把這個結果告訴fpga就行了。你不用管fpga他怎么移啊,他要移多少,你都不用管,你就告訴他現實的情況啊。然后fpga他自動會計算,最后決定我要偏移多少時序。然后后面有個相似的,就是假如說我們有一個叫offset in /out這種東西啊,就是告訴你之前你偏移多少哈,偏移多少啊,從而滿足時序這個這樣子的,我們就要自己去計算這個這一步呢就是不需要計算了。啊,這就是我們的output delay 一個配置方式啊,相對比較簡單。好,本次視頻講這里,謝謝。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605996 -

延時

+關注

關注

0文章

107瀏覽量

25582 -

時序約束

+關注

關注

1文章

115瀏覽量

13457

發布評論請先 登錄

相關推薦

FPGA時序約束之衍生時鐘約束和時鐘分組約束

FPGA靜態時序分析——IO口時序(Input Delay /output Delay)

華為內部經典FPGA時序資料---FPGA input delay約束的方法

FPGA中的時序約束設計

FPGA時序約束分析余量

FPGA的時序input delay約束

FPGA的時序input delay約束

評論