本人最早接觸SI仿真的時(shí)候,只是進(jìn)行一個(gè)簡單的流程操作,其中涉及到的原理、模型知之甚少,再后來慢慢的接觸到了深一點(diǎn)的東西開始自己搭建電路了解到了IBIS。用于電路仿真的模型有好多,可能IBIS是最常用和最方便的一個(gè),一般這個(gè)東西都是芯片廠家提供的,其中的一些原理又是一個(gè)很復(fù)雜的事情。下面簡單整理IBIS中的構(gòu)造:

一 IBIS簡介

1.IBIS(Input/Output Buffer Information Specification):輸入輸出緩沖器,是一個(gè)行為級(jí)模型,描述的是電壓與電流、電壓與時(shí)間的關(guān)系,也是一種基于V/I曲線的對(duì)于輸入輸出端口快速準(zhǔn)確建模的方法,是反映芯片驅(qū)動(dòng)和接受電氣特性的一種國際標(biāo)準(zhǔn)。

2.IBIS 本身只是一種文件格式,它說明在一標(biāo)準(zhǔn)的IBIS 文件中如何記錄一個(gè)芯片的驅(qū)動(dòng)器和接收器的不同參數(shù),但并不說明這些被記錄的參數(shù)如何使用,這些參數(shù)需要由使用IBIS 模型的仿真工具來讀取。

二 IBIS模型結(jié)構(gòu)

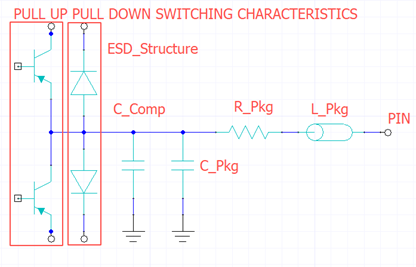

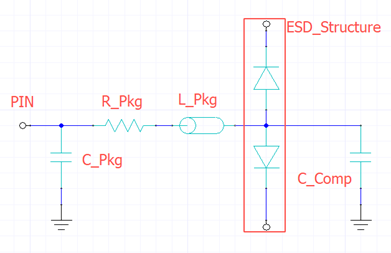

IBIS的模型結(jié)構(gòu)分為輸入和輸出,如下圖:

1.輸出結(jié)構(gòu):包含一個(gè)PMOS、一個(gè)NMOS、兩個(gè)ESD保護(hù)二極管、芯片的電容和封裝寄生參數(shù)

C_PKGR_PKGL_PKG是整個(gè)芯片的等效電容、電阻、電感特性

C_Comp為硅片上腳的壓焊盤電容 (結(jié)電容)。

2.輸入結(jié)構(gòu):包含兩個(gè)ESD保護(hù)二極管、芯片的電容和封裝寄生參數(shù)

C_PKGR_PKGL_PKG是整個(gè)芯片的等效電容、電阻、電感特性

C_Comp為硅片上腳的壓焊盤電容 (結(jié)電容)。

三 IBIS文件結(jié)構(gòu)

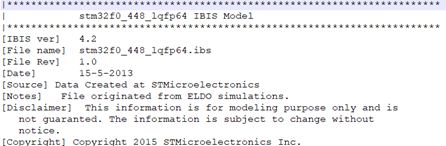

1.頭文件

這部分包含了IBIS的版本、文件名、版權(quán)等信息,如下圖:是下載于ST官網(wǎng)的STM的IBIS模型的頭文件:

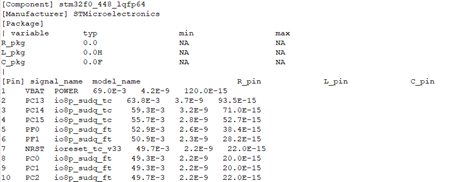

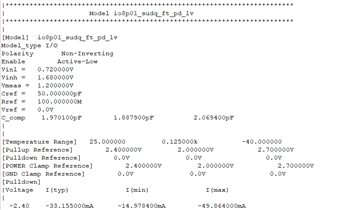

2.器件描述

包含器件模型名稱、器件名稱、廠商、封裝和引腳等信息,如下圖:

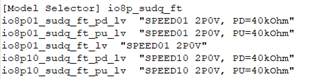

3.模型描述

這部門定義了模型對(duì)應(yīng)的緩沖器類型、Pulldown、Pullup、 Power_Clamp、Gnd_Clamp的IlV數(shù)據(jù)表;Ramp數(shù)據(jù);描述波形上升/下降沿的VIT數(shù)據(jù)表等,如下圖:

四 IBIS在信號(hào)完整性中的應(yīng)用

IBIS在信號(hào)完整性仿真中有不可或缺的作用,它可以作為一個(gè)源端和接收端。它可以被大數(shù)的EDA軟件識(shí)別,并且在有些仿真的軟件中沒有IBIS模型,是不能進(jìn)行時(shí)域仿真的。在IBIS模型的基礎(chǔ)之上,我們可以分析傳輸線上的信號(hào)完整性問題,包括源端到負(fù)載端的阻抗、串?dāng)_、反射、時(shí)延等時(shí)域問題。

IBIS模型會(huì)把每個(gè)I/O或pin分為幾種狀態(tài)(輸入、輸出、浮空),把這幾種狀態(tài)配置成幾種模型,通過調(diào)用I/O或pin的幾種模型來模擬輸入輸出。

審核編輯:湯梓紅

-

緩沖器

+關(guān)注

關(guān)注

6文章

1930瀏覽量

45643 -

電路仿真

+關(guān)注

關(guān)注

37文章

208瀏覽量

95763 -

IBIS

+關(guān)注

關(guān)注

1文章

55瀏覽量

19941

原文標(biāo)題:仿真設(shè)計(jì)---IBIS簡介(一)

文章出處:【微信號(hào):FANYPCB,微信公眾號(hào):凡億PCB】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

IBIS 模型

請(qǐng)問有人知道IBIS模型怎么使用嗎?

跪求ibis仿真模型

高速互連IBIS仿真模型概述

生成IBIS模型錯(cuò)誤

哪里可以找到IBIS模型?

MPOA的模型結(jié)構(gòu),MPOA的模型結(jié)構(gòu)是什么?

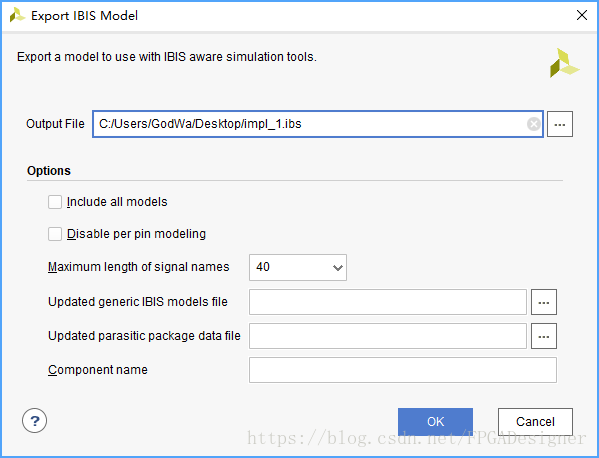

Vivado IBIS模型創(chuàng)建及導(dǎo)出方式

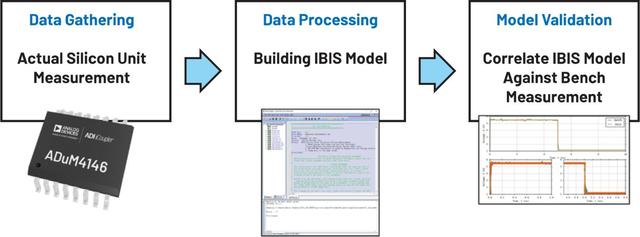

AN-715: 走近IBIS模型:什么是IBIS模型?它們是如何生成的?

初識(shí)IBIS模型

IBIS模型入門介紹

IBIS的模型結(jié)構(gòu)與文件結(jié)構(gòu)

IBIS的模型結(jié)構(gòu)與文件結(jié)構(gòu)

評(píng)論