明德揚有完整的時序約束課程與理論,接下來我們會一章一章以圖文結合的形式與大家分享時序約束的知識。要掌握FPGA時序約束,了解D觸發器以及FPGA運行原理是必備的前提。今天第一章,我們就從D觸發器開始講起。

一、D觸發器的基本概念

1、D觸發器結構

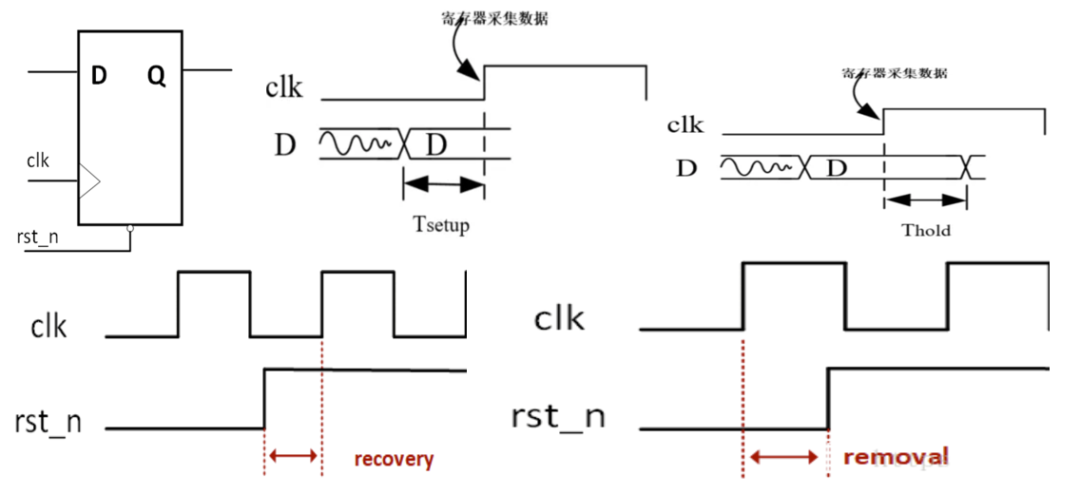

首先是D觸發器的結構,其硬件電路圖如下所示,可以看到D觸發器包含復位、時鐘、輸入和輸出;信號由D端輸入,clk給到上升沿的指示,Q端輸出信號。

D觸發器的功能很簡單。

當R等于0時,q固定輸出0;

當R等于1時,遇到CLK的上升沿時,將D的值賦給Q,D是什么Q就是什么;非CLK的上升沿,Q保持不變。

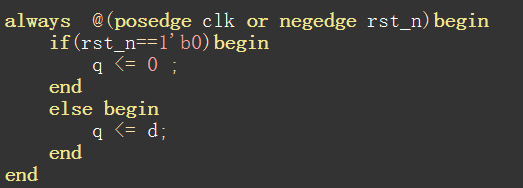

2、D觸發器代碼

D觸發器的代碼也很簡單,如下圖所示,從代碼的描述來看,依舊是

當rst_n等于0時,q固定輸出0;

當rst_n等于1時,遇到clk的上升沿時,將d的值賦給q,d是什么q就是什么;非clk的上升沿,q保持不變。

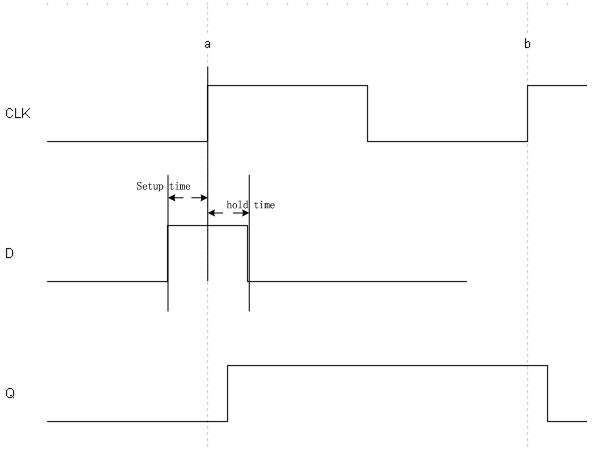

3、D觸發器波形

D觸發器工作波形如下所示,時鐘處于上升沿的時,如果輸入信號D為1,輸出信號Q也為1;如果輸入信號D為0,那么輸出信號Q也為0。

4、建立時間和保持時間

前面波形圖可以看到,D觸發器在上升沿處進行信號采集,為了保證采集到的數據準確性,信號D在上升沿前后會保持狀態一段時間。在上升沿前的這段時間為setup_time,叫做建立時間;上升沿后的這段時間為hold_time部分,叫做保持時間。

1

關于建立時間和保持時間有幾個關鍵點需要注意。

首先D觸發器的數據輸入端必須在建立時間前到達,并且要保持到持續時間以后,這樣才可以保證FPGA可以采集到正確的數據。

其次建立時間和保持時間是D觸發器的固有屬性,是不可改變的。注意,這里說的不可改變,是指不能從代碼層次去改變。例如我們買了一個FPGA開發板,其FPGA芯片的D觸發器建立時間和保持時間就是固定的,沒辦法從VERILOG去修改,除非換一個芯片。

二、電路的延時

1、電路延時原理

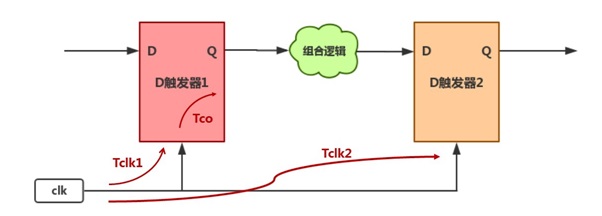

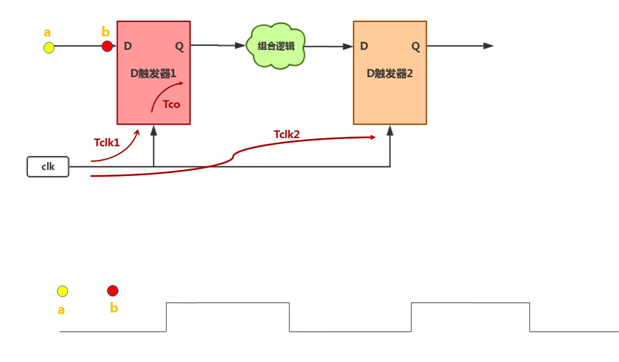

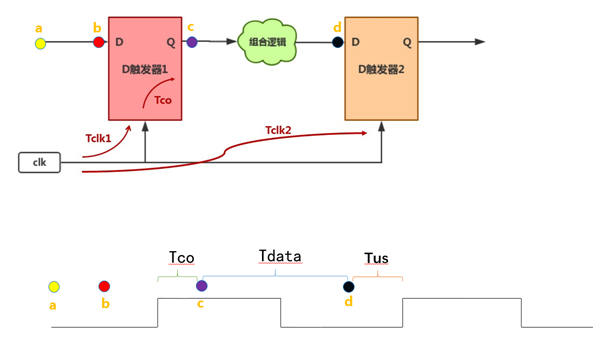

我們知道從物理層面看電平通過每個階段都是需要一段時間的,這就是電路的延時,我們通過FPGA中最經典的結構來學習一下電路的延時。使用了兩個D觸發器,中間由組合邏輯進行相連,即通過一個組合邏輯電路將兩個D觸發器相連。電路圖如下圖所示:

從圖中可以看出,一個有效信號經過D觸發器1之后,接著經過一段組合邏輯(可以是加法器、選擇器、乘法器這些電路,也可以僅僅是連線)然后到達另一個D觸發器2,D觸發器2對信號進行判斷后繼續進行輸出。下面逐個分析這個基本結構里面包含的時間參數。

首先Tclk1是時鐘到D觸發器1的時間。Tclk2為時鐘到達D觸發器2的時間,在真實的物理情況下,因為有線路的延時,兩個時鐘采到的上升沿其實是不同的,有一點微小的差別;但是FPGA里面,我們經常把這個時間忽略掉,因為我們FPGA時鐘時專門優化過的,它們之間的差別會比較小,因此在這里我們先忽略不計。Tclk1和Tclk2是時鐘延時。

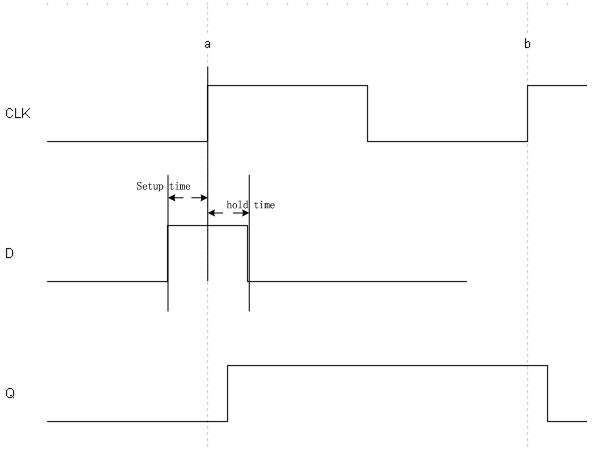

還有一段時間為D觸發器的傳輸延時,即上升沿之后,采集到的數據從進入到出來這段時間延時。如下圖所示,輸出信號Q在上升沿后一段時間由0變1,這段為D觸發器的傳輸延時。

接著D觸發器1之后信號需要通過組合邏輯賦到D觸發器2之前的位置,這段時間是組合邏輯的延時,即信號通過組合邏輯這段時間的延時為組合邏輯延時Tdata。

最后還有前面講到的建立時間和保持時間,信號在D觸發器2會有建立時間和保持時間,這就是D觸發器本身的延時。

2、時序表示電路的延時

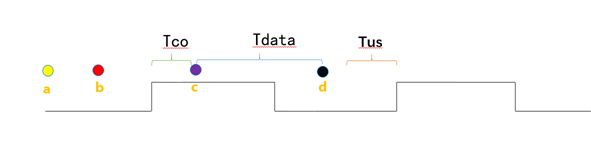

這里我們可以用時序來表示這組結構中的信號變化。如下所示,比如我們有兩個時鐘上升沿,在最開始,所有位置的信號都為0。

假設一個由0變1的信號需要通過前面的組合邏輯,首先D觸發器1前面一段由0變1,即圖中點a到點b變為1,這段時間在時序中如下圖中點a與點b的位置。

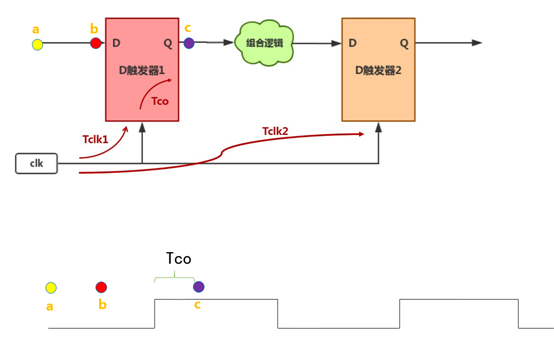

1)D觸發器傳輸延時

接著是D觸發器的傳輸延時,在時鐘上升沿處,信號1從D觸發器1后輸出,即下圖中信號從c點輸出,這段時間的延時在時序中為時鐘上升沿處到信號輸出的延時,即下面時序圖中Tco部分。

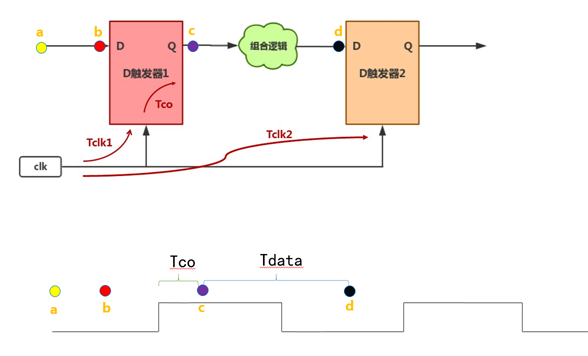

2)組合邏輯延時間

之后信號會通過組合邏輯,這段時間為組合邏輯的延時Tdata。如下圖所示,此信號由點c通過組合邏輯接著傳輸到點d,在時序圖中為Tdata部分。

3)建立時間

當然不要忘記我們前面講的D觸發器傳輸信號會有一段的建立時間,因此在時序中信號1會提前到達d點,即信號到達d點時,到達下一個時鐘上升沿還有一段時間,如下面時序圖中Tus部分所示。

當然像上圖中這樣信號到達d點的時間與建立時間相等的情況是比較理想的狀態,現實工程中大多數情況下信號1都會提前到達d點,等待建立時間的到來,即時間預量。實際的時序圖如下所示,可以看到信號達到d點的時間與D觸發器建立時間并不重合,中間會有一段時間預量,這才是實際工程中可以見到的情況。

以上就是由0變1的信號通過兩個D觸發器和一段組合邏輯的流程。在理想狀態下整個過程的延時與時間周期是相等的,但是實際情況下會有一定的變化,這時需要我們具體問題具體分析。

三、D觸發器在FPGA中的使用

1、FPGA的電路結構

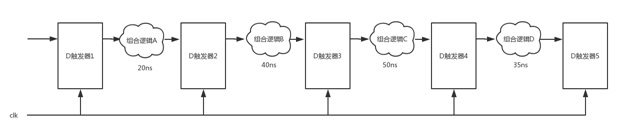

了解了兩個D觸發器的組合使用,下面學習FPGA的基本電路結構。

FPGA的基本電路結構如上圖所示。我們可以把電路分成兩個部分:D觸發器和組合邏輯。每兩個D觸發器之間,都會有或多或少的組合邏輯。組合邏輯可以是乘法器、加法器、RAM,甚至就是一條簡單的連線。前一個D觸發器的輸出端,經過組合邏輯運算后,給了下一個D觸發器的輸入端,等待時鐘上升沿的時候,再傳遞給D觸發器的輸出端。

上圖中,所有的D觸發器都統一受時鐘CLK的控制,都是在CLK的上升沿把輸入的值傳遞給輸出端。

FPGA中有4個組合邏輯A、B、C、D ,邏輯與邏輯之間,共使用了5個D觸發器傳輸數據。其中組合邏輯A持續20納秒,組合邏輯B持續40納秒,組合邏輯C持續50納秒,組合邏輯D持續35納秒。時鐘周期為100納秒,即上升沿100納秒產生一次;每個觸發器的建立時間為5納秒,保持時間為25納秒。

2、現實案例

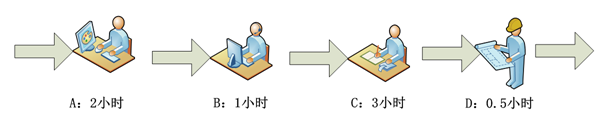

為了便于理解,我們用一個生活中的例子類比一下D觸發器與組合邏輯的關系。如下圖所示,現在有一個生產線生產一款產品,一共需要4個步驟,分別由員工ABCD來完成,其中A做完一個工序需要2小時,B需要1小時,C需要3小時,D是0.5小時。工廠統一規定每隔5個小時交接一次;為了避免交接混亂,要求交接點前5分鐘交接,交接點后10分鐘才能繼續工作。

此生產線就像是前面我們講到的FPGA電路結構,四個員工就相當于FPGA中四個組合邏輯,大家在同一個環境下工作,被同一個時鐘所支配,相互間又有著傳輸關系。

要求每5個小時交接一次相當于100納秒產生一次時鐘上升沿;每一位員工交接給下一位員工的這個過程就相當于D觸發器將輸入的值賦給輸出。

所有員工在交接點前5分鐘都停下手中工作,進入準備交接狀態,5分鐘相當于D觸發器的建立時間5納秒;交接點后10分鐘,大家依舊保持交接狀態,10分鐘相當于D觸發器的保持時間25納秒。

公司的規定必須提前5分鐘,等待10分鐘進行交接,就和D觸發器的硬件特性相同,交接時間是不能因為個人改變的;不論工作什么時候完成,在交接點前5分鐘一定要準備交接,交接點后保持交接狀態10分鐘才可以繼續工作,這樣才可以保證整個生產線可以流暢進行。

我們用了一個簡單的案例比較清晰的理解了D觸發器,通俗來說就是需要傳輸的數據等待在D觸發器前,D觸發器每個時鐘都會在門口進行檢測,檢測到了有效數據后,在此時鐘上升沿進行數據輸出。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1630文章

21796瀏覽量

605996 -

D觸發器

+關注

關注

3文章

164瀏覽量

48020 -

時序約束

+關注

關注

1文章

115瀏覽量

13457

發布評論請先 登錄

相關推薦

FPGA時序約束之衍生時鐘約束和時鐘分組約束

FPGA設計為什么要加時序約束?加時序約束有什么作用?

FPGA中的時序約束設計

時序約束系列之D觸發器原理和FPGA時序結構

時序約束系列之D觸發器原理和FPGA時序結構

評論