1、前言

FPGA端掛載DDR時(shí),對FPGA引腳的約束和選擇并不是隨意的,有一定的約束規(guī)則,一般可以通過利用vivado工具中的pin assignment去選擇合適的位置輔助原理圖設(shè)計(jì)。

2、DDR3約束規(guī)則

XILINX 7series FPGA支持高性能存儲(chǔ)接口,對于DDR來說分為數(shù)據(jù)(DQ,DQS,DM)和控制(地址和控制信號(hào))兩類引腳,在和FPGA互聯(lián)時(shí),DDR數(shù)據(jù)部分以字節(jié)組為單位,即每8個(gè)數(shù)據(jù)線和對應(yīng)的DQS和DM數(shù)據(jù)掩碼作為一組,對于64位DDR來說就有8個(gè)字節(jié)組。DDR控制部分不分組,可以任意接在同一的IO BANK內(nèi),但不能跨BANK放置。

FPGA的IO BANK有50 pins,劃分為4個(gè)區(qū)域(4*12)和2個(gè)VRN/VRP管腳,DDR字節(jié)組(8DQ+2DQS+1DM)需要放在FPGA bank 區(qū)域(12 pins)里,同一個(gè)區(qū)域內(nèi)除了DQS需要接在DQS位置,其余管腳可以在區(qū)域內(nèi)任意換位置,區(qū)域里多余的管腳可以用于接其他控制信號(hào)(除RAS_NCAS_NWE_NCS_NODT等)。

當(dāng)系統(tǒng)時(shí)鐘推薦放置在地址控制IO BANK內(nèi),并且應(yīng)當(dāng)放置在SRCCMRCCDQS等位置上,當(dāng)存在多個(gè)時(shí)鐘CK時(shí)應(yīng)該將其放置在同一字節(jié)區(qū)域內(nèi)

單個(gè)DDR接口不允許使用超過3個(gè)IO BANK,并且當(dāng)使用3個(gè)BANK時(shí),地址控制部分必須在中間BANK的位置,且不允許跨BANK分布。

VRN/VRP一般用作數(shù)控阻抗DCI,但是特殊情況下也可以用作地址控制管腳。

為了減小PCB設(shè)計(jì)復(fù)雜性,通常PCB布線時(shí)需要換pin以方便走線,減小布線交叉的情況,布線時(shí)允許換pin的原則有:

1、數(shù)據(jù)部分字節(jié)區(qū)域內(nèi)部可以任意換pin(除DQS專用引腳)

2、數(shù)據(jù)部分字節(jié)區(qū)域之間可以任意互換

3、地址控制部分可以在對應(yīng)bank 內(nèi)任意字節(jié)區(qū)域之內(nèi)或者之間進(jìn)行換pin,但是要保證CK信號(hào)放在srccmrccdqs等pn對上。

3、利用VIVADO輔助原理圖設(shè)計(jì)

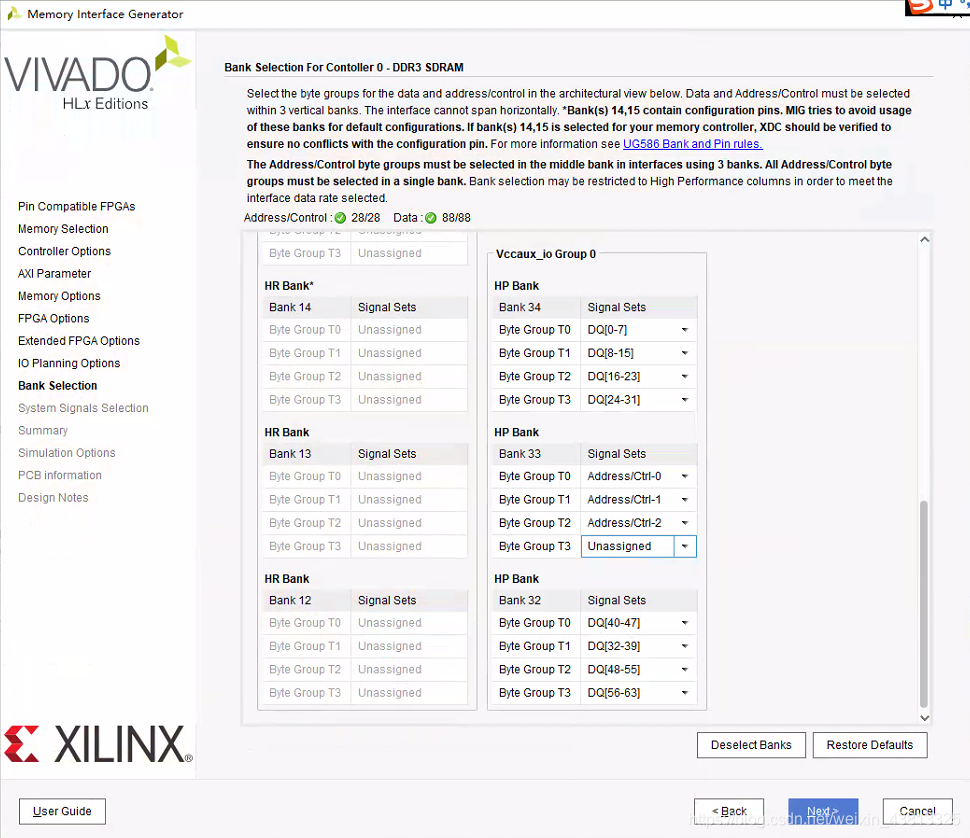

使用vivado IPCORE進(jìn)行設(shè)置時(shí)可以看到比較典型的64位DDR3的引腳分配。

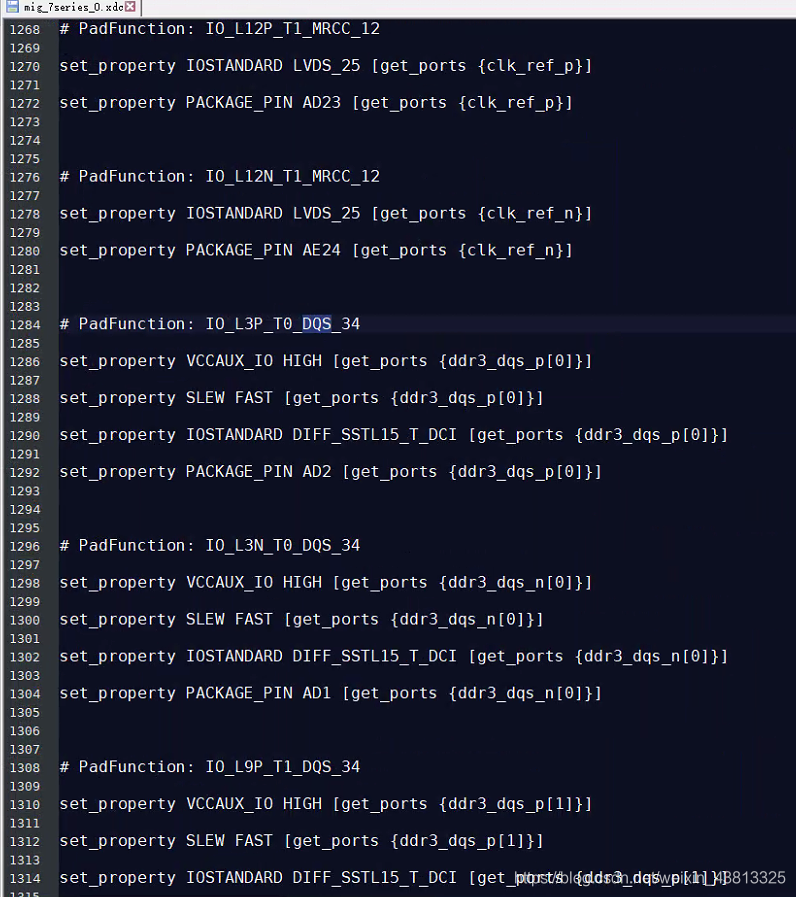

具體到管腳上的分配可以查看IP CORE的XDC約束文件看到,根據(jù)約束去輔助原理圖設(shè)計(jì),保證設(shè)計(jì)可用性。

3、DDR3 IP核時(shí)鐘需求

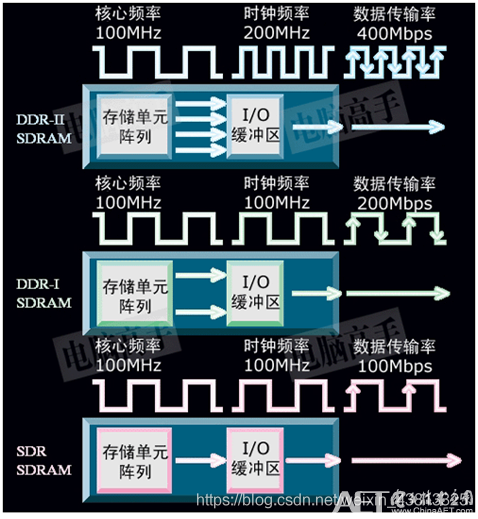

首先了解DDR的工作時(shí)鐘和內(nèi)核時(shí)鐘與數(shù)據(jù)速率的關(guān)系。下圖可知工作時(shí)鐘=數(shù)據(jù)速率/2,(因?yàn)镈DR在時(shí)鐘上下降沿都采樣數(shù)據(jù)),內(nèi)核時(shí)鐘=數(shù)據(jù)速率/8(數(shù)據(jù)預(yù)取bit為8),因此工作時(shí)鐘和內(nèi)核時(shí)鐘之間的關(guān)系就是4:1的關(guān)系,如果是數(shù)據(jù)速率為1600M的DDR3,工作時(shí)鐘應(yīng)該是800M,用戶時(shí)鐘為200M,同時(shí)系統(tǒng)還需要一個(gè)200M固定參考時(shí)鐘用于延時(shí)調(diào)整,這幾個(gè)時(shí)鐘通常利用輸入系統(tǒng)參考時(shí)鐘(外部晶振參考時(shí)鐘或者內(nèi)部PLL輸出時(shí)鐘)經(jīng)過DDR內(nèi)部PLL鎖出工作時(shí)鐘、用戶時(shí)鐘、參考時(shí)鐘。

?

原文標(biāo)題:XILINX 7series FPGA掛載DDR3之引腳約束

文章出處:【微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605999 -

DDR3

+關(guān)注

關(guān)注

2文章

276瀏覽量

42389 -

Xilinx

+關(guān)注

關(guān)注

71文章

2171瀏覽量

122134 -

時(shí)鐘

+關(guān)注

關(guān)注

11文章

1746瀏覽量

131799 -

IP核

+關(guān)注

關(guān)注

4文章

331瀏覽量

49635

原文標(biāo)題:XILINX 7series FPGA掛載DDR3之引腳約束

文章出處:【微信號(hào):gh_9d70b445f494,微信公眾號(hào):FPGA設(shè)計(jì)論壇】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

DDR3 SDRAM控制器IP核的寫命令和寫數(shù)據(jù)間關(guān)系講解

cyclone V控制DDR3的讀寫,quartusII配置DDR3 ip核后,如何調(diào)用實(shí)現(xiàn)DDR3的讀寫呢,謝謝

如何使用IP核生成的xdc文件?

DDR3存儲(chǔ)器接口控制器IP助力數(shù)據(jù)處理應(yīng)用

Xilinx:K7 DDR3 IP核配置教程

紫光同創(chuàng)FPGA入門指導(dǎo):DDR3 讀寫——紫光盤古系列50K開發(fā)板實(shí)驗(yàn)教程

紫光同創(chuàng)FPGA入門指導(dǎo):DDR3 讀寫——紫光盤古系列50K開發(fā)板實(shí)驗(yàn)教程

xilinx平臺(tái)DDR3設(shè)計(jì)教程之仿真篇_中文版教程

DDR3 SDRAM的IP核調(diào)取流程

lattice DDR3 IP核的生成及調(diào)用過程

Gowin DDR3 Memory Interface IP用戶指南

FPGA學(xué)習(xí)-DDR3

基于AXI總線的DDR3讀寫測試

DDR3約束規(guī)則與IP核時(shí)鐘需求

DDR3約束規(guī)則與IP核時(shí)鐘需求

評論