Versal 自適應計算加速平臺( ACAP )將標量引擎( Scalar Engine )、自適應引擎( Adaptable Engine )和智能引擎( Intelligent Engine )與領先的存儲器和交互技術有機結合,從而為任何應用提供強大的異構加速功能。最重要的是,Versal ACAP 硬件和軟件是專為數據科學家和軟硬件開發者開展編程和優化工作而提供的。Versal ACAP 受到諸多工 具、軟件、資源庫、IP、中間件和框架的廣泛支持,適用于所有業界標準的設計流程。

本文檔涵蓋了以下設計進程:系統和解決方案規劃,即確認系統級別的組件、性能、I/O 和數據傳輸要求,包括解決方案到 PS、PL 和 AI 引擎的應用映射。同時,本指南旨在提供 Versal ACAP 的高層次綜述,如下所示:

·第 2 章:系統架構:提供 Versal ACAP 概述,包含每個高層次集成塊的摘要,其中包括每個塊的用途以及彼此之間的關聯。

·第 3 章:系統規劃:描述每個 Versal 器件系列與不同系統設計類型和設計流程之間的關聯。

·第 4 章:設計流程:描述賽靈思設計工具和支持用于 Versal ACAP 的設計流程。

·第 5 章:系統移植:為以 Versal ACAP 為目標的設計提供高層次系統移植建議以及每個塊的移植信息。

由于篇幅有限,本文僅節選了部分關于系統規劃的內容。如果您希望查閱完本設計指南的其他內容,請至文末點擊鏈接下載完整版。

系統規劃

要正確規劃系統,您必須根據自己的目標應用或系統設計類型明確系統要求。其中包括識別具有正確特性(例如, DDRMC IP 數量、AI 引擎等)的相應 Versal 器件。

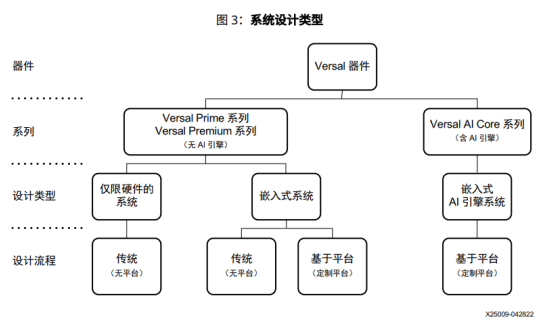

系統設計類型

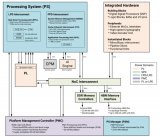

Versal ACAP 屬于異構計算平臺,具有多個計算引擎。在 Versal ACAP 上可映射各種應用,包括對無線系統、機器學習推斷和視頻處理算法進行信號處理。除了多個計算引擎外,Versal ACAP 還可使用高速串行 I/O、片上網絡( NoC )、DDR4/LPDDR4 存儲器控制器和多重速率以太網媒體訪問控制器( MRMAC )來提供超高系統帶寬。Versal 器件分類為 Versal Prime 系列、Premium 系列和 AI Core 系列。下圖顯示了每種 Versal 器件系列所支持的不同系統設計類型和設計流程。

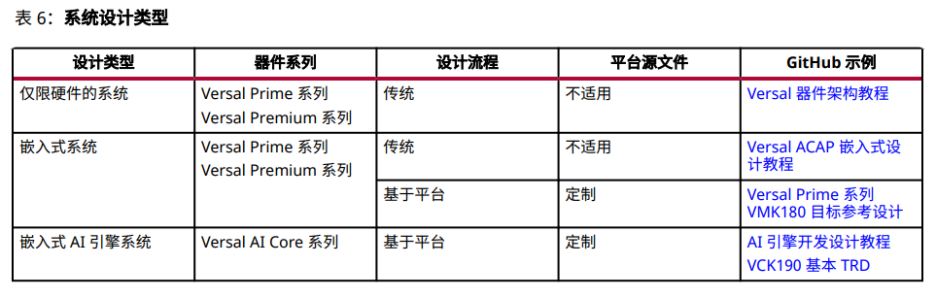

下表顯示了每種 Versal 器件系列所支持的系統設計類型和設計流程。如該表中所示,大部分設計流程都以構建平臺為基礎。

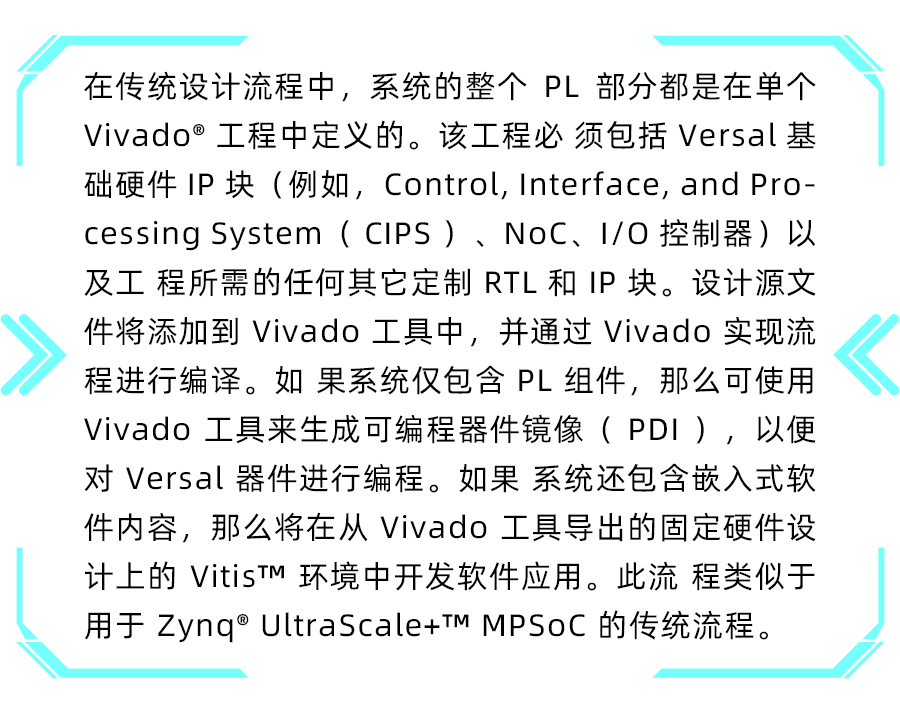

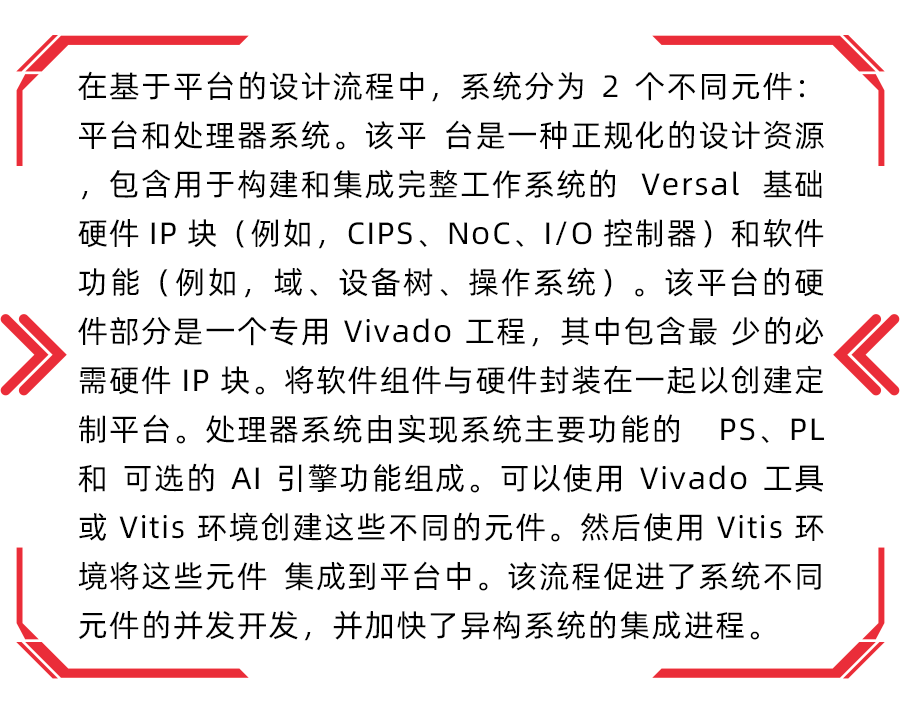

點擊對應圖片查看詳細內容

在設計流程中使用 Vitis 環境

Vitis 環境由工具、庫和 IP 組成,支持您對 Versal ACAP 應用的不同要素進行編程、運行和調試,包括AI 引擎內核與圖、可編程邏輯( PL )函數以及處理器系統( PS )上運行的軟件應用。Vitis 工具使用基于平臺的方法,其中系統按概念分為以下要素,這些要素可并行開發和測試:

平臺

自適應子系統

軟件應用

Vitis 環境設計方法論

要求:開始開發前,您必須選擇最適合您的應用的 Versal 器件,然后根據應用要求按功能目標(PS、AI 引擎和 PL)對設計進行分區。在此情況下,您必須了解:

系統設計注意事項,例如吞吐量和時延

域功能以及域間功能,包括計算和帶寬

整個系統和各子系統中的數據流和控制流程

此外,您必須注意平臺的目標類型。您必須規劃并設計開發板上的外設和接口以及定制開發板上可用的存儲器資源。

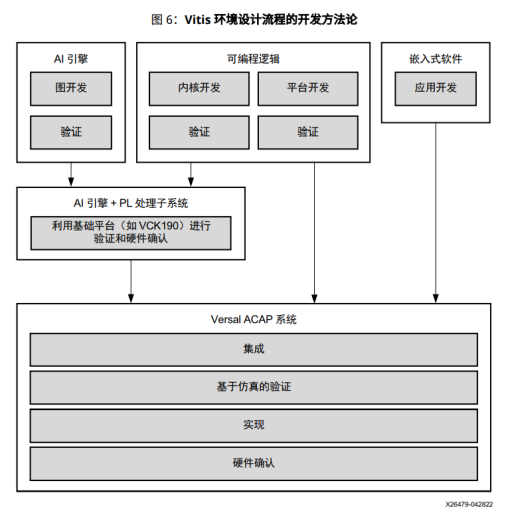

方法論概述:下圖顯示了基于 Vitis 環境設計流程的開發方法論的高層次表示法。

Vitis 環境開發方法論反應了 Versal ACAP 系統的異構性質,此類系統通常是由 PS、PL 和 AI 引擎功能組成的。您可使用 Vitis 工具來獨立開發并驗證這些組件,并逐漸將其加以集成以構成最終系統。

Vitis 環境設計流程是迭代性流程,可能多次循環執行每個步驟,并通過后續迭代來向自適應系統添加更多層級或元件。各團隊可以快速迭代早期步驟,將更多時間用于后續步驟,以便提供更詳細的性能數據。

最佳實踐:Vitis 環境設計方法論的基礎是迭代方法和并行開發。因此,強烈建議您采用如下最佳實踐:

并行開發自適應子系統和定制平臺。

對系統進行精確分區,即上述兩個要素可各自單獨開發和驗證,從而節省時間和精力。

單獨調試并驗證 AI 引擎圖和每個 PL 內核,然后再進行集成。

采用此方法可以盡可能提升在集成階段快速融合的可能性。已知所有組件都正確無誤的前提下,集成問題的調試難度大大降低。

使用標準AMD賽靈思平臺(例如,VCK190)來集成并驗證由 AI 引擎圖和 PL 內核組成的自適應子系統,然后再將目標瞄準定制平臺。

AMD 賽靈思平臺都經過預驗證,可立即部署到硬件上。通過使用標準 AMD 賽靈思平臺,AI 引擎圖和 PL 內核的開發者即可使 用仿真或硬件開發板來驗證自適應子系統,同時可以避免定制平臺的不確定性和復雜性。

確保在流程每個階段都能滿足性能目標。

在硬件中運行完整系統與在隔離環境中對個別組件進行仿真相比,性能結果并無明顯改善。因此,有必要在流程中盡早對任何性能問題進行完整檢查和調試。在組件級別確保滿足性能目標難度遠低于在包含所有組件間交互的復雜系統環境內滿足性能目標。

審核編輯 :李倩

-

Versal

+關注

關注

1文章

163瀏覽量

7712 -

ACAP

+關注

關注

1文章

54瀏覽量

8197

原文標題:Versal ACAP 設計指南

文章出處:【微信號:賽靈思,微信公眾號:Xilinx賽靈思官微】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

北大攜智元機器?團隊提出OmniManip架構

《大話芯片制造》閱讀體會分享_1

使用 AMD Versal AI 引擎釋放 DSP 計算的潛力

使用AMD Versal AI引擎加速高性能DSP應用

ALINX VERSAL SOM產品介紹

一個更適合工程師和研究僧的FPGA提升課程

各類常用混頻器的高層次設計和優缺點

贛江新區黨工委專職副書記羅進走訪慰問我司高層次人才駱建輝!

AMD發布第二代Versal自適應SoC,AI嵌入式領域再提速

在Vivado中構建AMD Versal可擴展嵌入式平臺示例設計流程

AMD Versal AI Edge自適應計算加速平臺之PL LED實驗(3)

AMD Versal AI Edge自適應計算加速平臺PL LED實驗(3)

【ALINX 技術分享】AMD Versal AI Edge 自適應計算加速平臺之 Versal 介紹(2)

AMD Versal AI Edge自適應計算加速平臺之Versal介紹(2)

Versal ACAP的高層次綜述

Versal ACAP的高層次綜述

評論