引言

我們華林科納討論了一種高速率各向異性蝕刻工藝,適用于等離子體一次蝕刻一個晶片。結果表明,蝕刻速率主要取決于Cl濃度,而與用于驅動放電的rf功率無關。幾種添加劑用于控制蝕刻過程。加入BCl以開始蝕刻,加入CHCI以控制各向異性。大量的氦有助于光致抗蝕劑的保存。已經進行了支持添加劑作用的參數研究。

高速率各向異性等離子體蝕刻工藝對于提高加工VLSI晶片器件的機器的效率非常重要。這篇論文描述了這樣一種用于以高速率(> 5000埃/分鐘)蝕刻鋁的工藝,并且沒有底切,甚至沒有過蝕刻。先前已經報道了使用許多含氯化合物的等離子體在平行板反應器中對鋁進行各向異性蝕刻的工藝,包括CCL、bcl和CU/BCS混合物(1-7)。然而,據報道,這些蝕刻工藝都沒有同時具有高蝕刻速率(> 2500/min)和在過蝕刻過程中沒有底切。

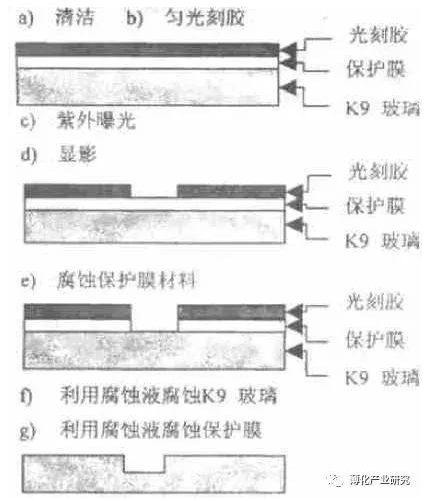

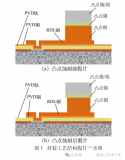

鋁的蝕刻似乎包括兩個過程:天然氧化鋁層的去除和鋁的蝕刻。據報道,使用BCS有助于去除氧化層,但是單獨使用BCS蝕刻鋁相對較慢。然而,銅和BCS的混合物:發現以高速率(1.2 p/min)蝕刻鋁,但各向同性。各向異性蝕刻可以用這種混合物在高蝕刻速率(4000埃/分鐘)下實現,然而,在這種情況下,在過蝕刻期間通常會導致底切。通過添加CHC/3等物質,各向異性蝕刻是可能的。這種添加被認為以類似于用CCLi蝕刻的方式保護側壁,其中觀察到鋁的各向異性蝕刻與在蝕刻的鋁邊緣上形成薄膜相關。在其他系統中也提出了類似的側壁保護促進各向異性的建議。

結果

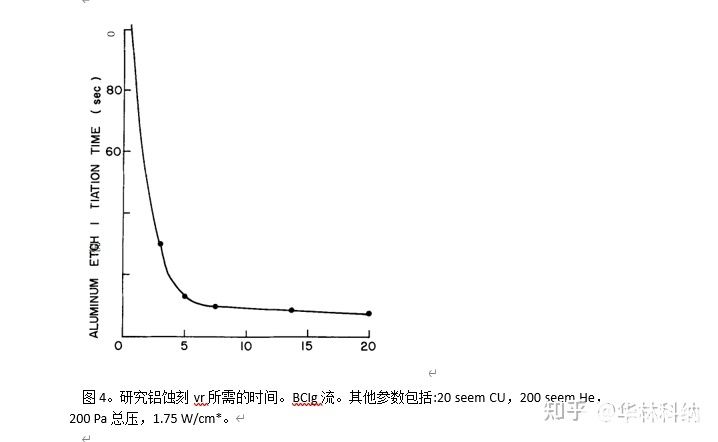

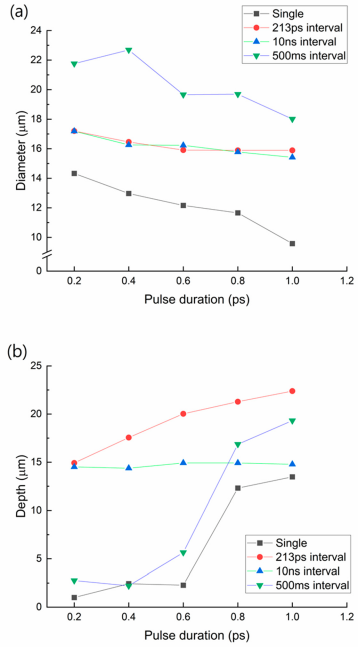

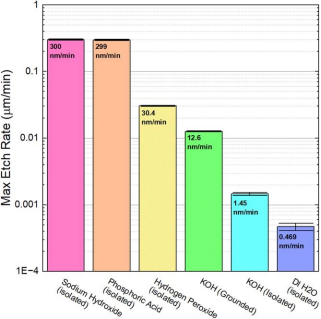

鋁蝕刻速率的測量是作為銅流速的函數進行的,銅流速隨著幾個工藝參數的變化而變化:BClz流速、CHC5流速和功率水平。觀察到蝕刻速率在較低流速下強烈依賴于CU流速,而在可能發生飽和的較高流速下較弱依賴于CU流速。蝕刻速率對其他工藝參數的依賴性要弱得多。蝕刻速率隨著CHC13流速的增加而略微降低,并且與BC*3流速無關。在低流速下,啟動時間對bcl有很強的依賴性;然而,在中等流速下,啟動時間與流速無關。在暴露于不含BC13的銅放電5分鐘后,沒有觀察到鋁蝕刻的開始。蝕刻速率基本上不依賴于rf功率,這與之前使用CCLt (3)的觀察結果一致。在開始后,觀察到在BC/3/CU的未稀釋混合物中,蝕刻以與放電大致相同的蝕刻速率在大至一半的區域上繼續進行,而沒有放電。在沒有排放物存在的情況下,從未觀察到整個器皿變干凈。這種影響沒有詳細研究,將在本文后面討論。使用鋼電極或鋁電極觀察到的蝕刻速率也沒有實質性差異。

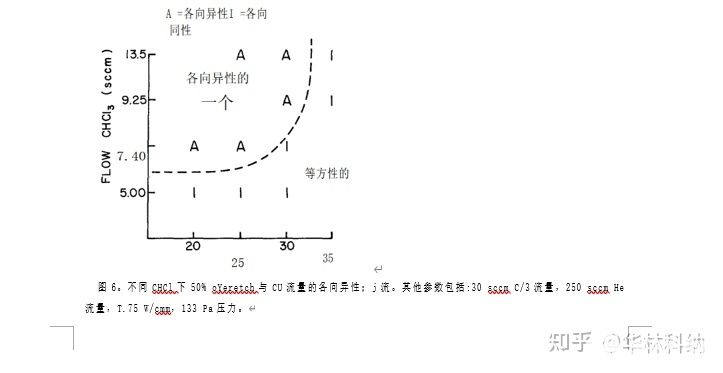

隨著CHC1、流速和r1功率的變化,測量作為CU流速的函數的各向異性

所有其他工藝參數保持不變。在每個研究中,觀察流速和功率的閾值,高于該閾值將獲得垂直剖面,但低于該閾值將發生底切。此外,當功率和CHC13流量增加到該閾值以上時,可以在較高的C/2流量下獲得垂直剖面。恒定功率下電極間距的減小增加了各向同性,其方式類似于隨著功率增加(恒定電極間距)所看到的;這表明體積功率密度很重要。對于大量的CHCI,放電是不穩定的,具有高強度的局部區域。從一個電極延伸到另一個電極的這些區域占據了大約19%的電極面積,并且發射強度是周圍等離子體的10倍。

討論

本文的結果支持了銅等離子體對鋁的腐蝕是一種無離子增強的化學反應的觀點。這種模型將解釋蝕刻速率對rf功率的不敏感性,RF功率影響離子能量和離子通量。這種純化學反應的概念與在超高真空條件下用銅放電束(11)進行的單獨工作是一致的。在該工作中,發現蝕刻速率不僅與o:I離子流量和能量無關,而且與放電的存在無關。然而,需要放電來啟動蝕刻,大概是通過去除天然氧化鋁表面層。沒有明確的化學物種鑒定負責:自發反應已經在這項工作中。然而,蝕刻速率對銅流量的過度依賴和對射頻功率的不敏感性。

審核編輯:符乾江

-

蝕刻

+關注

關注

9文章

419瀏覽量

15508 -

材料科學

+關注

關注

0文章

13瀏覽量

7568

發布評論請先 登錄

相關推薦

蝕刻基礎知識

半導體濕法刻蝕殘留物的原理

芯片濕法蝕刻工藝

芯片濕法刻蝕殘留物去除方法

濕法蝕刻的發展

玻璃基電路板的蝕刻和側蝕技術

玻璃電路板表面微蝕刻工藝

基于光譜共焦技術的PCB蝕刻檢測

利用貝塞爾光束、超短雙脈沖激光和選擇性化學蝕刻研究玻璃通孔(TGV)

通信——通過表面電荷操縱控制鍺的蝕刻

關于兩種蝕刻方式介紹

影響pcb蝕刻性能的五大因素有哪些?

電偶腐蝕對先進封裝銅蝕刻工藝的影響

金屬蝕刻殘留物對蝕刻均勻性的影響

金屬蝕刻殘留物對蝕刻均勻性的影響

評論