今天的許多設計都包括三個不同值(10uF/1uF/100nF)的去耦電容器,或者當只使用一個電容器時,可以使用 0.1 uF 這樣的小值。是時候重新考慮這些過時的遺留設計指南了。

作為遺留問題的神話

從一開始,電子行業就被更快、更小、更便宜、現在的四種力量拉向未來。這推動了技術、材料、制造和設計方面的革命性和進化性發展的不斷進步。

有時,我們在上一代采用的設計原則在下一代變成“遺留代碼”,不再適用。適用于一種互連技術組合的方法可能不適用于新的組合。遺留設計指南成為一個神話,應該重新評估。

唯一不變的是變化

我們的行業見證了從電子管、晶體管、集成電路到封裝系統的革命性進步。我們經歷了從離散布線到單層和雙層印刷電路板,再到多層板,再到 HDI 技術的革命性進步。

我們已經看到了從早期通孔器件(例如簡單的金屬罐封裝到 DIP 到大型針柵陣列)到帶引線框架的表面貼裝封裝到小型有機印刷電路基板到球柵陣列到芯片級封裝的革命性進步,以及多芯片模塊。。

圖 1顯示了四個具有代表性的技術代板和封裝的時間快照

圖1 四個時間快照。

從左到右:管子和分立線、管子和電路板、分立晶體管和電路板,以及帶有多層電路板的表面貼裝 BGA 封裝。

技術世代對設計的影響

信號如何與互連交互背后的基本原則沒有改變。它們仍然基于具有 150 年歷史的麥克斯韋方程組。然而,隨著每一代封裝和互連技術的發展,我們如何實施設計原則并將其轉化為設計指南已經發生了變化。

在使用離散布線的管子的早期,互連通常是透明的。當互連很重要時,首先要解決的問題通常是由于大環路電感引起的串擾。“越短越好”的設計原則以及捆綁在一起的電源線和地線很受歡迎。

當引入多層板時,這些遺留代碼中的一些繼續將電源和接地路由為離散線,而不是使用接地層。將電源和接地緊密捆綁在一起的傳統阻礙了一些早期設計中接地層的實施。

隨著時鐘頻率升至 20 MHz 以上,傳輸線效應開始占據主導地位,受控阻抗、布線拓撲和端接策略成為互連設計的重要驅動力。“越短越好”的遺留代碼導致人們不愿使用菊花鏈路由拓撲,這可能會導致路徑長度更長但反射噪聲更低。

當我們進入 1 Gbps 狀態時,損耗變得很重要,我們開始選擇除了常見的基于環氧玻璃的材料之外的其他材料,以降低損耗。當使用這些低損耗層壓板時,我們發現超過 5 Gbps 的銅損耗比預期的要高,我們發現更光滑的銅更好。超過 10 Gbps 時,我們發現 50 年前的玻璃纖維增強電路板制造方法導致了玻璃或纖維編織歪斜的新問題。

有了新技術,我們需要新的設計規則。高剝離強度、環氧樹脂玻璃電路板的舊規則不一定是千兆互連時代的最佳設計指南。

專家指南

我們每天在我們的電子產品中應用的設計指南是由行業領導者制定的。這些公司在信號完整性、電源完整性、EMC、材料、制造、可靠性和集成方面擁有專門的專家,他們正在推出最前沿的產品。這些專家應用基本原則為他們引入的新材料、IC 技術和互連技術建立設計指南。

但有時,在一代技術中起作用的東西在下一代中變成了神話。由于這些設計規則是由專家制定的,因此業界其他人有時不愿意放棄舊的設計指南,并繼續在可能不適用的新一代技術中使用它們。它們成為我們工具箱中根深蒂固的神話。

如果最后一個設計遵循這些舊的設計指南,人們通常認為這是因為設計指南,即使它可能不顧它們。有時遺留代碼是中性的,有時它有缺點。即使它是中立的,如果它阻止建立更好的設計指南,它也會變成負面的。它變成了一個即將被取代的神話。

設計指南神話,例如每個電源引腳使用三個不同的電容器進行去耦,這會降低下一代設計的性能,因此應始終重新評估。

高頻電容器

當安裝電感大于約 1 nH 時,一個簡單的串聯 RLC 電路可以很好地描述真實電容器的理想等效電路模型。當它低于 1 nH 時,會出現新的效果,真實電容器的傳輸線模型更匹配。

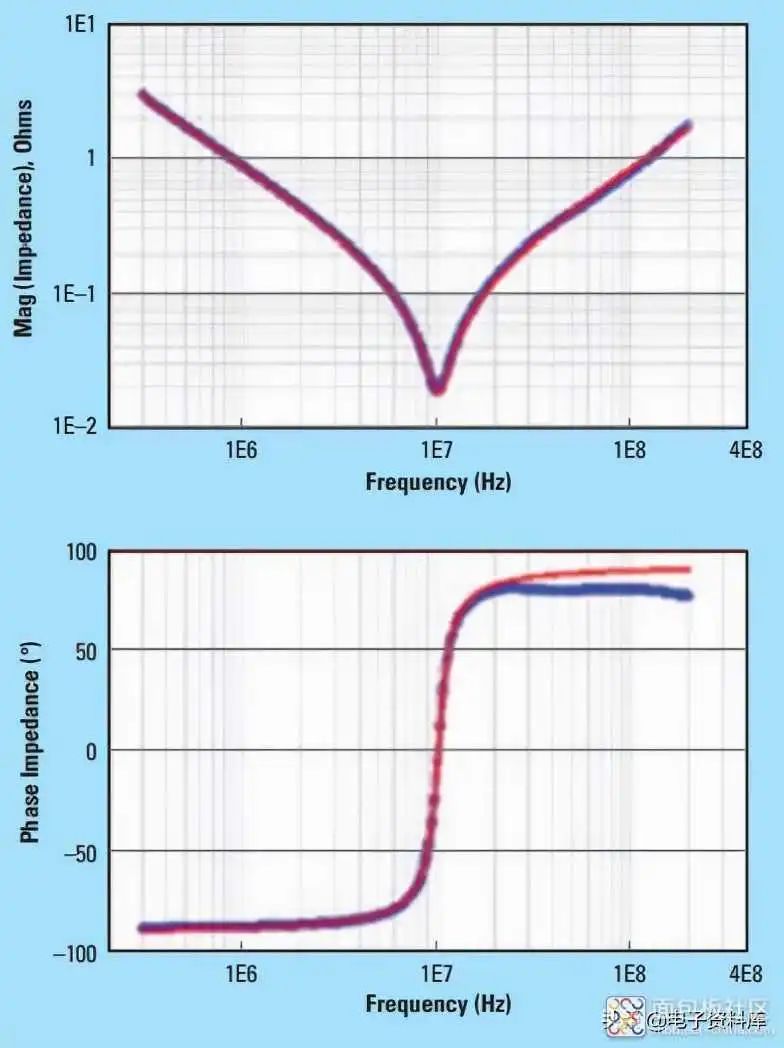

簡單的 RLC 模型適用于大多數代的電容器。圖 2顯示了實際 SMT、MLCC 電容器的測量阻抗和理想 RLC 串聯電路的模擬阻抗的示例 。

圖2 真實 SMT 電容器的測量阻抗(藍色)和相位以及簡單 RLC 電路模型的模擬阻抗(紅色)示例。

測量相位和模擬相位的差異表明實際電容器中的 ESR 行為不包括在簡單的 RLC 模型中。

該系列 RLC 電路模型是最簡單的模型,通常適用于電解、鉭、陶瓷、MLCC 電容器的技術范圍,無論是通孔還是表面貼裝。這只是一階模型,許多實際電容器可以與二階模型更好地匹配。但第一個模型提供了對這三個重要術語的作用的洞察。

理想的 C 對應于低頻下的阻抗行為。R 通常被稱為等效串聯電阻 (ESR)。這是由于實際電容器的引線、極板的金屬化,以及在較小程度上,電容器中的其他損耗機制。L 稱為等效串聯電感 (ESL)。這主要是由于電容器的內部結構及其電路板電源和接地路徑到它所連接的 IC 引腳。

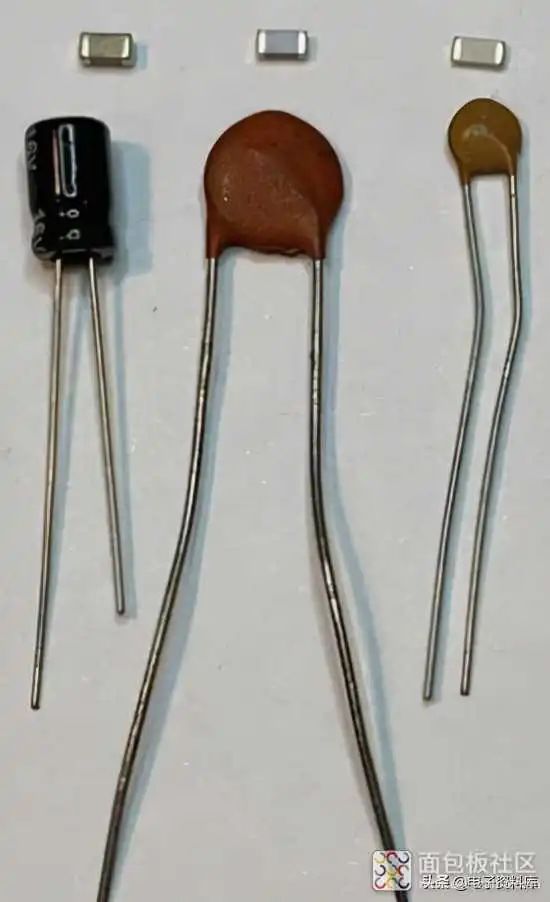

在通孔電容器時代,從 50 多年前開始,兩種常用的電容器技術是電解和陶瓷盤。這些示例如圖 3所示。

圖3 電解和陶瓷圓盤電容器的例子。

較小物理尺寸的電容器具有較小的電容、較小的 ESL 和較大的 ESR。

在電解電容器和陶瓷圓盤電容器技術中,可以在電容器中設計的電容數量與其物理尺寸和引線長度之間存在直接聯系。較大的電容值意味著較大的物理尺寸電容器。

因為 ESL 還取決于電容器的物理尺寸及其引線長度,所以較大值的電容器也具有較大的 ESL。例如,47 uF 電解電容器的 ESL 可能高達 30 nH,而小型 0.1 uF 圓盤電容器的 ESL 可能低至 7 nH。

甚至 ESR 也因電容器技術和尺寸而異。電解電容器的 ESR 可能在 0.1 到 5Ω 的量級。較小尺寸的電容器通常具有較高的 ESR。陶瓷圓盤電容器的 ESR 約為 0.1 至 1Ω。

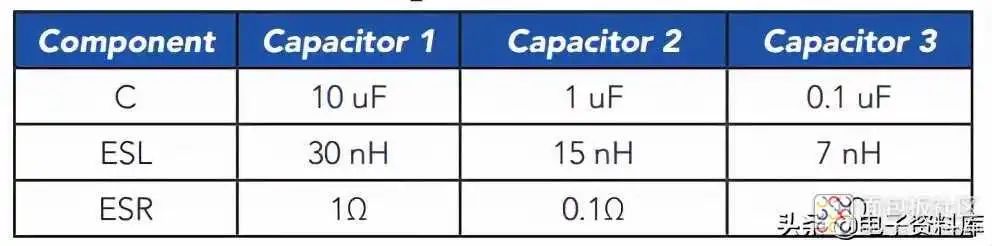

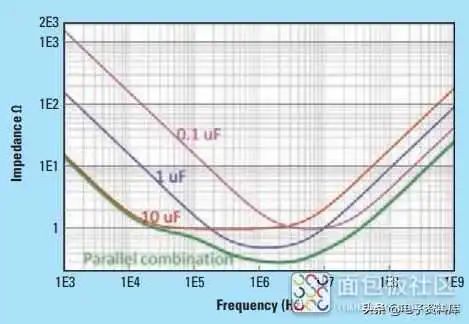

電容值和 ESL 之間的這種聯系極大地影響了大電容和小電容的阻抗分布。在低頻下,真實電容器的阻抗與其電容有關。在高頻下,真實電容器的阻抗大約是其引線電感。圖 4顯示了具有三種不同阻抗曲線的三種不同電容器的示例。他們的一階模型的組件值可能是:

圖4 這三個電容器的模擬阻抗曲線。最小值提供高頻下的低阻抗

對于帶引線的通孔電容器,通常正確的是,較小值的電容器尺寸較小,并且可以安裝較低的環路電感。這意味著它們在較高頻率下將具有較低的阻抗。在尋找高頻下阻抗低的通孔電容器時,應選擇小值和小尺寸的電容器。

這就是為什么小值電容器通常被稱為“高頻”電容器的原因。由于它們的引線較短,如果以低回路電感安裝到電路板上,它們在高頻時提供最低阻抗。

如果我們想要低頻時的最低阻抗以及高頻時的最低阻抗,通常的做法是并聯添加兩個或三個電容器。大容量電容器在低頻時提供低阻抗,而具有較低 ESL 的小容量電容器在高頻時提供低阻抗。并行組合充分利用了兩種配置的優點。

MLCC電容器與高頻電容器的神話

當我們改用基于MLCC表面貼裝技術的電容器時,電容器的特性與引線電容器有很大的不同。圖 5顯示了 1206 型 MLCC 電容器的示例,其電容值對應于相應陶瓷盤電容器中的相同電容。

圖5 個 1206 封裝的 MLCC 電容器(頂部)和相應值的陶瓷圓盤電容器。

通常,可以在完全相同的機身尺寸中獲得大范圍的電容值。0402 中的 10 uF 與 0.01 uF 一樣容易。這意味著 MLCC 電容器的 ESL 如果以最佳方式集成到電路板中,將與其電容值無關。

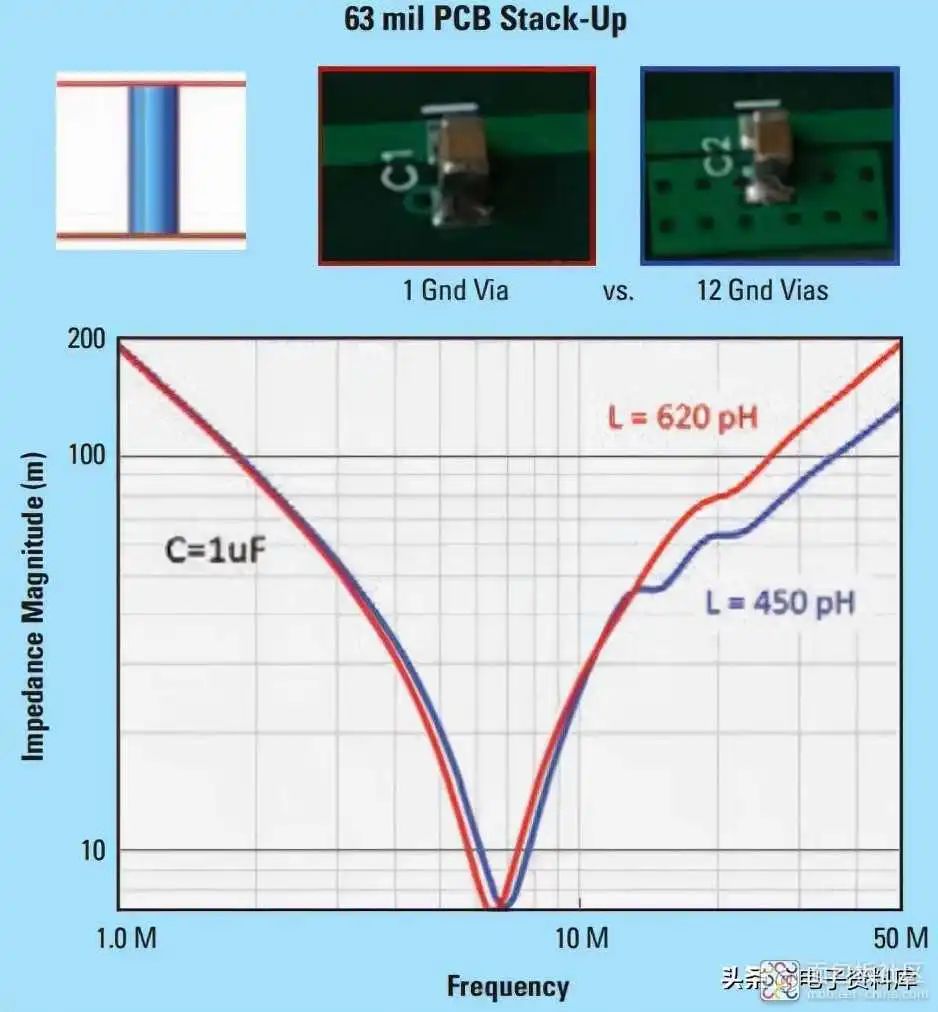

事實上,使用低環路電感設計,MLCC 的 ESL 可以設計為小于 1 nH,即使在兩層電路板上也是如此。圖 6顯示了在具有 0.620 nH ESL 的兩層 063 mil 厚板上測得的 1 uF MLCC 電容器的阻抗曲線示例 。

圖 6 電路板上 1 uF MLCC 電容器的測量阻抗曲線示例,電路板上的 ESL 為 0.620 nH。

這也表明當安裝電感小于 1 nH 時需要二階模型。測量由Picotest提供。

10 和 0.1 uF MLCC 電容器將具有完全相同的高頻阻抗。電容值較小的電容不再是“高頻”電容。事實上,一個 10 uF 的 MLCC 電容也將是一個“高頻”電容。

如果設計中具有低 ESL 的價值,則應始終使用 MLCC 電容器。即使是 10 uF MLCC 電容器,其 ESL 和“高頻”陶瓷圓盤電容器的阻抗也可能低于 10%。

在較舊的產品中,當使用通孔電容器時,較小的電容值具有較低的 ESL 和較高頻率下的較低阻抗。當電路板上的電源引腳上只有一個電容器的空間并且來自該引腳的瞬態電流很小時,指定了一個具有低電感的單個“高頻”電容器。這是一個低值電容,通常為 0.1 uF。

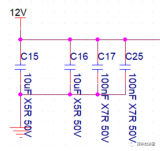

當一個引腳有三個電容器的空間時,通常會指定三個電容器值的范圍。與僅一個值電容器相比,這提供了在高頻下的較低阻抗和在低頻下的較低阻抗。圖 7是顯示這些常見規格的典型示意圖示例。

圖7 一個典型電路示例,顯示了具有三個不同電容值和一個小值單個電容的去耦網絡。

但是,此原理圖示例并非來自使用通孔部件和通孔電容器的舊設計,而是來自 120 MHz 前沿 Cortex M4 微控制器板,全部采用 MLCC 電容器設計和組裝。

高頻電容器的神話已經延續到這個設計中,因為它在許多其他設計中仍然指定一個小值電容器用作單個電容器和三個不同的值用于更高電流的引腳。

高頻電容器和使用三種不同電容器值的神話是許多現代設計中仍然存在的遺留代碼。

哪個更好?

那么,哪個更好:三個電容值相差十倍還是三個電容值相同?

不幸的是,只有具有所有元素的準確模型的系統級分析才有機會回答這個問題。

如果規范中的建議是使用三種不同值的電容器,那么編寫規范的工程師很有可能從未做過任何分析,而是使用了基于高頻電容器神話的 50 年歷史的設計指南。隨著 20 年前 MLCC 電容器的推出,該建議背后的理由消失了。懷疑 PDN 設計。

在這種情況下,您使用什么可能并不重要。盡管有電容值,您的產品也可能工作,但可能不是因為它們。

當三個具有相同ESL的不同值的電容器并聯組合時,在它們的自諧振頻率之間會產生兩個并聯諧振峰。峰值阻抗值與相鄰電容器的電容和電感以及電容器的ESR有關。

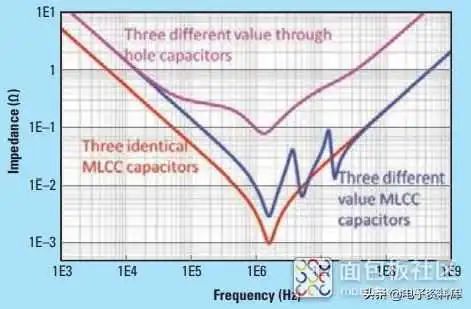

圖 8顯示了三個電容器的三種不同組合的模擬阻抗曲線。一種組合是建議在通孔技術中實現 10、1 和 0.1 uF。第二個是在 MLCC 電容器技術中實現的相同組合。第三種組合都是相同的 10 uF MLCC 電容器。MLCC 電容器的 ESL 為 1 nH。

圖 8 三個不同和三個相同 MLCC 電容器的模擬阻抗曲線。

與三個不同值的電容器相比,三個相同大值的電容器值可能會在整個頻譜上提供更低的阻抗(并且在中頻處沒有并聯諧振峰值),但這并不意味著它是一個更穩健的解決方案。

最后一個產品可能有效,但您可能不知道該設計有多健壯,或者某些無法追蹤、不可重現的故障是否可能是由于過度的開關噪聲以及恰到好處的數據模式收斂而導致的并聯諧振時的阻抗。

不要誤以為三個不同值的電容器是一種穩健的策略,或者三個電容器的值都相同更穩健。如果沒有系統級分析,它們都可能同樣可接受、同樣邊緣化或因相同故障而失敗。

“測試”質量

如果您不打算進行自己的系統級分析,請計劃實施徹底的測試計劃,以便您可以找到 PDN 中的薄弱環節并“測試質量”。

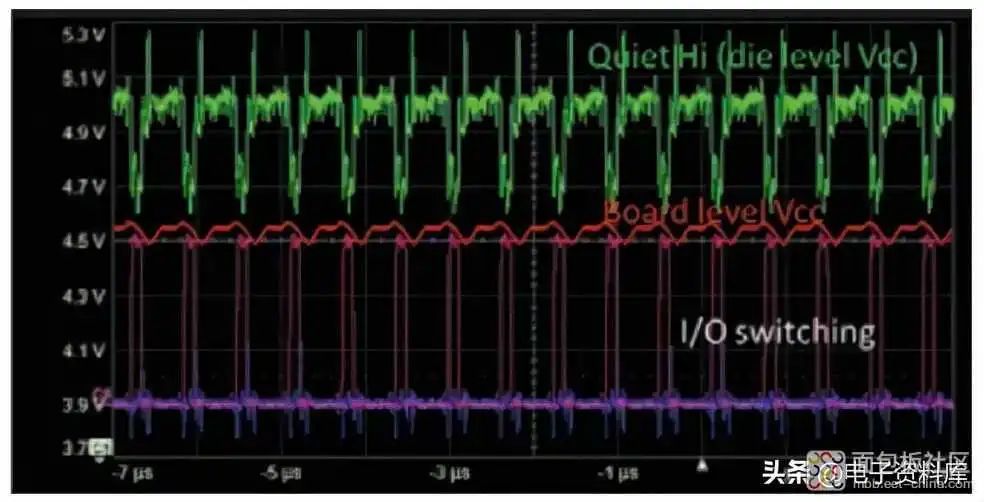

完整的測試計劃的一部分是為 PDN 中的測試進行設計。例如,使用高帶寬感測線表征噪聲(不僅在板級,而且在管芯的焊盤上)越好,您就越能夠將一種去耦策略與另一種去耦策略進行比較。圖 9是在 I/O 切換時在芯片電源軌和板級上測得的電壓噪聲示例。在 5 V 電壓軌上,片上電壓噪聲為 600 mV 峰峰值。板級電壓噪聲僅為 75 mV 峰峰值。

圖9 在芯片上相同的電源軌上測量的電壓噪聲是通過檢測線測量的,在電路板上,兩者的標度相同,均為 200 mV/div

無論應用如何,較低的安裝回路電感總是有價值的。這就是為什么 MLCC 去耦電容器應始終是放置在板上的第二個組件,因此它們可以以實際最低的安裝電感進行布線。

如果在一個引腳上只指定一個電容器,這是許多低電流應用的常見做法,那么在可接受的額定電壓下,始終使用允許的最大電容,以實現最小的實際尺寸。如果沒有系統級分析,這仍然不能保證產品的穩健性,因此必須制定全面的測試計劃。

設計質量:正確的去耦電容策略

使用三種不同值的去耦電容器是基于過時的假設,即小值電容器是“高頻”電容器。在我們的 MLCC 電容器時代,這個假設不適用,有什么更好的建議?不幸的是,答案是“視情況而定”。

但是,有一些適用于大多數系統的通用設計指南。

任何 PDN 的目標都是為那些需要它的組件提供直流電壓,并為應用提供可接受的噪聲水平。用于去耦的 MLCC 電容器只是良好 PDN 策略的一部分。

PDN 設計的基本原則之一是保持阻抗分布,如 IC 的焊盤所見,阻抗平坦且值可接受的低。這意味著通常通過增加更多電容來減少并聯諧振峰值,減少環路電感,并通過使用不同的電容值或通過受控的 ESR(這將降低峰值的 q 因子)來塑造阻抗曲線。

這有時會轉化為足夠的大容量電容,從而降低 VRM 大容量電容器的峰值。在高頻端,板級的平坦阻抗分布將有助于抑制片上電容和封裝引線電感并聯諧振峰值的班迪尼山。

選擇電容器值需要進行系統級分析,包括一端的 VRM 和另一端的消耗元件。當您設計所有安裝功能以盡可能減少電容器的環路電感時,使用 3D 仿真器和基于測量的建模工具為 PDN 元件開發準確的模型以仿真整個系統總是很有價值的。

VRM 的準確模型以及每個導軌和封裝引線電感的片上電容是設計穩健設計的整體分析的一部分。

當存在相當大的封裝去耦時,大容量電容器和 MLCC 電容器的低頻特性更為重要。當片上電容和封裝引線電感占主導地位時,從它們的并聯諧振中產生一個大的班迪尼山,從板級 MLCC 電容器產生的平坦阻抗分布中進行阻尼是很重要的。

不幸的是,除了使用受控 ESR 電容器之外,僅三個電容器值的組合不會為 Bandini Mountain 提供板級的任何阻尼。

這只是對真正進入優化的、具有成本效益的解耦策略的一些設計驅動力的一瞥。第一步是識別問題。第二步是確定問題的根本原因,第三步是確定提供可接受噪聲的整體 PDN 設計策略,其中優化的解耦策略只是其中的一部分。

當系統的目標阻抗差異超過六個數量級時,從許多物聯網應用中的超過 10Ω 到基于大型網絡處理器的產品中的小于 10 uOhms,沒有一種具有成本效益的策略,而是許多。

但這是一個不同章節的故事。

概括

使用三種不同電容器值的起源是基于使用通孔引線電容器。較小電容值的電容器通常在高頻下具有較低的 ESL 和較低的阻抗。對于通孔電容器,使用三種不同的電容器值具有性能優勢。

但是對于使用了 20 多年的 MLCC 電容器,這些陳舊的傳統設計指南不再適用。

當只指定一個或三個電容器用于去耦時,可能是因為沒有對設計進行分析。相反,在上一個設計中起作用的是在下一個設計中推薦的。盡管使用了三個不同的值,并且很有可能,該設計作品在使用所有三個相同的值時同樣有效。在這種情況下,您的設計的穩健性是“測試”而不是“設計”。

最好的方法是始終進行自己的分析,包括配電系統的其余部分,以及所有組件的準確模型(如果可用),因為它們正在安裝到您的系統中。

如果您的設計指定了三種不同的電容值,您可能會遵循已沿用 20 多年的傳統設計指南。可能是時候為您的下一個設計重新考慮該設計指南并進行自己的分析了。

審核編輯 :李倩

-

電容器

+關注

關注

64文章

6256瀏覽量

100250 -

去耦電容

+關注

關注

11文章

316瀏覽量

22474

原文標題:去耦電容 0.1 uF、10uF、1uF、100nF,現在還適用嗎?

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

三個不同值(10uF/1uF/100nF)的去耦電容器

三個不同值(10uF/1uF/100nF)的去耦電容器

評論