ZYNQ從放棄到入門(九)-PS和PL交互-DMA

我們上一節(jié)談到使用 DMA(直接內(nèi)存訪問(wèn))的好處已經(jīng)變得顯而易見。到了這一步,我們留下了人類長(zhǎng)期以來(lái)一直在思考的問(wèn)題:DMA到底是什么?

DMA介紹

在最基本的層面上,一旦處理器設(shè)置了傳輸,DMA 將數(shù)據(jù)傳入或傳出內(nèi)存而無(wú)需CPU干預(yù)。DMA 可以顯著提高系統(tǒng)性能,具體取決于所采用的方法。在我們更詳細(xì)地了解 Zynq DMA 之前,我想先解釋一些 DMA 控制器的通用原理。通常 DMA 控制器以以下三種模式之一運(yùn)行:

- Burst Mode突發(fā)模式 - 在一次連續(xù)操作中傳輸整個(gè)數(shù)據(jù)塊。在許多應(yīng)用中,突發(fā)模式傳輸時(shí)拒絕總線訪問(wèn)處理器。這種模式好與壞還是取決于系統(tǒng)。

- Cycle Stealing – 為了克服上訴的不足,DMA支持Cycle Stealing將單個(gè) DMA 字節(jié)或字傳輸與處理器訪問(wèn)系統(tǒng)總線交錯(cuò)運(yùn)行。

- 透明模式——最有效的模式。僅當(dāng)處理器執(zhí)行不需要訪問(wèn)系統(tǒng)總線的任務(wù)時(shí)才傳輸數(shù)據(jù)。

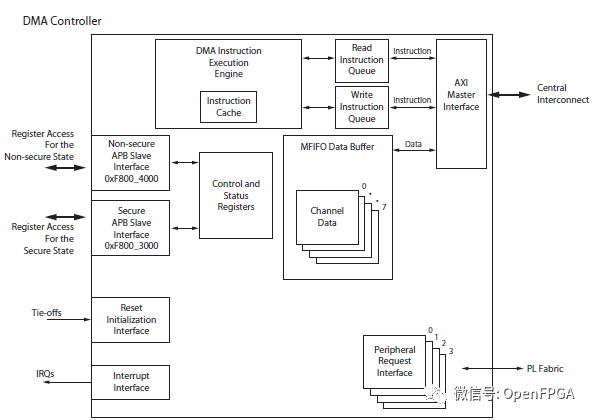

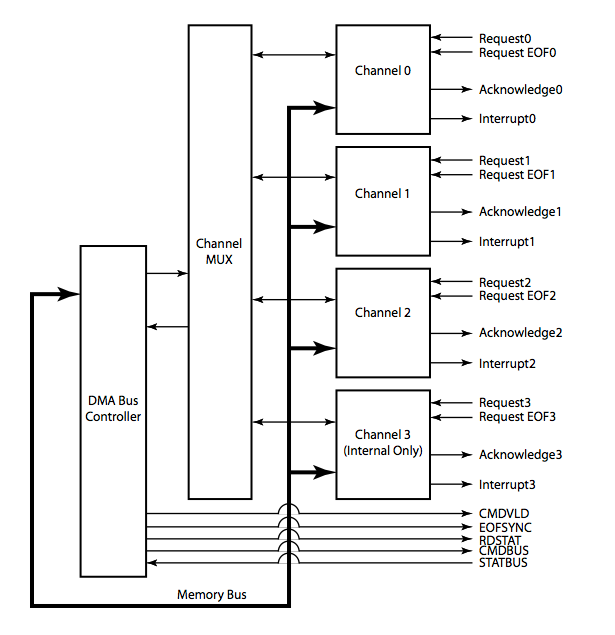

DMA 控制器的一項(xiàng)非常有用的功能是支持分散/收集(scatter/gather)操作的能力。此功能允許將多個(gè)數(shù)據(jù)源傳輸?shù)絾蝹€(gè)目標(biāo)地址或允許單個(gè)源地址提供多個(gè)輸出目標(biāo)(也稱為“緩沖區(qū)”)。Zynq SoC 的基于 ARM 的處理系統(tǒng) (PS) 有一個(gè) DMA 控制器 (DMAC),它連接到 Zynq 的 AXI4 互連并使用 AXI 總線執(zhí)行傳輸。DMAC 在系統(tǒng)存儲(chǔ)器和 Zynq 的可編程邏輯 (PL) 之間采用 64 位 AXI 傳輸。如下所示,Zynq DMAC 有 8 個(gè)通道,允許 DMAC 同時(shí)執(zhí)行 8 個(gè) DMA 線程,并通過(guò) AXI 互連實(shí)現(xiàn)流控制。

雖然 Zynq DMAC 允許在系統(tǒng)存儲(chǔ)器和 PL(包括 PL 中的 Zynq 外設(shè))之間進(jìn)行雙向傳輸,但它不支持 Zynq PS 中的外設(shè)的 DMA,因?yàn)檫@些外設(shè)沒有流控制信號(hào)來(lái)支持 DMA 操作。然而,Zynq SoC 中的一些 IO 外設(shè)具有自己的 DMA 控制器,以支持進(jìn)出 IOP 和系統(tǒng)內(nèi)存的高數(shù)據(jù)速率傳輸。這些外圍設(shè)備是:

- GigE Controller 千兆以太網(wǎng)控制器

- SDIO Controller SDIO 控制器

- USB Controller USB控制器

- Device Configuration Controller 設(shè)備配置控制器

如果設(shè)備使用 ARM TrustZone,Zynq SoC 還支持安全寄存器訪問(wèn)。Xilinx 同時(shí)也提供了一個(gè)簡(jiǎn)單的驅(qū)動(dòng)程序文件 (xdmaps.h),我們可以在獨(dú)立 BSP 中使用它來(lái)配置和啟動(dòng) DMA 傳輸。在下一節(jié)中,我們將了解如何使用此文件創(chuàng)建簡(jiǎn)單的 DMA 傳輸。

示例演示

本節(jié)創(chuàng)建一個(gè)非常簡(jiǎn)單的示例來(lái)演示如何設(shè)置和使用 DMA。

為了演示這示例,將使用一個(gè) DMA 控制器通道將一個(gè)內(nèi)存位置傳輸?shù)搅硪粋€(gè)內(nèi)存位置。

首先需要在BSP中包含一部分Vivado中生成的頭文件。這些頭文件提供了我們可以用來(lái)驅(qū)動(dòng) DMA 的宏和函數(shù)。對(duì)于這個(gè)例子,我們需要包括:

#include"xscugic.h"

#include"xdmaps.h"

#include"xil_exception.h"

Xscugic.h 和 xil_exceptions.h 允許使用中斷控制器,而 xdmaps.h 允許配置并使用DMA。

使用 xparamters.h 提供的參數(shù),我們可以定義 DMA 和中斷控制器的設(shè)備標(biāo)識(shí)、將使用的中斷以及我們將傳輸?shù)臄?shù)據(jù)長(zhǎng)度:

#defineDMA_DEVICE_IDXPAR_XDMAPS_1_DEVICE_ID

#defineINTC_DEVICE_IDXPAR_SCUGIC_SINGLE_DEVICE_ID

#defineDMA_FAULT_INTRXPAR_XDMAPS_0_FAULT_INTR

#defineDMA_DONE_INTR_0XPAR_XDMAPS_0_DONE_INTR_0

#defineDMA_LENGTH1024

開發(fā)的下一階段是編寫三個(gè)函數(shù)來(lái)配置DMA,配置中斷控制器,并在DMA傳輸完成時(shí)充當(dāng)中斷服務(wù)程序。

在 DMA 配置函數(shù)中,我們首先使用 xdmaps.h 提供的命令結(jié)構(gòu)創(chuàng)建一個(gè) DMA 命令。DMA 命令由通道控制、塊描述符、用戶定義的程序、指向生成的程序的指針和傳輸結(jié)果組成。由于這是一個(gè)簡(jiǎn)單的示例,我們不需要所有這些組件,但是我們將配置 DMA 控制器,如下所示:

DmaCmd.ChanCtrl.SrcBurstSize=4;

DmaCmd.ChanCtrl.SrcBurstLen=4;

DmaCmd.ChanCtrl.SrcInc=1;

DmaCmd.ChanCtrl.DstBurstSize=4;

DmaCmd.ChanCtrl.DstBurstLen=4;

DmaCmd.ChanCtrl.DstInc=1;

DmaCmd.BD.SrcAddr=(u32)Src;

DmaCmd.BD.DstAddr=(u32)Dst;

DmaCmd.BD.Length=DMA_LENGTH*sizeof(int);

下一步設(shè)置運(yùn)行中斷函數(shù)以將 DMA 中斷連接到中斷控制器之前初始化和配置 DMA 控制器:

DmaCfg=XDmaPs_LookupConfig(DeviceId);

XDmaPs_CfgInitialize(DmaInst,DmaCfg,DmaCfg->BaseAddress);

SetupInterrupt(&GicInstance,DmaInst);

在此之后,在我們連接完成處理程序并開始傳輸之前,源內(nèi)存位置被設(shè)置并清除目標(biāo)位置,為了跟蹤進(jìn)度,我們還調(diào)用了 DMA 進(jìn)度函數(shù):

DmaCfg=XDmaPs_LookupConfig(DeviceId);

XDmaPs_CfgInitialize(DmaInst,DmaCfg,DmaCfg->BaseAddress);

SetupInterrupt(&GicInstance,DmaInst);

XDmaPs_Print_DmaProg(&DmaCmd);

當(dāng)附加的源代碼文件在ZYNQ上運(yùn)行時(shí),以下結(jié)果顯示串口輸出上。

源碼:

https://gitee.com/openfpga/zynq-chronicles/blob/master/part_29.c

原文標(biāo)題:ZYNQ從放棄到入門(九)-DMA

文章出處:【微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

控制器

+關(guān)注

關(guān)注

112文章

16448瀏覽量

179481 -

dma

+關(guān)注

關(guān)注

3文章

566瀏覽量

100966 -

Zynq

+關(guān)注

關(guān)注

10文章

610瀏覽量

47298

原文標(biāo)題:ZYNQ從放棄到入門(九)-DMA

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

DMA控制器介紹

基于DMA控制器的UART串行通信設(shè)計(jì)

DMA控制器功能及特點(diǎn)

基于AMBA總線的DMA控制器IP核設(shè)計(jì)

基于PCI Core的鏈?zhǔn)?b class='flag-5'>DMA控制器設(shè)計(jì)

NiosⅡ系統(tǒng)中DMA控制器的原理及應(yīng)用

Crossbar的多通道DMA控制器設(shè)計(jì)

dma控制器芯片8257資料介紹

dma控制器由什么組成

dma控制器的組成

dma控制器是什么_dma控制器工作方式

ZNEO CPU 上的 DMA 控制器特性分析

DMA控制器原理詳解

請(qǐng)問(wèn)DMA控制器可以減輕CPU負(fù)擔(dān)嗎?

DMA控制器介紹及示例演示詳解

DMA控制器介紹及示例演示詳解

評(píng)論