本章通過概述CUDA編程模型是如何在c++中公開的,來介紹CUDA的主要概念。

NVIDIA GPU 架構(gòu)圍繞可擴(kuò)展的多線程流式多處理器 (SM: Streaming Multiprocessors) 陣列構(gòu)建。當(dāng)主機(jī) CPU 上的 CUDA 程序調(diào)用內(nèi)核網(wǎng)格時(shí),網(wǎng)格的塊被枚舉并分發(fā)到具有可用執(zhí)行能力的多處理器。一個(gè)線程塊的線程在一個(gè)SM上并發(fā)執(zhí)行,多個(gè)線程塊可以在一個(gè)SM上并發(fā)執(zhí)行。當(dāng)線程塊終止時(shí),新塊在空出的SM上啟動(dòng)。

SM旨在同時(shí)執(zhí)行數(shù)百個(gè)線程。為了管理如此大量的線程,它采用了一種稱為 SIMT(Single-Instruction, Multiple-Thread: 單指令,多線程)的獨(dú)特架構(gòu),在 SIMT 架構(gòu)中進(jìn)行了描述。這些指令是流水線的,利用單個(gè)線程內(nèi)的指令級(jí)并行性,以及通過同時(shí)硬件多線程處理的廣泛線程級(jí)并行性,如硬件多線程中詳述。與 CPU 內(nèi)核不同,它們是按順序發(fā)出的,沒有分支預(yù)測(cè)或推測(cè)執(zhí)行。

SIMT 架構(gòu)和硬件多線程描述了所有設(shè)備通用的流式多處理器的架構(gòu)特性。 Compute Capability 3.x、Compute Capability 5.x、Compute Capability 6.x 和 Compute Capability 7.x 分別為計(jì)算能力 3.x、5.x、6.x 和 7.x 的設(shè)備提供了詳細(xì)信息。

NVIDIA GPU 架構(gòu)使用 little-endian 表示。

4.1 SIMT 架構(gòu)

多處理器以 32 個(gè)并行線程組(稱為 warp)的形式創(chuàng)建、管理、調(diào)度和執(zhí)行線程。組成 warp 的各個(gè)線程一起從同一個(gè)程序地址開始,但它們有自己的指令地址計(jì)數(shù)器和寄存器狀態(tài),因此可以自由地分支和獨(dú)立執(zhí)行。warp一詞源于編織,這是第一個(gè)并行線程技術(shù)。半warp是warp的前半部分或后半部分。四分之一經(jīng)線是warp的第一、第二、第三或第四四分之一。

當(dāng)一個(gè)多處理器被賦予一個(gè)或多個(gè)線程塊來執(zhí)行時(shí),它將它們劃分為warp,并且每個(gè)warp都由warp調(diào)度程序調(diào)度以執(zhí)行。一個(gè)塊被分割成warp的方式總是一樣的;每個(gè)warp包含連續(xù)的線程,增加線程ID,第一個(gè)warp包含線程0。線程層次結(jié)構(gòu)描述了線程ID如何與塊中的線程索引相關(guān)。

一個(gè) warp 一次執(zhí)行一條公共指令,因此當(dāng)一個(gè) warp 的所有 32 個(gè)線程都同意它們的執(zhí)行路徑時(shí),就可以實(shí)現(xiàn)完全的效率。如果 warp 的線程通過依賴于數(shù)據(jù)的條件分支發(fā)散,則 warp 執(zhí)行所采用的每個(gè)分支路徑,禁用不在該路徑上的線程。分支分歧只發(fā)生在一個(gè)warp內(nèi);不同的 warp 獨(dú)立執(zhí)行,無論它們是執(zhí)行公共的還是不相交的代碼路徑。

SIMT 體系結(jié)構(gòu)類似于 SIMD(單指令多數(shù)據(jù))向量組織,其中單指令控制多個(gè)處理元素。一個(gè)關(guān)鍵區(qū)別是 SIMD 矢量組織向軟件公開了 SIMD 寬度,而 SIMT 指令指定單個(gè)線程的執(zhí)行和分支行為。與 SIMD 向量機(jī)相比,SIMT 使程序員能夠?yàn)楠?dú)立的標(biāo)量線程編寫線程級(jí)并行代碼,以及為協(xié)調(diào)線程編寫數(shù)據(jù)并行代碼。為了正確起見,程序員基本上可以忽略 SIMT 行為;但是,通過代碼很少需要warp中的線程發(fā)散,可以實(shí)現(xiàn)顯著的性能改進(jìn)。在實(shí)踐中,這類似于傳統(tǒng)代碼中緩存線的作用:在設(shè)計(jì)正確性時(shí)可以安全地忽略緩存線大小,但在設(shè)計(jì)峰值性能時(shí)必須在代碼結(jié)構(gòu)中考慮。另一方面,向量架構(gòu)需要軟件將負(fù)載合并到向量中并手動(dòng)管理分歧。

在 Volta 之前,warp 使用在 warp 中的所有 32 個(gè)線程之間共享的單個(gè)程序計(jì)數(shù)器以及指定 warp 的活動(dòng)線程的活動(dòng)掩碼。結(jié)果,來自不同區(qū)域或不同執(zhí)行狀態(tài)的同一warp的線程無法相互發(fā)送信號(hào)或交換數(shù)據(jù),并且需要細(xì)粒度共享由鎖或互斥鎖保護(hù)的數(shù)據(jù)的算法很容易導(dǎo)致死鎖,具體取決于來自哪個(gè)warp競(jìng)爭(zhēng)線程。

從 Volta 架構(gòu)開始,獨(dú)立線程調(diào)度允許線程之間的完全并發(fā),而不管 warp。使用獨(dú)立線程調(diào)度,GPU 維護(hù)每個(gè)線程的執(zhí)行狀態(tài),包括程序計(jì)數(shù)器和調(diào)用堆棧,并且可以在每個(gè)線程的粒度上產(chǎn)生執(zhí)行,以便更好地利用執(zhí)行資源或允許一個(gè)線程等待數(shù)據(jù)由他人生產(chǎn)。調(diào)度優(yōu)化器確定如何將來自同一個(gè) warp 的活動(dòng)線程組合成 SIMT 單元。這保留了與先前 NVIDIA GPU 一樣的 SIMT 執(zhí)行的高吞吐量,但具有更大的靈活性:線程現(xiàn)在可以在 sub-warp 粒度上發(fā)散和重新收斂。

如果開發(fā)人員對(duì)先前硬件架構(gòu)的 warp-synchronicity2 做出假設(shè),獨(dú)立線程調(diào)度可能會(huì)導(dǎo)致參與執(zhí)行代碼的線程集與預(yù)期的完全不同。特別是,應(yīng)重新訪問任何warp同步代碼(例如無同步、內(nèi)部warp減少),以確保與 Volta 及更高版本的兼容性。有關(guān)詳細(xì)信息,請(qǐng)參閱計(jì)算能力 7.x。

注意:

參與當(dāng)前指令的 warp 線程稱為活動(dòng)線程,而不在當(dāng)前指令上的線程是非活動(dòng)的(禁用)。線程可能由于多種原因而處于非活動(dòng)狀態(tài),包括比其 warp 的其他線程更早退出,采用與 warp 當(dāng)前執(zhí)行的分支路徑不同的分支路徑,或者是線程數(shù)不是線程數(shù)的塊的最后一個(gè)線程warp尺寸的倍數(shù)。

如果 warp 執(zhí)行的非原子指令為多個(gè) warp 的線程寫入全局或共享內(nèi)存中的同一位置,則該位置發(fā)生的序列化寫入次數(shù)取決于設(shè)備的計(jì)算能力(參見 Compute Capability 3.x、Compute Capability 5.x、Compute Capability 6.x 和 Compute Capability 7.x),哪個(gè)線程執(zhí)行最終寫入是未定義的。

如果一個(gè)由 warp 執(zhí)行的原子指令讀取、修改和寫入全局內(nèi)存中多個(gè)線程的同一位置,則對(duì)該位置的每次讀取/修改/寫入都會(huì)發(fā)生并且它們都被序列化,但是它們發(fā)生的順序是不確定的。

4.2 硬件多線程

多處理器處理的每個(gè) warp 的執(zhí)行上下文(程序計(jì)數(shù)器、寄存器等)在 warp 的整個(gè)生命周期內(nèi)都在芯片上維護(hù)。因此,從一個(gè)執(zhí)行上下文切換到另一個(gè)執(zhí)行上下文是沒有成本的,并且在每個(gè)指令發(fā)出時(shí),warp 調(diào)度程序都會(huì)選擇一個(gè)線程準(zhǔn)備好執(zhí)行其下一條指令(warp 的活動(dòng)線程)并將指令發(fā)布給這些線程。

特別是,每個(gè)多處理器都有一組 32 位寄存器,這些寄存器在 warp 之間進(jìn)行分區(qū),以及在線程塊之間進(jìn)行分區(qū)的并行數(shù)據(jù)緩存或共享內(nèi)存。

對(duì)于給定內(nèi)核,可以在多處理器上一起駐留和處理的塊和warp的數(shù)量取決于內(nèi)核使用的寄存器和共享內(nèi)存的數(shù)量以及多處理器上可用的寄存器和共享內(nèi)存的數(shù)量。每個(gè)多處理器也有最大數(shù)量的駐留塊和駐留warp的最大數(shù)量。這些限制以及多處理器上可用的寄存器數(shù)量和共享內(nèi)存是設(shè)備計(jì)算能力的函數(shù),在附錄計(jì)算能力中給出。如果每個(gè)多處理器沒有足夠的寄存器或共享內(nèi)存來處理至少一個(gè)塊,內(nèi)核將無法啟動(dòng)。

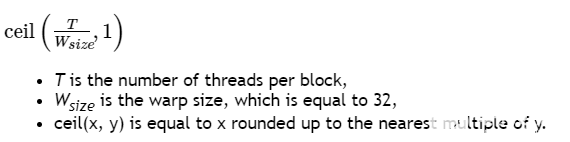

一個(gè)塊中的warp總數(shù)如下:

為塊分配的寄存器總數(shù)和共享內(nèi)存總量記錄在 CUDA 工具包中提供的 CUDA Occupancy Calculator中。

關(guān)于作者

Ken He 是 NVIDIA 企業(yè)級(jí)開發(fā)者社區(qū)經(jīng)理 & 高級(jí)講師,擁有多年的 GPU 和人工智能開發(fā)經(jīng)驗(yàn)。自 2017 年加入 NVIDIA 開發(fā)者社區(qū)以來,完成過上百場(chǎng)培訓(xùn),幫助上萬個(gè)開發(fā)者了解人工智能和 GPU 編程開發(fā)。在計(jì)算機(jī)視覺,高性能計(jì)算領(lǐng)域完成過多個(gè)獨(dú)立項(xiàng)目。并且,在機(jī)器人和無人機(jī)領(lǐng)域,有過豐富的研發(fā)經(jīng)驗(yàn)。對(duì)于圖像識(shí)別,目標(biāo)的檢測(cè)與跟蹤完成過多種解決方案。曾經(jīng)參與 GPU 版氣象模式GRAPES,是其主要研發(fā)者。

審核編輯:郭婷

-

機(jī)器人

+關(guān)注

關(guān)注

211文章

28646瀏覽量

208428 -

NVIDIA

+關(guān)注

關(guān)注

14文章

5076瀏覽量

103728 -

gpu

+關(guān)注

關(guān)注

28文章

4777瀏覽量

129360

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

Spire.XLS for C++組件說明

EE-112:模擬C++中的類實(shí)現(xiàn)

C++新手容易犯的十個(gè)編程錯(cuò)誤

C7000優(yōu)化C/C++編譯器

C++語言基礎(chǔ)知識(shí)

C++中實(shí)現(xiàn)類似instanceof的方法

FX2 CY7C68013A如何在C++環(huán)境中使用LoadEEPROM函數(shù)?

如何在FX3 SuperSpeed explorer等電路板上使用openOCD調(diào)試C++項(xiàng)目?

STM32CubeMX如何在*.c源文件中使用c++特性?

C/C++中兩種宏實(shí)現(xiàn)方式

鴻蒙OS開發(fā)實(shí)例:【Native C++】

使用 MISRA C++:2023? 避免基于范圍的 for 循環(huán)中的錯(cuò)誤

為什么很少用C++開發(fā)單片機(jī)

CUDA編程模型如何在c++實(shí)現(xiàn)

CUDA編程模型如何在c++實(shí)現(xiàn)

評(píng)論