本文由甄建勇翻譯。甄建勇,高級(jí)架構(gòu)師(某國(guó)際大廠),十年以上半導(dǎo)體從業(yè)經(jīng)驗(yàn)。主要研究領(lǐng)域:CPU/GPU/NPU架構(gòu)與微架構(gòu)設(shè)計(jì)。感興趣領(lǐng)域:經(jīng)濟(jì)學(xué)、心理學(xué)、哲學(xué)。

2022 年服務(wù)器行業(yè)的最大亮點(diǎn)之一將是 Compute Express Link ( CXL)。我們?cè)?2019 年首次宣布 CXL時(shí)就有媒體開始報(bào)道它。該項(xiàng)目已經(jīng)從英特爾內(nèi)部項(xiàng)目發(fā)展成了一個(gè)廣泛的行業(yè)聯(lián)盟,并且是我們進(jìn)入 2022 PCIe Gen5 時(shí)代時(shí)行業(yè)的發(fā)展方向。盡管如此,仍有許多人不太了解 CXL,因此我們將嘗試先使用一個(gè)簡(jiǎn)單的視頻來解釋 CXL:酸橙(Limes)。

視頻版由于我們將在未來幾年內(nèi)討論 CXL,因此我們提供了此作品的視頻版本,您可以在此處找到。

什么是CXL?

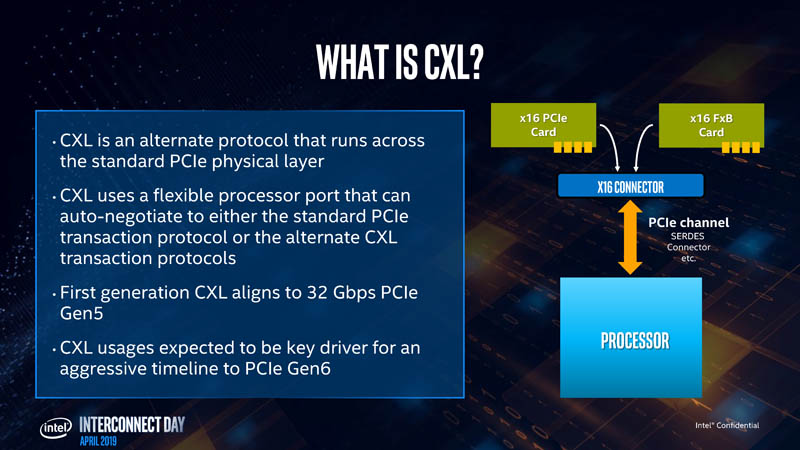

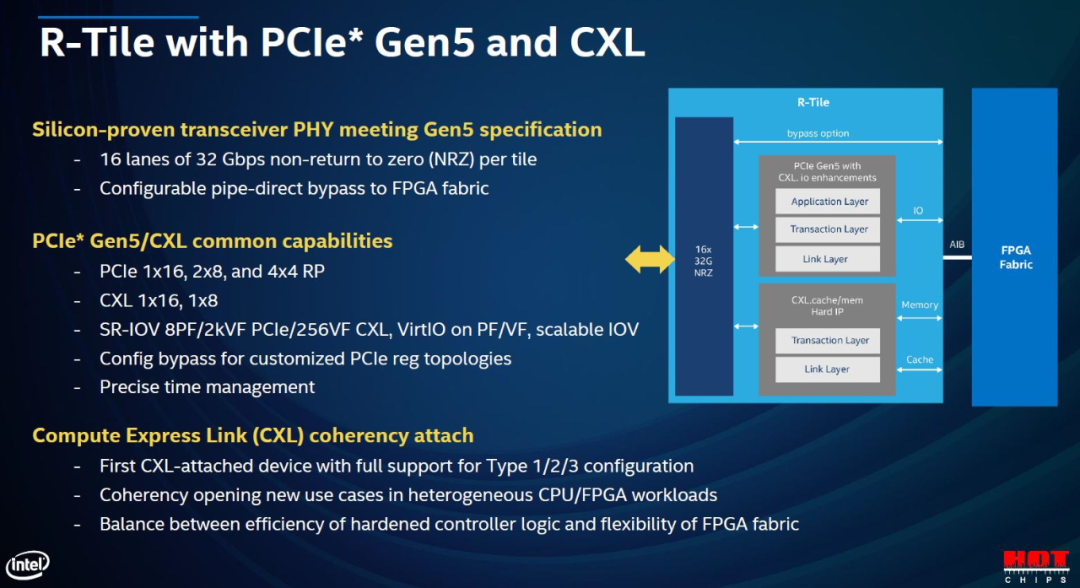

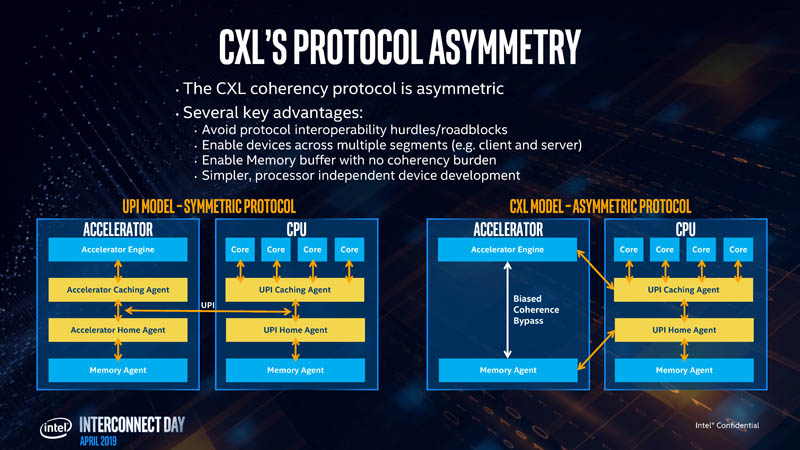

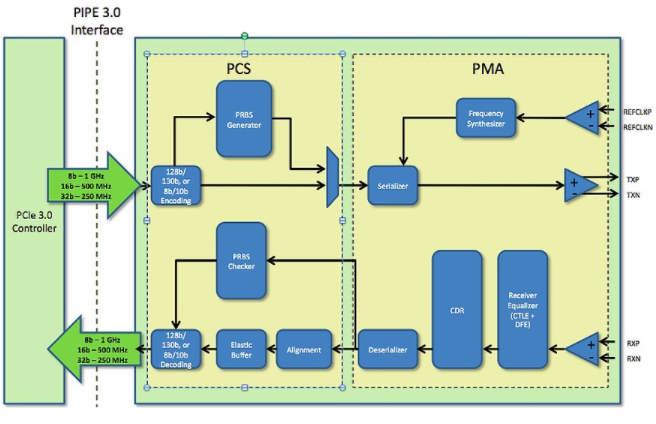

Compute Express Link 是一種緩存一致性互聯(lián),旨在幫助系統(tǒng)(尤其是具有加速器的系統(tǒng))更高效地運(yùn)行。CXL位于 PCIe Gen5鏈路基礎(chǔ)架構(gòu)之上。可以有 PCIe Gen5 設(shè)備,但許多PCIe Gen5(或 PCIe 5.0)設(shè)備也支持在PCIe或 CXL兩種模式下運(yùn)行。類似于 AMD EPYC(霄龍)CPU可以將其 I/O通道作為 PCIe或 Infinity Fabric 運(yùn)行。這不是特定于某個(gè)供應(yīng)商的實(shí)現(xiàn),而是一個(gè)廣泛的行業(yè)標(biāo)準(zhǔn)。CXL的主要優(yōu)勢(shì)是它允許不同終端上的內(nèi)存直接支持Load/Store,這就是我們接下來要介紹的內(nèi)容。

我們將在這里重點(diǎn)關(guān)注內(nèi)存。內(nèi)存是實(shí)現(xiàn)這一目標(biāo)的關(guān)鍵驅(qū)動(dòng)因素,因?yàn)槌笠?guī)模生產(chǎn)商意識(shí)到,幾乎每個(gè)設(shè)備都有板載內(nèi)存,而內(nèi)存成本很高,但利用率經(jīng)常很低。在更高的層次上,CXL 是系統(tǒng)在多個(gè)設(shè)備之間有效共享和利用內(nèi)存的工具。我們今天討論的主要是服務(wù)器,但CXL也可以應(yīng)用于服務(wù)器之外的領(lǐng)域。

為什么PCIe Gen3/Gen4 不使用CXL?

首先是時(shí)間。 CXL 從推出到 2019 年采用, 2021 年末和 2022 年初確實(shí)是我們希望看到的支持CXL的第一代芯片。不過,另外一個(gè)關(guān)鍵的因素是 PCIe Gen5 的迅速普及。整個(gè)行業(yè)從PCIe Gen3過渡到 Gen4花了大約七年的時(shí)間。PCIe Gen5 普及發(fā)生在Gen4 之后大約 3 年。Gen5把 PCIe Gen4帶寬翻倍了。由于 CXL位于 PCIe Gen5 之上,所以我們通常會(huì)看到 32GT/s x16的控制器,但CXL 也可以支持x8 和 x4。在所謂的“降級(jí)”模式下,有一些模式可以進(jìn)入 x2和 x1。重要的是,PCIe Gen5 x4 鏈路有足夠的帶寬來處理 100GbE 鏈路,因此可見低配下仍然有很大的帶寬,類似于英特爾在2021 年第一季度用PCIe Gen3 x16作為高端互聯(lián)的解決方案。

還有,額外的帶寬意味著PCIe將有足夠的能力來處理一類新的應(yīng)用,特別是那些涉及遠(yuǎn)程內(nèi)存加載/存儲(chǔ)的場(chǎng)景,而前幾代PCIe的處理速度不夠快。

所以,總結(jié)來看,為什么CXL沒有早點(diǎn)出來的原因有三。

首先,我們需要 配合PCIe Gen5 的發(fā)展時(shí)間。

其次,我們需要?jiǎng)?chuàng)建 CXL。

第三,行業(yè)采用需要時(shí)間。

現(xiàn)在萬事俱備,CXL 就是未來。

Compute Express Link 協(xié)議三部曲

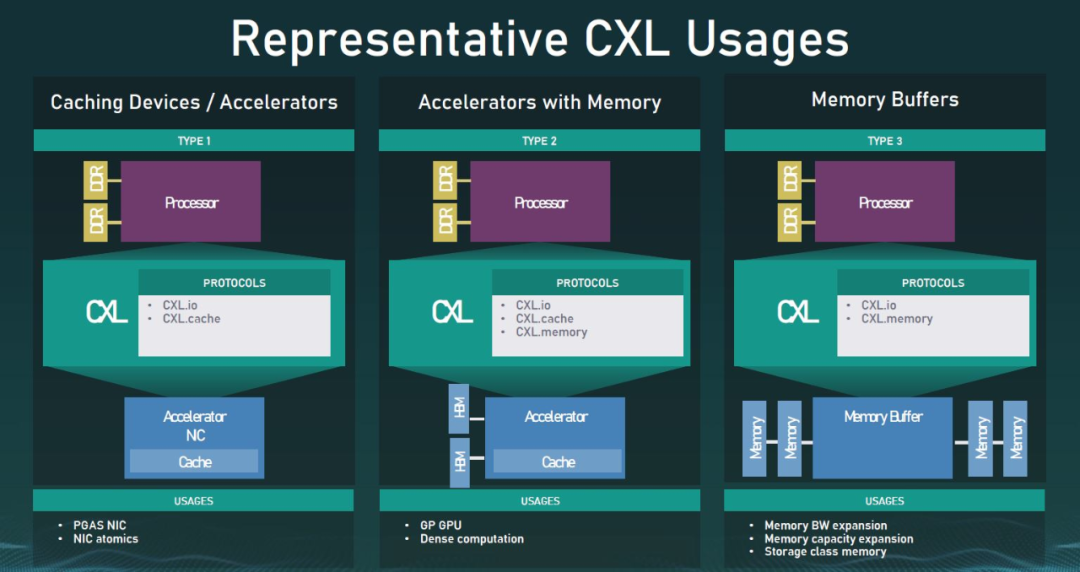

CXL 使用三個(gè)主要協(xié)議:

CXL.io 是用于初始化、鏈接、偵測(cè)設(shè)備和枚舉以及注冊(cè)訪問的協(xié)議。它為I/O 設(shè)備提供了一個(gè)非連貫的加載/存儲(chǔ)接口,類似于 PCIe Gen5。CXL 設(shè)備也必須支持 CXL.io。

CXL.cache 是定義主機(jī)(通常是 CPU)和設(shè)備(例如CXL內(nèi)存模塊或加速器)之間交互的協(xié)議。這允許 CXL 設(shè)備以低延遲訪問緩存在主機(jī)內(nèi)存的數(shù)據(jù)。可以將其理解為為 GPU直接緩存數(shù)據(jù)在 CPU的內(nèi)存中。

CXL.memory / CXL.mem 是為主機(jī)處理器(通常是 CPU)提供使用加載/存儲(chǔ)命令直接訪問設(shè)備內(nèi)存的協(xié)議。將其理解 CPU可以直接使用 GPU或加速器上的內(nèi)存。

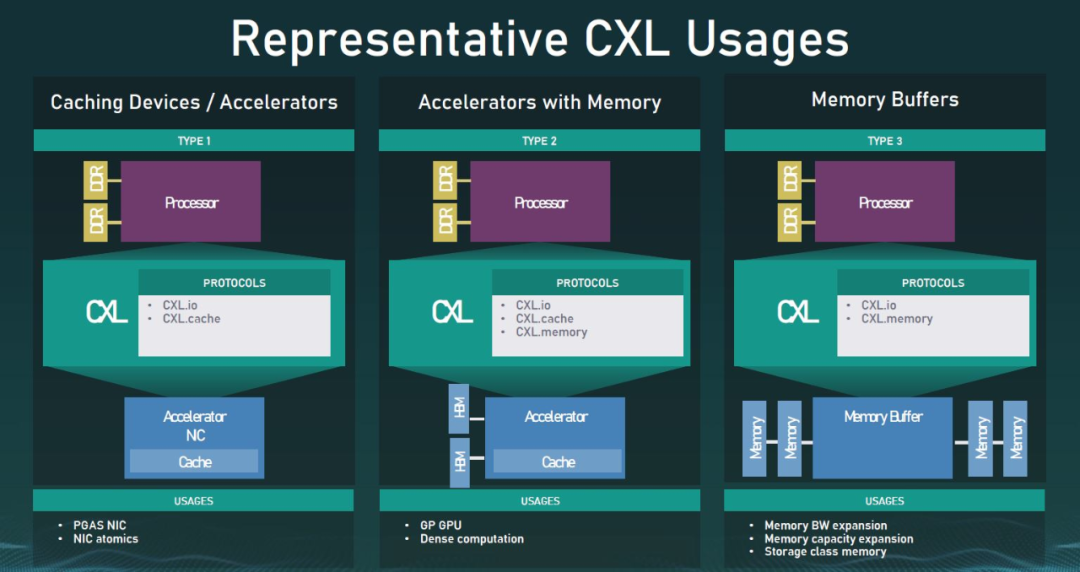

CXL.io 是 CXL中必需的,可以和 CXL.cache或CXL.mem 任意組合。比如 Type 1 (CXL.io + CXL.cache)、Type 2(所有三個(gè))和 Type 3 (CXL.io + CXL.mem)。

CXL 1.0 和 1.1 用法

Type 1 可以將其視為直接訪問主機(jī)CPU內(nèi)存的加速器,比如NIC。Type 2 是我們有一個(gè)加速器的情況,比如有內(nèi)存的 GPU,GPU 可以訪問主機(jī)內(nèi)存,而主機(jī) CPU 可以訪問 GPU 內(nèi)存。可以將類型 3 視為一種內(nèi)存模塊,其主要目的是將 CXL 內(nèi)存設(shè)備的內(nèi)容暴露給主機(jī) CPU。 CXL 1.1 與 2.0

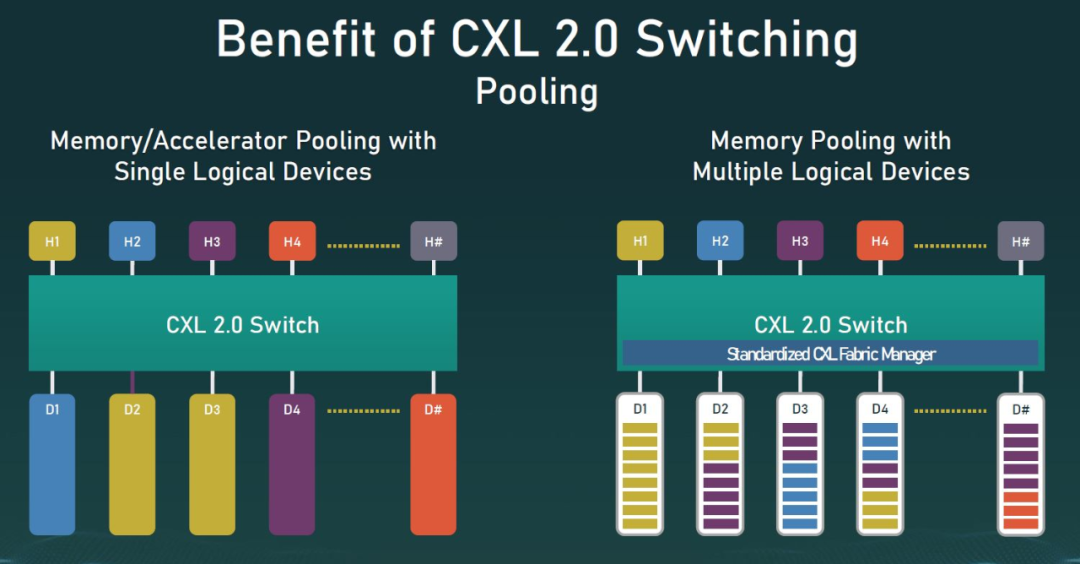

我們將在2022 年初看到大多數(shù)的設(shè)備將使用CXL 1.1。這些仍然主要是主機(jī) CPU管理的, CXL只用于現(xiàn)有的系統(tǒng)中。CXL 2.0 是真正有意思的東西。使用 CXL2.0,我們可以進(jìn)行 CXL 切換。CXL的 交換和池等機(jī)制,允許將多個(gè)主機(jī)和多個(gè)設(shè)備連接到一個(gè)交換機(jī),然后設(shè)備既可以作為完整設(shè)備,又可以作為邏輯設(shè)備分配給不同的主機(jī)。從CXL 2.0開始我們將看到游戲規(guī)則的改變。

CXL 2.0交換池

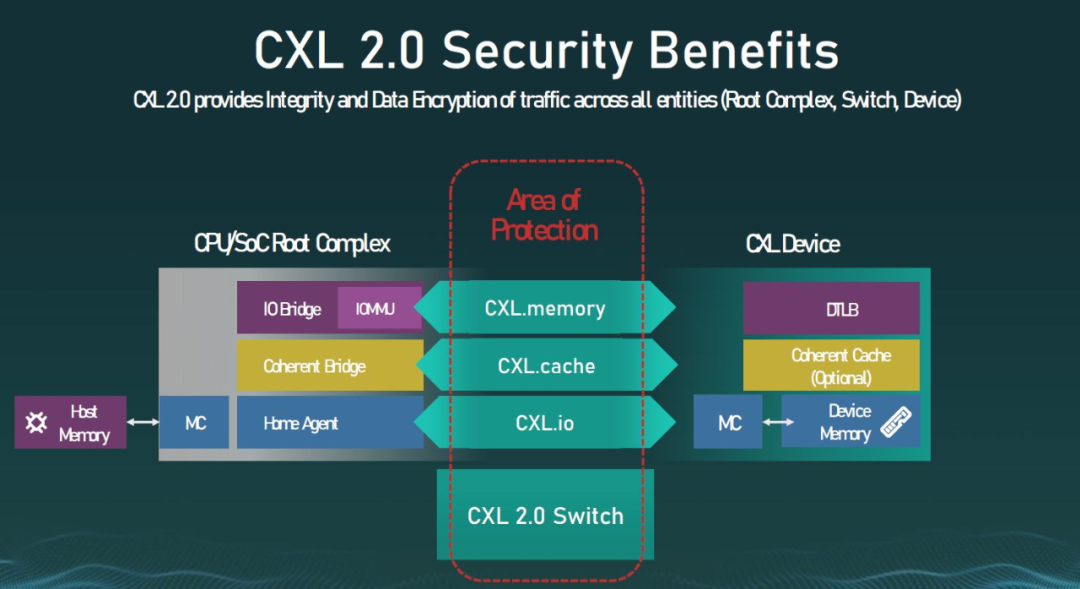

除了 CXL 2.0 交換和池化機(jī)制之外,我們還為協(xié)議添加了額外的安全層。

CXL 2.0安全性雖然 CXL 1.0/ 1.1 將是啟動(dòng)該計(jì)劃的重要版本,但 CXL 2.0 是我們真正想要的。這主要是因?yàn)槲覀冮_始改變服務(wù)器架構(gòu)和部署的方式。CXL 1.1 是必要的,并且有一些應(yīng)用場(chǎng)景,尤其是加速器和 GPU。不過,CXL 2.0 ,我們希望擁有足夠成熟的軟件以永遠(yuǎn)改變服務(wù)器的設(shè)計(jì)方式。 接下來,我們將討論一些示例,并使用我們的Tacos和Limes來幫助那些在幻燈片上難以想象出 CXL 用處的人。 三個(gè) Compute Express Link (CXL) 示例……使用Tacos和Limes那么讓我們來看看Tacos和Limes用例,以及為什么這些用例很重要。這層次太高,也并不完美,但希望這有助于人們對(duì)一些高級(jí)概念有形象化的理解。

CXL 1.0 和 1.1 用法在我們的示例中,Limes將代表Memory。主機(jī)部分將由Rubio的Blackened Mahi Mahi Tacos代表,加速器將由beverage(飲料)代表。

CXL Taco 和 Lime 示例:兩個(gè) Tacos盤的石灰蘇打水

在我們的第一個(gè)示例中,也許我們?cè)趦蓚€(gè) Rubio 熏黑的Mahi Mahi Tacos上收到了一個(gè)Limes。

CXL Taco 和 Lime 示例:兩個(gè) Tacos 一個(gè) Lime 一個(gè) Soda

這并不少見。大多數(shù)體驗(yàn)過盧比奧炸玉米餅的人都經(jīng)歷過一次“不足”的事件。事實(shí)上,即使是貼在商店櫥窗上的廣告也表明,一個(gè)酸橙配三個(gè)炸玉米餅可能會(huì)發(fā)生這種情況。

Rubios 商店櫥窗廣告 3 Tacos 1 Lime

這顯示了配置內(nèi)存(石灰)的資源效率低下。我們的第一個(gè)示例雖然討論了一個(gè)可能的操作。也許今天不是酸橙炸玉米餅日,而是酸橙飲料日。在這里,我們可以從主機(jī)處理器(玉米餅)訪問酸橙汁(內(nèi)存)并將其用于我們的飲料。這就是 CXL.cache 和 Type 1 設(shè)備示例背后的想法。

通過 CXL.cache Beverage 訪問 CXL Lime

在我們的第二個(gè)示例中,我們的處理器(炸玉米餅)來自 Rubios,兩個(gè)炸玉米餅只有一個(gè)酸橙。這是主機(jī)處理器內(nèi)存不足的示例。我們可以利用中心的酸橙盤中的酸橙汁(CXL內(nèi)存擴(kuò)展模塊)。這是 CXL.mem和 Type 3 設(shè)備的一個(gè)示例。

CXL Taco 和石灰示例板的石灰

理論上,尤其是當(dāng)我們有交換和池化的 CXL 2.0 后,我們?cè)L問的內(nèi)存不必是 DDR5。我們可以(理論上)使用英特爾傲騰、GDDR6X 或其他技術(shù)等SCM的 CXL設(shè)備。不同配置成本不同,應(yīng)用也不同,但這就是CXL如此重要的原因。

CXL 玉米卷和酸橙玉米卷與柑橘品種 2

在這個(gè)用例中,我們可以擁有多種類型的內(nèi)存,將它們附加到單個(gè)系統(tǒng),然后訪問整個(gè)內(nèi)存設(shè)備,或者將設(shè)備的一部分用于不同的目的。CXL 2.0 具有熱插拔功能。我們已經(jīng)知道用于此用例的設(shè)備已經(jīng)出現(xiàn),所以我們認(rèn)為熱拔插將非常重要。它還允許比傳統(tǒng)DIMM 外形尺寸更大容量更大的系統(tǒng)內(nèi)存。 在我們的第三個(gè)示例中,讓我們更瘋狂一點(diǎn),假設(shè)我們想在炸玉米餅(處理器)上使用我們飲料中的酸橙(加速器,如 GPU),并在我們的飲料中使用炸玉米餅中的一些酸橙汁。這是 Type-2 設(shè)備的示例。

CXL Taco 和Lime 示例 許多炸玉米餅 許多蘇打水 柑橘品種

同樣,事情開始變得真正有趣的地方是,比如說,我們想要 3D XPoint/英特爾傲騰持久內(nèi)存或存儲(chǔ)類內(nèi)存 (SCM),而不是我們的標(biāo)準(zhǔn) DDR5 內(nèi)存。我們可以將 SCM媒體(檸檬)打包到看起來像我們用于酸橙的東西,現(xiàn)在可以使用檸檬而不是酸橙或檸檬和酸橙的混合物的 Type-3 設(shè)備。在 CXL 2.0世界中,GPU和 CPU不再需要各自的 SCM,而是都可以訪問 SCM 甚至是其它連接的大型內(nèi)存池。 雖然這不是一個(gè)完美的例子,但希望上面的照片有助于說明CXL的發(fā)展方向。就像在虛擬化中一樣,GPU 訪問主機(jī)系統(tǒng)或 Type-3連接設(shè)備內(nèi)存的能力,意味著我們可以更有效地利用資源和系統(tǒng)設(shè)計(jì)。我們不需要具有與主機(jī) CPU 分開的 Optane 內(nèi)存的 GPU/AI 加速器。那將是成本高昂且不靈活的。CXL 為系統(tǒng)增加了這種靈活性。CXL 有助于控制成本,同時(shí)還增加了架構(gòu)的靈活性,這類似于幾年前虛擬化帶來的好處。 加強(qiáng)版示例 供應(yīng)很重要,有效的資源利用也很重要,但讓我們更進(jìn)一步,想象一下這將如何改變架構(gòu)。盡管它們?cè)诋?dāng)今的大規(guī)模部署中不太常見,但許多企業(yè)仍在使用硬件 RAID 控制器。

Broadcom 9500 RAID 控制器

這些通常使用一些關(guān)鍵組件和功能進(jìn)行操作: · 有一個(gè) SoC 控制數(shù)據(jù)移動(dòng)、奇偶校驗(yàn)計(jì)算、緩存和存儲(chǔ)/檢索。· 板載 DRAM 用作寫入緩存,通常用作小型讀取緩存。· 電池/電容器 FRU 允許寫入緩存發(fā)生在板載 DRAM中,即使斷電也能安全刷新。· 用于板載 DRAM 的閃存存儲(chǔ),以在斷電時(shí)刷新。· 用于管理磁盤的存儲(chǔ)控制器。· SSD 用于主存儲(chǔ)或作為連接到 RAID控制器的緩存設(shè)備進(jìn)行管理。· 通常,這些 SSD 在每個(gè)設(shè)備上都有自己的斷電保護(hù)寫入緩存。現(xiàn)在,想象一下未來會(huì)怎樣。DRAM-less NAND SSD 和硬盤驅(qū)動(dòng)器在更高級(jí)別進(jìn)行管理。這可以為每個(gè) SSD移除幾 GB的 NAND。我們可以使用基于 CXL的 SCM(例如 Optane Persistent Memory)并直接寫入該設(shè)備,而不是 NAND SSD和 RAID控制器上的斷電保護(hù)以及閃存寫入斷電刷新事件數(shù)據(jù)作為系統(tǒng)的寫緩存。然后,諸如 DPU 之類的協(xié)處理器可以管理將緩存從 SCM 寫入本地或網(wǎng)絡(luò)存儲(chǔ)的刷新。RAID 卡上的緩存不是幾 GB 可能是 1TB 的主機(jī)內(nèi)存(盡管這基本上不需要,因?yàn)槲覀冇?CXL)或CXL DDR5,可以由主機(jī)處理器直接訪問,而不是通過 RAID控制器。 這種應(yīng)用場(chǎng)景給我們的啟發(fā)是,如何用服務(wù)器中更高性能的本地資源替換傳統(tǒng)存儲(chǔ)陣列并使用橫向擴(kuò)展存儲(chǔ)?這對(duì)行業(yè)來說絕對(duì)是變革性的,這只是我們聽到的幾家公司正在努力的一個(gè)例子。通常,這些應(yīng)用場(chǎng)景包含更大、更多樣化的內(nèi)存池和 GPU/AI 等加速器,所以我給了一些不同的示例來說明為什么CXL 可以輕松應(yīng)付這些個(gè)不同的場(chǎng)景。

最后的話

CXL 的關(guān)鍵在于,隨著 CXL的普遍采用,服務(wù)器架構(gòu)的嚴(yán)格限制將開始消失。這非常重要,因?yàn)殡S著服務(wù)器不斷擴(kuò)大,這意味著資源得到了更有效的利用。幾年后,我們回顧今天的服務(wù)器,就會(huì)認(rèn)為它們是一種傳統(tǒng)的運(yùn)營(yíng)模式,就像我們?yōu)樘摂M化之后的許多應(yīng)用程序(以及后來的容器)所做的專用服務(wù)器一樣。多年以來,這些東西已經(jīng)被討論過很多次,但我們實(shí)際上是在Astera Labs Aries CXL Retimers之外的產(chǎn)品中實(shí)施不到一年。

CXL Taco 和Lime示例 許多炸玉米餅 許多蘇打水 柑橘品種

希望本指南可以幫助您了解 CXL 是什么以及它通常要完成的工作。CXL在技術(shù)深度方面還有很多,但我們想確保我們的讀者先有一個(gè)基本的理解。Tacos和 Lime并不完美,但多年來我們一直在研究相同的圖表,但仍有人不知道 CXL 的影響。我們談?wù)摰氖荘CIe Gen5時(shí)代早期的CXL,但我們也有有一個(gè)到PCIe Gen6 及以后的路線圖。我們已經(jīng)討論了一些關(guān)于此模型如何擴(kuò)展到諸如 Gen-Z 之類的結(jié)構(gòu),以使用某種類似的解決方案實(shí)現(xiàn)更大規(guī)模部署。 當(dāng)然,我們將來會(huì)有更多關(guān)于 CXL 的內(nèi)容,但我們想先給大家說一下CXL 是啥以及其他一些關(guān)于CXL的初級(jí)內(nèi)容。

原文標(biāo)題:CXL:為緩存一致性而生的新一代總線

文章出處:【微信公眾號(hào):Linux閱碼場(chǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

審核編輯:湯梓紅

-

控制器

+關(guān)注

關(guān)注

112文章

16445瀏覽量

179444 -

cpu

+關(guān)注

關(guān)注

68文章

10902瀏覽量

213001 -

總線

+關(guān)注

關(guān)注

10文章

2903瀏覽量

88387

原文標(biāo)題:CXL:為緩存一致性而生的新一代總線

文章出處:【微信號(hào):LinuxDev,微信公眾號(hào):Linux閱碼場(chǎng)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

用于 PCIe Gen-3 卡的高速前端參考設(shè)計(jì)

PCIe GEN3 ECRC僅在離線模式下出錯(cuò)

為什么在我的PCIe Gen3插槽上使用VC709不起作用?

請(qǐng)問XC7K325T-2FFG900支持PCIE PHY GEN3嗎?

符合PCIe Gen1,Gen2和Gen3標(biāo)準(zhǔn)的9端口PCIe時(shí)鐘發(fā)生器

PCIe Gen-3高速前端卡參考設(shè)計(jì)

Layerscape MPU中是否有支持PCIe GEN3 16通道的EVB?

Altera率先實(shí)現(xiàn)Stratix V GX FPGA與PCIe Gen3交換機(jī)互操作

邁威科技PCIe Gen4 NVMe SSD控制器面世!推進(jìn)下一代技術(shù)發(fā)展

西部數(shù)據(jù)推出高性能、輕薄低功耗的PCIe Gen4 NVMe SSD

克服向PCIe Gen3遷移的SoC設(shè)計(jì)挑戰(zhàn)

為什么USB4 Gen4采用 PAM3?

天璣9400性能將超越驍龍8 Gen4?

Xilinx 7系列FPGA PCIe Gen3的應(yīng)用接口及特性

為什么PCIe Gen3/Gen4不使用CXL

為什么PCIe Gen3/Gen4不使用CXL

評(píng)論