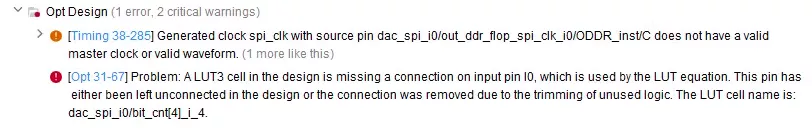

在Vivado中,可能由于某些邏輯輸入懸空而導致Implementation的opt_design時會錯,比如:

報的錯誤是dac_spi_i0/bit_cnt[4]_i_4的這個LUT有個輸入懸空了,這個工程的邏輯比較簡單,例化的嵌套也比較少,因此在schematic一層層找也很容易可以找到,但如果工程比較復雜,在很內部的一個LUT的輸入懸空了,找起來就很費勁了。

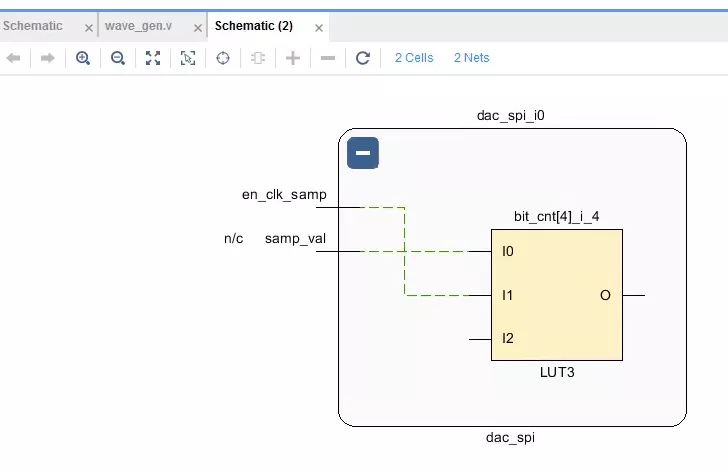

筆者碰到的問題是在vivado的axi-interconnect ip中報了這個錯誤,而且是ip內部套了好幾層的地方,如果再一層層往下找就比較麻煩了,不過vivado提供了tcl指令可以幫我們快速找到這個LUT在schematic中的位置:

show_schematic [get_cells dac_spi_i0/bit_cnt[4]_i_4]

就會快速定位到schematic中的位置:

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

指令

+關注

關注

1文章

611瀏覽量

35811 -

邏輯

+關注

關注

2文章

833瀏覽量

29515 -

Vivado

+關注

關注

19文章

815瀏覽量

66883

發布評論請先 登錄

相關推薦

詳解Object Detection Demo的移植

繼上一篇移植了 Mediapipe 的 LLM Inference 后,這篇文章我們將繼續探索 Object Detection Demo 的移植。

電腦相片云存儲位置,如何快速找到電腦相片云存儲位置

在數字化時代,傳統的電腦已經無法滿足我們對高效、便捷計算的需求。云電腦以其強大的功能和靈活的使用方式,成為了新時代的寵兒。今天就為大家介紹如何快速找到電腦相片云存儲位置。 ? ?在現代辦公和生活中

Vivado Design Suite用戶指南:邏輯仿真

電子發燒友網站提供《Vivado Design Suite用戶指南:邏輯仿真.pdf》資料免費下載

發表于 01-15 15:25

?0次下載

Xilinx_Vivado_SDK的安裝教程

I Agree,然后點擊 Next: 選擇 Vivado HL System Edition(一般選擇這個設計套件比較完整,它比 Vivado HL Design Edition 多了一個 System Generator for DSP with Mat

每次Vivado編譯的結果都一樣嗎

很多FPGA工程師都有這種困惑,Vivado每次編譯的結果都一樣嗎? 在AMD官網上,有這樣一個帖子: Are Vivado results repeatable for identical

Vivado使用小技巧

有時我們對時序約束進行了一些調整,希望能夠快速看到對應的時序報告,而又不希望重新布局布線。這時,我們可以打開布線后的dcp,直接在Vivado Tcl Console里輸入更新后的時序約束。如果調整

TPA3118D2EVM Schematic中輸出電感可用FB1812(貼片磁珠),貼片磁珠的參數規格型號和怎樣選?

TPA3118D2EVM Schematic中輸出電感可用FB1812(貼片磁珠),貼片磁珠的參數規格型號和怎樣選

請高手或TI工程師幫忙指教

發表于 10-18 06:17

Vivado 使用Simulink設計FIR濾波器

。

使用vivado的System Generator可以在simulink下快速的通過matlab的強大設計功能設計濾波器。這里使用fdatool設計了一個15階的FIR濾波器。

軟件環境

發表于 04-17 17:29

Vivado怎么快速找到schematic中的object

Vivado怎么快速找到schematic中的object

評論