Integrity 3D-IC 是 Cadence 新一代多芯片設計解決方案,它將硅和封裝的規劃和實現,與系統分析和簽核結合起來,以實現系統級驅動的 PPA 優化。

原生 3D 分區流程可自動智能創建邏輯內存器件的 3D 堆疊配置,優化 3D 堆疊設計的 PPA 結果。

客戶可以放心采用 Cadence Integrity 3D-IC 平臺和 Samsung Foundry 的多 Die 實現流程,打造新一代超大規模計算、移動、汽車和人工智能應用。

中國上海,2021 年 11 月 18 日——楷登電子(美國 Cadence 公司,NASDAQ:CDNS),作為 Samsung Advanced Foundry Ecosystem(SAFE)的緊密合作伙伴,Cadence 公司于宣布,Samsung Foundry 已經對 Cadence Integrity 3D-IC 平臺的 2D-to-3D 原生 3D 分區流程進行了工藝認證。

利用新流程,客戶可以將現有的 2D 設計分割成 3D 邏輯內存器件(Memory-on-logic)配置,與原來的 2D 設計相比,可以通過同構 3D 堆疊獲得更好的功耗、性能和面積(PPA)結果。該流程還為分區設計提供了強大的 3D-IC 系統規劃、實現和早期分析能力,是客戶打造復雜的新一代超大規模計算、移動、汽車和人工智能應用的理想選擇。

由于內存墻限制,RAM 的訪問速度跟不上 CPU 的執行速度,導致整個系統因內存延遲而變慢。克服這個問題的方法之一是采用同構的堆疊配置,并將存儲器放在邏輯之上。這種配置安裝在同一封裝中時,可以減少導線長度和面積,加快內存訪問速度,因此有助于提高 CPU 核心的性能。

Integrity 3D-IC 平臺的 3D 分區功能使用戶能夠分離出內存宏和標準單元,并將它們放置在 3D 同構堆疊內的兩個不同裸片上。自動流程在宏和標準單元之間建立連接的同時,進行 3D 堆棧的分區和完整實現。最終確定每個裸片的內容之后,系統和封裝就可以在 Integrity 3D-IC 平臺上實現,進行凸點規劃、實現、與其他裸片的協同設計,以及熱、功耗和靜態時序分析(STA)的早期分析。

“對于在 3D-IC 配置方面具有不同自動化分區要求的客戶,可以利用 Samsung Foundry MDI 參考流程的這種獨特功能來探索芯片堆疊的效果,該流程基于 Cadence 新款 Integrity 3D-IC 平臺中的原生 3D 分區功能。”Samsung Electronics 工藝設計技術副總裁 Sangyun Kim 表示,“Cadence 和 Samsung 之間的這種成功合作為客戶提供了 3D 堆疊設計的分區、實現和分析流程,使他們能夠減小功耗和面積,同時提高整體系統性能。”

“通過與 Samsung Foundry 的持續合作,我們在多裸片設計實現領域進行了合作創新,并提供了自動化的原生 3D 分區流程。”Cadence 公司數字與簽核事業部產品工程副總裁 Vivek Mishra 表示,“Samsung Foundry 用于多裸片設計實現的先進封裝技術,結合 Cadence 集成化的 Integrity 3D-IC 平臺,為我們的共同客戶提供了強大的多裸片解決方案。”

Integrity 3D-IC 平臺為客戶提供了通用的控制面板和數據庫、完整的規劃系統、無縫集成的設計實現工具、集成化的系統級分析能力和易于使用的界面,并允許用戶使用 Virtuoso Design Environment 和 Allegro 封裝技術實現協同設計。該平臺還包括更廣泛的 Cadence 3D-IC 解決方案組合,包括用于電源分配網絡(PDN)分析的 Voltus IC Power Integrity Solution、用于 3D 熱分析的 Celsius Thermal Solver、用于 3D 簽核時序的 Tempus Timing Signoff Solution 和用于電路布局驗證(LVS)的 Pegasus Verification System。

責任編輯:haq

-

3D

+關注

關注

9文章

2911瀏覽量

108008 -

驅動

+關注

關注

12文章

1851瀏覽量

85644 -

Cadence

+關注

關注

65文章

930瀏覽量

142456

原文標題:Cadence Integrity 3D-IC平臺通過Samsung Foundry 5LPE工藝設計堆疊的原生3D分區流程認證

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

Cadence宣布收購Secure-IC

Cadence收購Secure-IC強化嵌入式安全布局

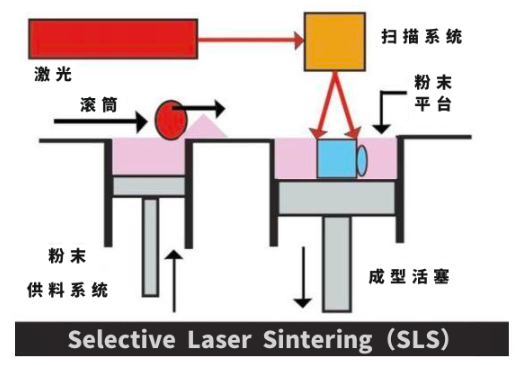

物聯網行業中3D打印工藝——SLS(選擇性激光燒結)工藝

Cadence與Samsung Foundry開展廣泛合作

剖析 Chiplet 時代的布局規劃演進

Samsung 和Cadence在3D-IC熱管理方面展開突破性合作

西門子推出Innovator3D IC,用于 3D IC 設計、驗證和制造的多物理場集成環境

Cadence與Intel Foundry的戰略合作取得重大成果

借助云計算加速3D-IC可靠性的機械應力模擬

Cadence與臺積電深化合作創新,以推動系統和半導體設計轉型

積木易搭通過亞馬遜SPN服務商認證,成為平臺指定3D商品展示服務商

3D-IC 以及傳熱模型的重要性

Cadence Integrity 3D-IC平臺進行工藝認證

Cadence Integrity 3D-IC平臺進行工藝認證

評論