隨著全球能源需求和能耗的增加以及對(duì)綠色能源的推動(dòng)加強(qiáng),許多公用事業(yè)公司正在改變他們的戰(zhàn)略。這些公司并沒有增加發(fā)電量,而是通過提高交付給客戶的電能質(zhì)量來提高輸配電效率,從而使電力系統(tǒng)具有容錯(cuò)性。同時(shí)通過增強(qiáng)保護(hù)、監(jiān)控、控制和自動(dòng)化,延長設(shè)備的使用壽命,最大限度地減少停機(jī)時(shí)間并降低運(yùn)營費(fèi)用。

從傳統(tǒng)變電站轉(zhuǎn)向智能變電站

通過閱讀我們的最新版白皮書,“從傳統(tǒng)變電站轉(zhuǎn)向智能變電站”,了解有關(guān)智能變電站的更多信息。

例如,具有容錯(cuò)性的電力系統(tǒng)減少了可用的故障電流,并通過與二級(jí)保護(hù)設(shè)備連接的傳感器和通信來實(shí)現(xiàn)設(shè)備的智能化。這些設(shè)備能夠準(zhǔn)確地檢測(cè)故障電流并縮短故障清除時(shí)間,進(jìn)行遠(yuǎn)程操作,準(zhǔn)確、快速地確定故障位置,從而最大限度地減少停機(jī)時(shí)間和降低供電恢復(fù)時(shí)間,并在數(shù)據(jù)分析中引入冗余來提高可靠性,從而做到提前預(yù)測(cè)和預(yù)防設(shè)備故障。一次設(shè)備,如輸電線路、電力變壓器(見圖1)、斷路器和負(fù)載開關(guān)等,在維護(hù)電力系統(tǒng)完整性和供電可用性方面發(fā)揮著重要作用。

所使用的高端二次設(shè)備包括帶AC模擬輸入模塊的保護(hù)繼電器和終端單元,如遠(yuǎn)程終端單元、配電終端單元、饋線終端單元、相量測(cè)量單元等,用于一次設(shè)備的保護(hù)、控制、測(cè)量和電能分析。公用事業(yè)公司也正在實(shí)施和改進(jìn)多種保護(hù)算法和診斷方案,以保護(hù)資產(chǎn)和電網(wǎng),并盡早預(yù)測(cè)故障。

大多數(shù)連接的傳感器可以提供與其測(cè)量的參數(shù)(電壓、電流和/或溫度)成比例的模擬輸出。為了獲取連接到一次設(shè)備的不同傳感器的模擬輸出,越來越需要在數(shù)據(jù)采集(DAQ)系統(tǒng)上擴(kuò)展模擬輸入通道。DAQ是精確測(cè)量和處理如電壓、電流和溫度等電氣輸入的過程,能夠選擇采樣率并使用集成信號(hào)處理器實(shí)時(shí)計(jì)算被測(cè)參數(shù)。

高性能DAQ系統(tǒng)的一些關(guān)鍵要求包括:

使用多個(gè)模數(shù)轉(zhuǎn)換器(ADC)(2個(gè)或2個(gè)以上)來采樣多個(gè)傳感器(4,8,16個(gè)或以上)的模擬輸入,以實(shí)現(xiàn)多通道采集和冗余。

使用16位或以上的精度逐次逼近寄存器(SAR)或Δ-Σ ADC來準(zhǔn)確測(cè)量電氣參數(shù)。

依照國際電工委員會(huì)(IEC)61850-9-2(用于保護(hù)的80個(gè)樣品,用于測(cè)量的256個(gè)樣品),能夠改變基于測(cè)量或保護(hù)的采樣率,同時(shí)對(duì)輸入進(jìn)行相干采樣,以用不同線路頻率

同時(shí)對(duì)輸入進(jìn)行采樣,以保持電壓和電流的相位角關(guān)系,從而簡化保護(hù)算法,減少跳閘次數(shù)。

將多個(gè)ADC連接到主處理器,以實(shí)時(shí)獲取ADC轉(zhuǎn)換器采樣數(shù)字?jǐn)?shù)據(jù)。

主處理器能夠同時(shí)從多個(gè)ADC中采集樣本并實(shí)時(shí)處理樣本,包括計(jì)算復(fù)雜的電氣參數(shù)。

鑒于系統(tǒng)復(fù)雜性的增加,需要優(yōu)化系統(tǒng)成本。

能夠使用數(shù)字隔離器選擇性地隔離連接至主處理器的ADC接口,以提高系統(tǒng)性能和可靠性。

有多種可用的ADC架構(gòu)。最流行的是SAR或Δ-Σ,并且ACD和主處理器之間的接口是可以并行或串行的。每種主機(jī)接口方法都有其優(yōu)點(diǎn)。在菊花鏈配置中使用串聯(lián)接口是最簡單的解決方案,因?yàn)槟梢詫?duì)ADC進(jìn)行菊花鏈?zhǔn)竭B接,但其弊端是降低了吞吐量。并行接口提供了更高的吞吐量,但限制了ADC的選擇,增加了成本和電路板的復(fù)雜性。

或者,您可以使用具有獨(dú)立可控芯片選擇的多個(gè)串行外圍接口(SPI)端口來實(shí)現(xiàn)更高的吞吐量,同時(shí)保持采樣的靈活性。所需的SPI端口數(shù)量隨著所連接的ADC數(shù)量的增加而增加,但這提高了實(shí)時(shí)處理能力的要求。這限制了主處理器(具有有限的SPI端口和實(shí)時(shí)處理能力)的使用。因此,一些設(shè)計(jì)人員選擇使用具有多個(gè)SPI端口的現(xiàn)場(chǎng)可編程門陣列(FPGA)與ADC進(jìn)行連接,以實(shí)現(xiàn)所需的采樣靈活性和數(shù)據(jù)吞吐量。此架構(gòu)需要一個(gè)用于人機(jī)和通信接口的額外應(yīng)用處理器,然而,這將提升系統(tǒng)的成本和復(fù)雜性。

帶集成外圍設(shè)備的16位SAR ADC,包括一個(gè)可編程增益放大器(PGA),一個(gè)準(zhǔn)確基準(zhǔn),一個(gè)連接至帶有雙核可編程實(shí)時(shí)單元以及工業(yè)通信子系統(tǒng)(PRU-ICSS)簡化DAQ系統(tǒng)設(shè)計(jì)的主處理器SPI串行接口。如TI的采用多個(gè)ADC且適用于同步相干DAQ的靈活接口(PRU-ICSS)參考設(shè)計(jì)所示。主處理器和ADC中增強(qiáng)的功能集成降低了整體系統(tǒng)成本,同時(shí)提高了性能和可靠性。

結(jié)論

當(dāng)您需要將多個(gè)ADC連接到單處理器時(shí),設(shè)備和架構(gòu)的選擇對(duì)于設(shè)計(jì)的成功至關(guān)重要。TI的集成電路和參考設(shè)計(jì)簡化了架構(gòu)選擇和需要16個(gè)或更多精度模擬輸入通道的多通道精度DAQ系統(tǒng)的設(shè)計(jì)。

審核編輯:何安

-

工業(yè)

+關(guān)注

關(guān)注

3文章

1867瀏覽量

46903

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

鴻蒙110kV變電站電氣試驗(yàn)設(shè)備方案

智能變電站難題揭秘:運(yùn)維問題全解析!--安科瑞張?zhí)锾?/a>

箱式變電站的運(yùn)行要求

箱式變電站具有哪些優(yōu)點(diǎn)

變電站RTU技術(shù)解析

變電站的定義與重要性

變電站母線失壓的依據(jù)是什么

變電站無人值守化管理 如何運(yùn)維呢

智能變電站集中監(jiān)控輔助決策系統(tǒng)配置原則

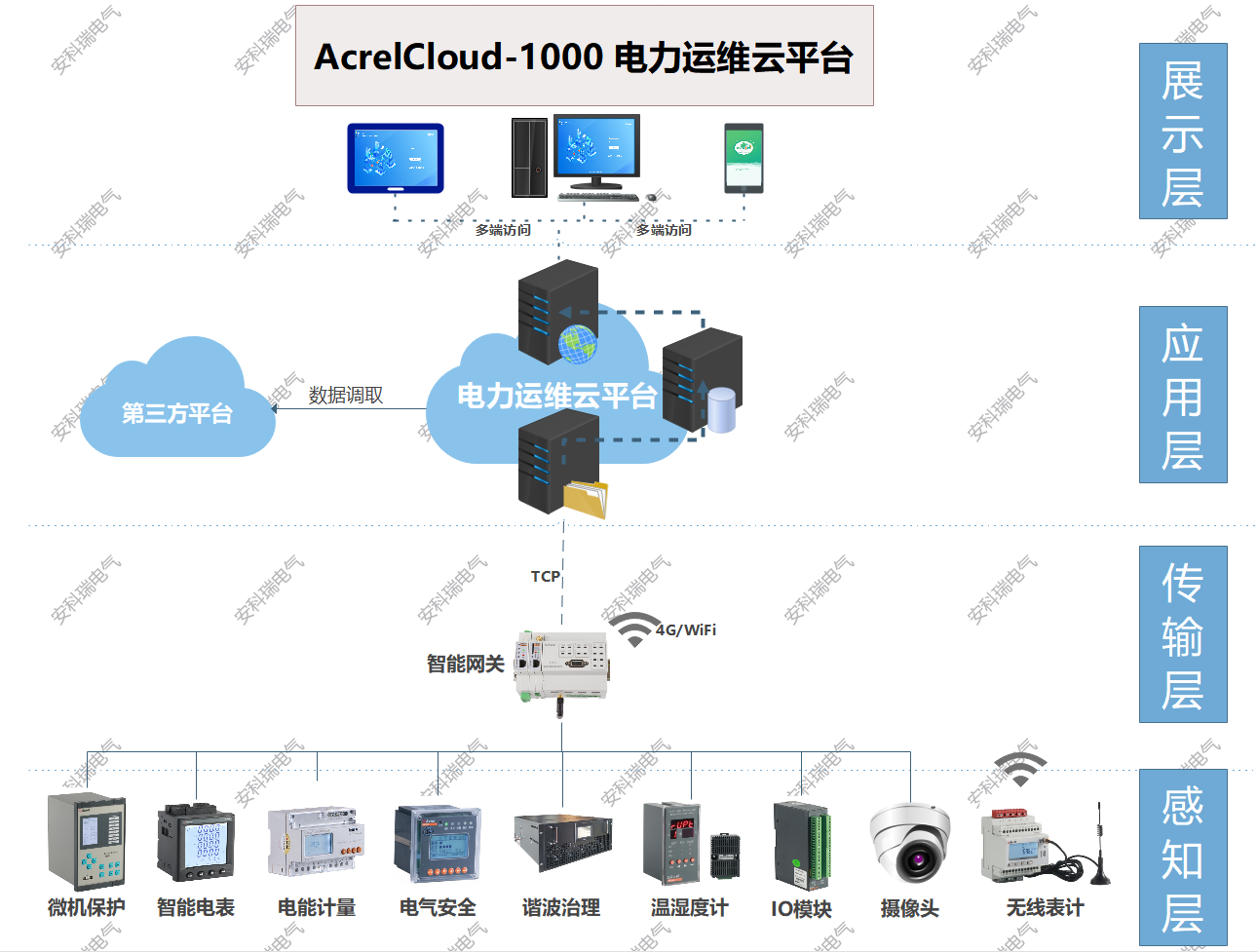

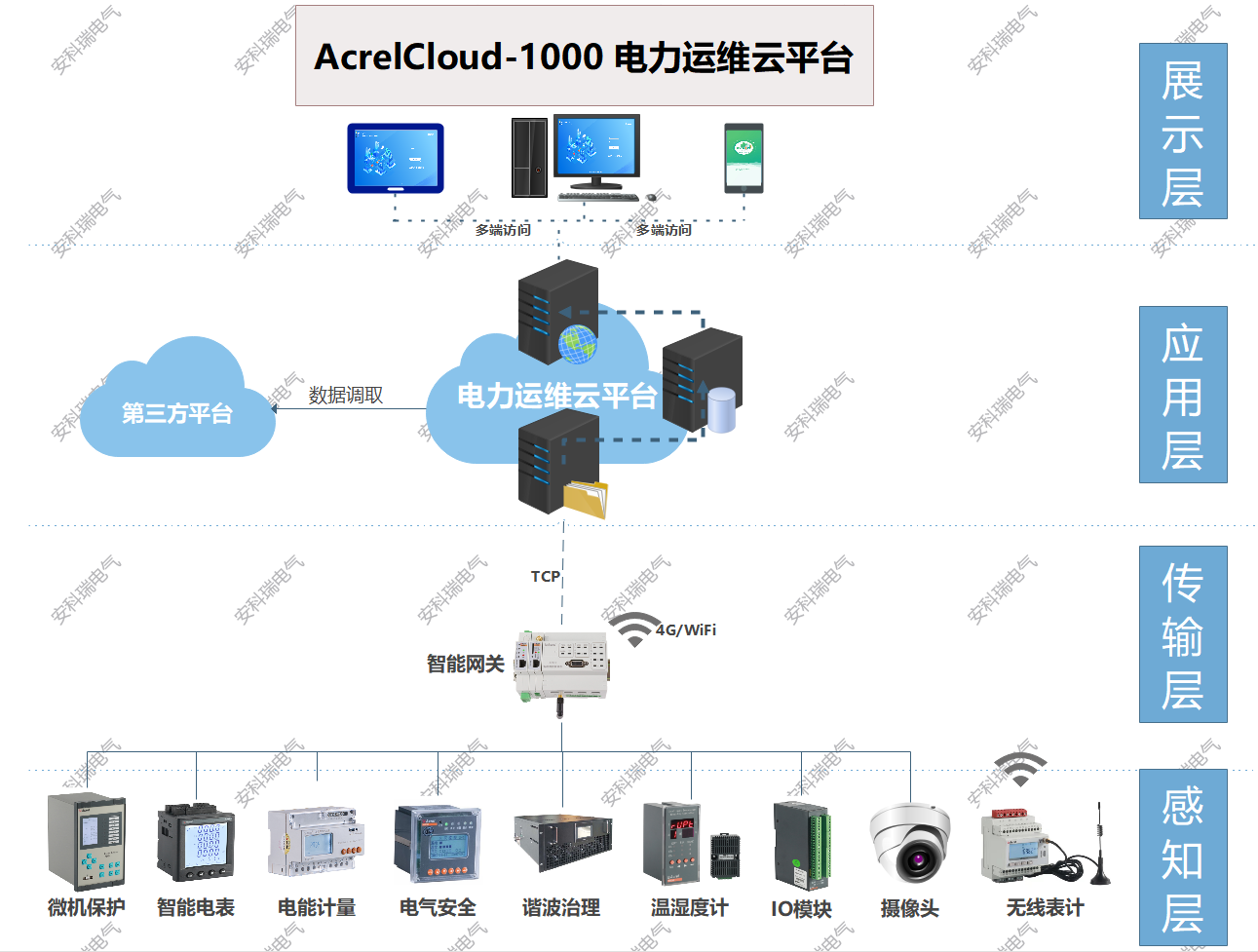

智能變電站遠(yuǎn)程監(jiān)控解決方案

變電站智能巡檢機(jī)器人的應(yīng)用領(lǐng)域?

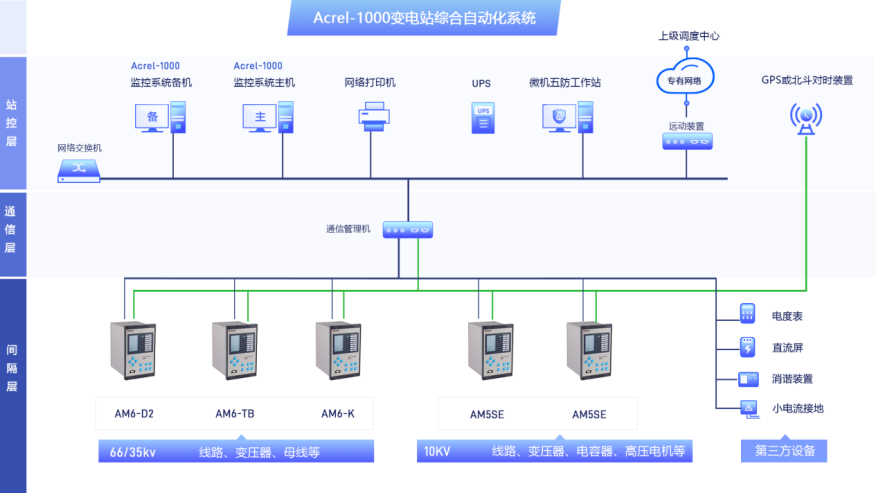

無人值守變電站的發(fā)展與變電站綜合自動(dòng)化系統(tǒng)

淺談智能變電站運(yùn)維管理平臺(tái)的安全與設(shè)備維護(hù)

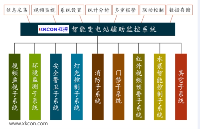

XKCON智能變電站輔助監(jiān)控系統(tǒng)采用模塊化結(jié)構(gòu)設(shè)計(jì)

從傳統(tǒng)變電站到智能變電站

從傳統(tǒng)變電站到智能變電站

評(píng)論