2021年8月30日,中國上海訊——國產EDA行業的領軍企業芯和半導體發布了前所未有的“3DIC先進封裝設計分析全流程”EDA平臺。該平臺聯合了全球EDA排名第一的新思科技,是業界首個用于3DIC多芯片系統設計分析的統一平臺,為客戶構建了一個完全集成、性能卓著且易于使用的環境,提供了從開發、設計、驗證、信號完整性仿真、電源完整性仿真到最終簽核的3DIC全流程解決方案。

隨著芯片制造工藝不斷接近物理極限,芯片的布局設計——異構集成的3DIC先進封裝(以下簡稱“3DIC”)已經成為延續摩爾定律的最佳途徑之一。3DIC將不同工藝制程、不同性質的芯片以三維堆疊的方式整合在一個封裝體內,提供性能、功耗、面積和成本的優勢,能夠為5G移動、HPC、AI、汽車電子等領先應用提供更高水平的集成、更高性能的計算和更多的內存訪問。然而,3DIC作為一個新的領域,之前并沒有成熟的設計分析解決方案,使用傳統的脫節的點工具和流程對設計收斂會帶來巨大的挑戰,而對信號、電源完整性分析的需求也隨著垂直堆疊的芯片而爆發式增長。

芯和半導體此次發布的3DIC先進封裝設計分析全流程EDA平臺,將芯和2.5D/3DIC先進封裝分析方案Metis與新思 3DIC Compiler現有的設計流程無縫結合,突破了傳統封裝技術的極限,能同時支持芯片間幾十萬根數據通道的互聯。該平臺充分發揮了芯和在芯片-Interposer-封裝整個系統級別的協同仿真分析能力;同時,它首創了“速度-平衡-精度”三種仿真模式,幫助工程師在3DIC設計的每一個階段,能根據自己的應用場景選擇最佳的模式,以實現仿真速度和精度的權衡,更快地收斂到最佳解決方案。

芯和半導體聯合創始人、高級副總裁代文亮博士表示:“在3DIC的多芯片環境中,僅僅對單個芯片進行分析已遠遠不夠,需要上升到整個系統層面一起分析。芯和的Metis與新思的 3DIC Compiler的集成,為工程師提供了全面的協同設計和協同分析自動化功能,在設計的每個階段都能使用到靈活和強大的電磁建模仿真分析能力,更好地優化其整體系統的信號完整性和電源完整性。通過減少 3DIC 的設計迭代加快收斂速度,使我們的客戶能夠在封裝設計和異構集成架構設計方面不斷創新。”

關于芯和半導體

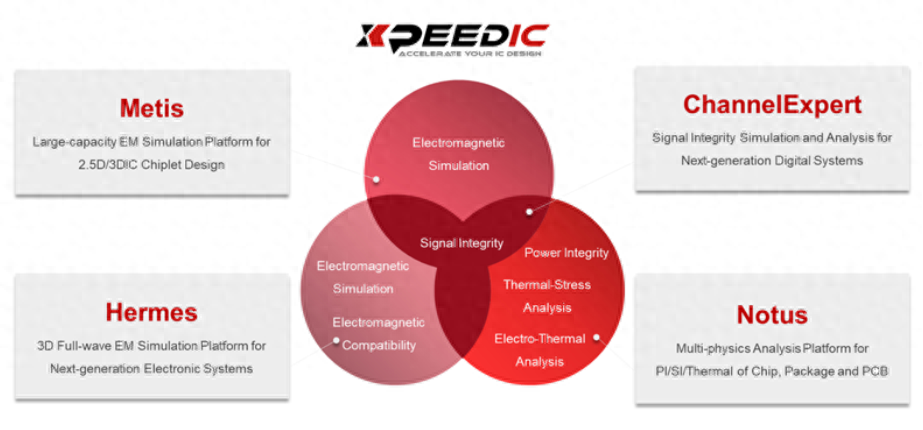

芯和半導體是國產EDA行業的領軍企業,提供覆蓋IC、封裝到系統的全產業鏈仿真EDA解決方案,致力于賦能和加速新一代高速高頻智能電子產品的設計。

芯和半導體自主知識產權的EDA產品和方案在半導體先進工藝節點和先進封裝上不斷得到驗證,并在5G、智能手機、物聯網、人工智能和數據中心等領域得到廣泛應用,有效聯結了各大IC設計公司與制造公司。

芯和半導體同時在全球5G射頻前端供應鏈中扮演重要角色,其通過自主創新的濾波器和系統級封裝設計平臺為手機和物聯網客戶提供射頻前端濾波器和模組,并被Yole評選為全球IPD濾波器領先供應商。

芯和半導體創建于2010年,前身為芯禾科技,運營及研發總部位于上海張江,在蘇州、武漢設有研發分中心,在美國硅谷、北京、深圳、成都、西安設有銷售和技術支持部門。如欲了解更多詳情,敬請訪問www.xpeedic.com。

fqj

-

半導體

+關注

關注

334文章

27714瀏覽量

222666 -

封裝

+關注

關注

127文章

7997瀏覽量

143410

發布評論請先 登錄

相關推薦

新思科技引領EDA產業革新,展望2025年芯片與系統創新之路

半導體行業加速布局先進封裝技術,格芯和臺積電等加大投入

芯和半導體邀您相約IIC Shenzhen 2024峰會

可驗證AI開啟EDA新時代,引領半導體產業變革

芯和半導體聯合新思科技業界首發, 前所未有的“3DIC先進封裝設計分析全流程”EDA平臺

芯和半導體聯合新思科技業界首發, 前所未有的“3DIC先進封裝設計分析全流程”EDA平臺

評論